上篇我們介紹了相關的算法原理以及外設特性,本篇我們將介紹一下基于FPGA的實時圖像邊緣檢測系統的實現方案,算法的Verilog實現以及最終實現的檢測效果。

一、 設計方案

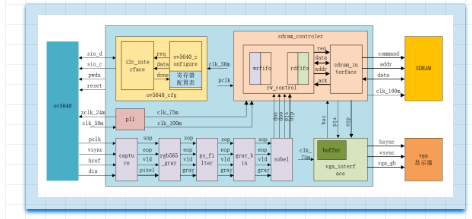

整個系統主要分為以下5個部分:攝像頭傳感器配置部分;圖像數據采集與處理部分;圖像緩存部分;VGA顯示部分;以及PLL時鐘管理部分;如圖1所示。

圖1 系統結構圖

攝像頭傳感器配置部分

按照配置表中的參數,將攝像頭配置為分辨率為1280*720像素點、RGB565數據格式、VGA時序輸出;然后通過I2C協議將參數配置給攝像頭的每個寄存器。

圖像數據采集與處理部分

攝像頭配置完成后,在攝像頭輸出時鐘pclk驅動下,完成圖像數據的采集與處理;圖像采集模塊(capture)對攝像頭輸出的像素數據進行串并轉換,然后給到后續的圖像處理模塊,依次進行灰度轉換(rgb565_gray)、高斯濾波(gs_filter)、二值化處理(gray_bin)、Sobel邊緣檢測(sobel);在進行二值化處理時,直接將灰度圖像二值化為0或1。

圖像緩存部分

主要是SDRAM讀寫控制邏輯(rw_control)與SDRAM接口(sdram_interface);其中,rw_control模塊作為Master向sdram_interface發起突發傳輸請求。主要有以下幾個功能:

跨時鐘域數據緩存;

乒乓緩存控制;

SDRAM讀寫優先級的仲裁以產生讀寫傳輸請求、地址等。

sdram_interface模塊作為Slave執行Master發起的突發傳輸請求,主要是根據接收到讀、寫請求以及數據、地址等,向SDRAM芯片發起各種命令、地址、數據,實現SDRAM的數據存取。

VGA顯示部分

主要是實現1080*720@60分辨率的VGA顯示時序,驅動VGA接口的顯示器顯示處理結果。

PLL時鐘管理部分

主要是產生整個工程需要使用的幾個時鐘,100MHz的SDRAM控制器與SDRAM工作時鐘、75MHz的VGA驅動時鐘,24MHz的攝像頭xclk時鐘;圖1中使用不同的顏色對不同的時鐘域進行了標注。實際上,我們在設計SDRAM控制器時需要考慮存儲器的帶寬是否大于實際所需吞吐量。而存儲器的帶寬是由其工作時鐘頻率決定的,但由于刷新、激活、預充電的存在,SDRAM的實際存取速度比其工作時鐘頻率略小;實際所需吞吐量是指單位時間內向SDRAM寫入的數據量與從SDRAM讀出數據量之和。當存儲器帶寬小于實際所需吞吐量時,由于存取速度超過SDRAM的存取帶寬會導致數據來不及寫入或者讀出,此時無論寫數據緩沖器與讀數據緩沖器的深度設置為多大,必然會導致寫緩沖區上溢或者讀緩沖區下溢。對于高速視頻流緩存場景,這種問題會造成災難性的問題。因此,在設計SDRAM控制器時需要根據數據存取速度合理設置SDRAM的工作時鐘頻率。

二、 主要模塊分析

接下來我們對部分模塊的Verilog代碼實現方案進行簡單介紹。

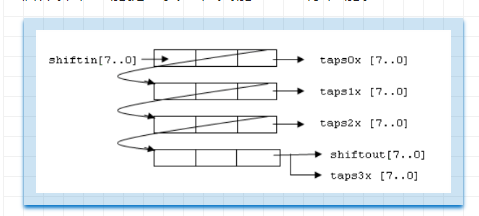

高斯濾波模塊與sobel邊緣檢測模塊都涉及到二維矩陣卷積,所以如何生成一個3*3的二維矩陣是我們需要考慮的。實際上,這里我們可以調用Quartus Prime軟件自帶的移位存儲器(shift_ram)IP核,將其配置為3個tap,每個tap之間的間距為1280個數據,如下圖所示。然后對每個tap輸出的數據打兩拍即可得到3*3的像素矩陣。然后使用流水線實現像素數據與模板權重的卷積計算,既能提高實時性又能保證時序性能。

圖2 移位存儲器結構示意圖SDRAM控制器部分主要是對檢測結果進行緩沖,由于我們使用的分辨率為1280*720,即使是二值(0、1)圖像也需要兩個大小為900Kbit的RAM存儲器進行乒乓緩存,而我們使用的EP4CE6F17C8型號的FPGA片上RAM僅有270Kbit,遠遠不能滿足需求;所以這里為了保證數據完整性,選用SDRAM來實現雙緩沖。在實現乒乓緩存時,使用sop(幀起始)與eop(幀結束)來控制完整數據幀緩存或丟棄。

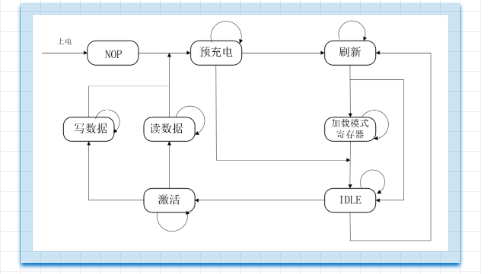

SDRAM接口模塊主要是配置SDRAM芯片的工作模式、存取數據,為了保證SDRAM芯片以較高的吞吐量存取數據,這里將SDRAM配置成了連續突發模式、突發長度為512。由于SDRAM的指令較多,工作時序比較復雜,這里選擇使用狀態機來設計SDRAM接口時序,狀態機設計如下圖所示:

圖3 SDRAM接口模塊狀態機轉移圖

三、 實現結果

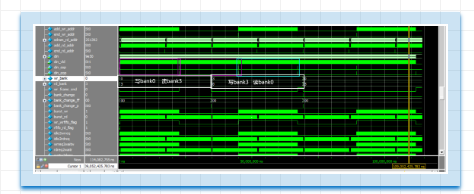

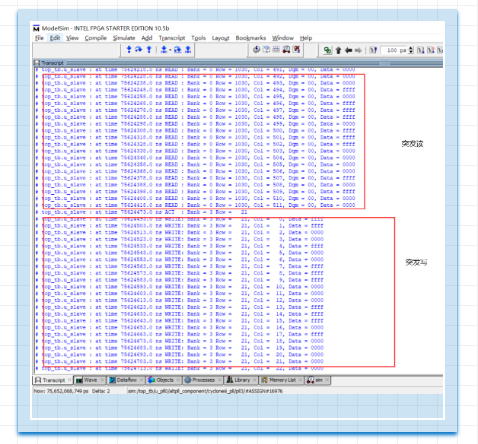

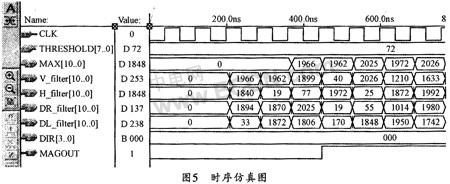

SDRAM乒乓緩存部分仿真結果如下圖4所示;當向bank0寫完第一幀數據之后,會丟棄下一幀數據,直到bank3中的一幀數據完整讀完時才會切換讀寫bank,然后再緩存下一幀新的數據。從圖5所示仿真結果可以看到,成功實現了對SDRAM兩個Bank的交替存取,實現了乒乓緩存的效果。

圖4 乒乓緩存仿真結果

圖5 SDRAM存取仿真結果本設計最終實現結果如圖6所示,能夠實時的檢測圖像邊緣,提取出目標的輪廓,達到預期效果。但是由于光線影響等方面的原因,導致最終實現出來的效果不是非常完美。

-

FPGA

+關注

關注

1643文章

21956瀏覽量

614011 -

檢測系統

+關注

關注

3文章

972瀏覽量

43708 -

圖像邊緣

+關注

關注

0文章

10瀏覽量

7392

發布評論請先 登錄

基于FPGA實時圖像邊緣檢測系統的實現

基于FPGA實時圖像邊緣檢測系統的實現

評論