簡介

過去幾十年來,無線系統通道數和帶寬一直穩步增長。對數據速率和系統整體性能的要求成為這些現代電信、雷達和儀器儀表系統發展的驅動因素。但與此同時,這些要求也加大了電源封裝和系統的復雜度,使功率密度和組件級別的功能變得更為重要。

為打破其中的一些限制,半導體行業將更多的通道整合到同一個硅封裝中,借此降低每個通道的功率要求。此外,半導體公司還將更復雜的功能整合到數字前端,簡化了過去在專用集成電路(ASIC)或現場可編程門陣列(FPGA)結構中才能實現的片外硬件設計。這些功能既包括濾波器、下變頻器或數控振蕩器(NCO)等通用組件,也有更復雜的特定應用操作。

信號調節和校準問題僅在開發多通道系統時才變得較復雜。這種架構可能需要每個通道有獨立的濾波器或其它數字信號處理(DSP)模塊,從而轉變成對節能更為重要的強化型DSP。

本文介紹了使用16通道發射和16通道接收子陣列的實驗結果,其中所有發射和接收通道都使用數字轉換器集成電路(IC)中的強化型DSP模塊來校準。與其它架構相比,這個多通道系統在尺寸、重量和功率上都更有優勢。對比該系統的FPGA資源利用率后可發現,強化型DSP模塊為多通道平臺的設計人員解決了重大挑戰。

數字信號處理模塊

真實信號,無論是用來合成還是接收,都需要一定程度的分析或處理,才能共同滿足任何應用所需的性能。信號鏈幅度衰減或平坦度的常見補償辦法是借助補償濾波器。圖1是增益和平坦度補償濾波器的示例,設計用于校正給定頻段內的缺陷,從而為下游應用創建更理想的響應。

圖1.ADC的頻率幅度平坦度響應可通過數字濾波來改善

對多通道系統而言,此處理必須能夠獨立控制每個通道,讓通道彼此獨立地運行。因此,該系統使用的是獨立的DSP模塊,可進行通道的相位和幅度對齊,還可在目標通帶內獲得平坦增益。由于每個通道和系統都是唯一的,DSP必須針對配置、環境和硬件組合專門調諧。

數字上/下變頻器模塊

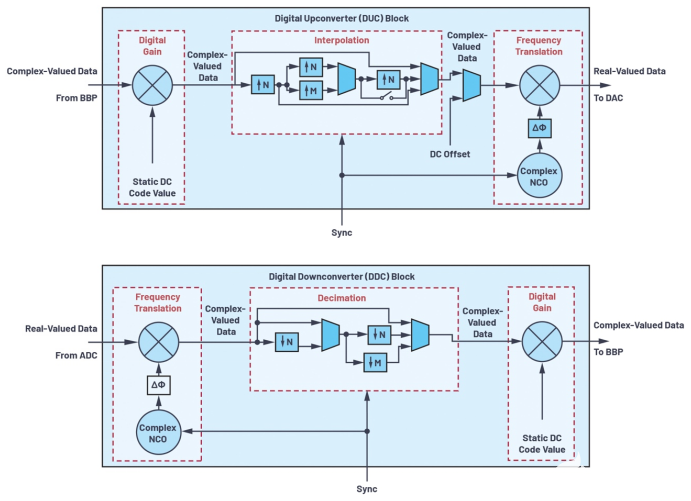

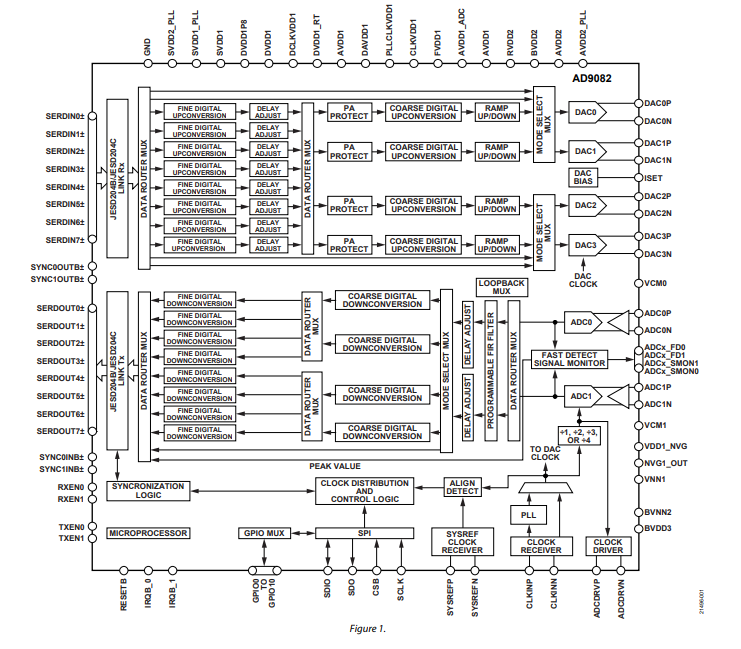

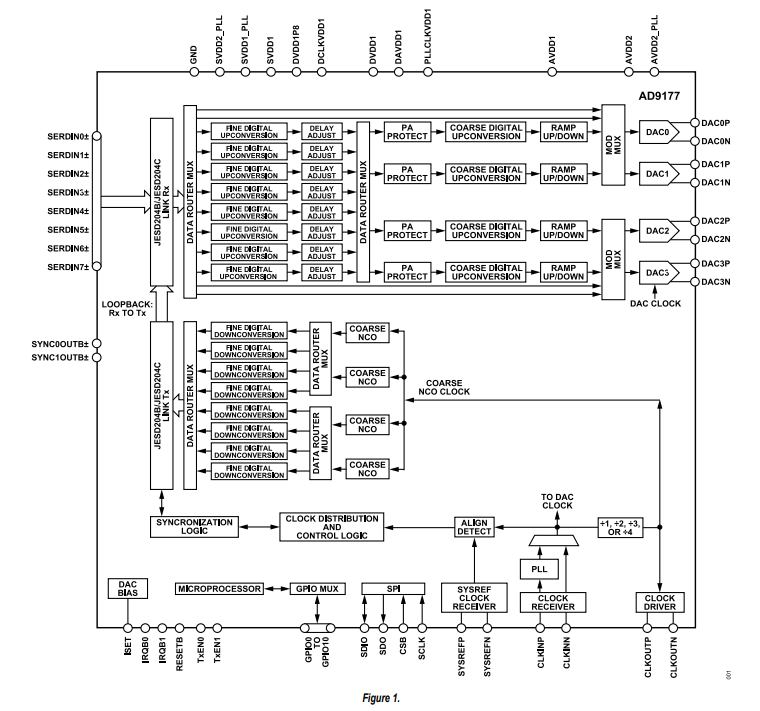

本文的結論主要依賴單芯片DAC和ADC中配置的數字上變頻器(DUC) DSP模塊和數字下變頻器(DDC) DSP模塊。圖2是DUC和DDC框圖示例,說明了這些數據通道常用的內部結構。這些DUC和DDC模塊有許多用途:

與數字接口的數據速率相比,內插(DUC)和抽取(DDC)轉換器的采樣速率。

轉化即將合成的DAC數據(DUC)和數字化ADC數據(DDC)的頻率。

將接口的數字數據發射導向基帶處理器(BBP)。

為每個通道實現數字增益,產生更接近系統滿量程值的碼值。

支持注入簡單的數字音調,無需數字數據鏈路,便能簡化系統快速啟動。

將每個通道的相位對齊通用基準。

我們往往希望卸載到轉換器或從轉換器卸載的數字數據速率與轉換器的采樣速率不同,從而降低系統功耗,提高系統的整體靈活性。因此,通常會部署數字上變頻器和下變頻器模塊。DUC模塊使來自BBP的發射波形數據能夠以低于DAC采樣速率的速率發射,因此也支持DAC以更高的速率合成內插波形數據(見圖2頂部的內插子模塊)。同樣地,DDC模塊使接收輸入在抽取前以更高速度的ADC采樣速率數字化,之后再以更低的數據速率發送到BBP(見圖2底部的抽取子模塊)。

此外,與通過數字接口發送到BBP或從BBP發送出的信號相比,頻率轉換在數字域內常用于合成或分析更高頻率的模擬信號。許多系統都在DUC和DDC中采用復值NCO,目的就是為了實現這種頻率轉換,如圖2所示。NCO可被認為是數字信號生成器,它能提供等同于本振(LO)的信號,當信號被發送到同樣在DUC/DDC中的數字混頻器中時,可以提高發送到DAC的發射波形頻率(和DUC的情況一樣),或降低從ADC發出的接收波形頻率(和DDC情況一樣)。當數字頻率轉換發生時,DDC內這些數字混頻器的輸出往往變成復值,使得同相位(I)和正交相位(Q)信號沿著最終連接到單獨ADC采樣實值數據的單一數字通道傳輸。同樣地,到達DUC數字增益模塊數字混頻器的輸入復值信號在輸出端變成實值,然后簽發到單獨DAC,合成實值信號。

圖2.DUC和DDC模塊提供目前轉換器IC中許多有用的DSP功能

此外,DUC和DDC還使用戶能夠在轉換器的瞬時帶寬內獲得多個數字通道。結果就是BBP能夠合成和/或分析比子陣列本身的轉換器數量還要多的數據流。因此,如果兩個窄通道彼此隔得很遠,就需要能提供更好的信號合成或分析能力的系統。

正如圖2所示,數字增益模塊也經常出現在DUC和DDC中。數字增益通過向子模塊中另一個數字混頻器的輸入提供靜態數字碼值來實現。利用這個功能,用戶獲得的碼值更接近數字接口位數所提供的滿量程值。同樣地,只要向數字混頻器的一個端口提供連續靜態碼值,便可注入直流偏移連續波(CW)波信號,而非基帶數據。這樣用戶就能通過DAC將發射CW波輕松合成至模擬域,無需通過BBP建立JESD204B或JESD204C數據鏈路。

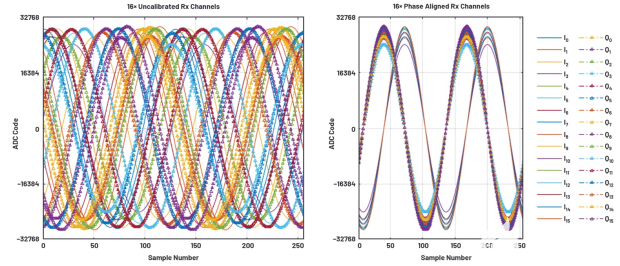

此外,相位偏移模塊經常部署在NCO的輸出,如圖2所示。這些相位偏移可按照系統內的通用基線參考來校正通道間相位偏差。由于每個DUC和DDC都有自己的NCO,因此只需針對給定的NCO頻率來偏移一個確定量的NCO相位,便可實現系統每個通道的相位對齊。這樣一來,在使用時遇到可用的多芯片同步算法時,所有通道間的確定性相位關系可通過這些NCO相位偏移進行校正1。 圖3顯示了實現相位對齊(通過嚴格為每個接收數據通路設置所需的NCO相位偏移值)前后,16通道同時接收I/Q數據采集的實驗結果。請注意,這些數字校正還校正了每個通道前端網絡中的射頻和微波損耗。

可編程有限脈沖響應濾波器

盡管NCO輸出相位偏移模塊可被用于單一頻率的相位對齊,子陣列校準則經常要求對整個目標頻帶進行相位對齊。此外需要幅度均衡,即所有通道名義上擁有相對于通用基準通道的相同幅度,還需要幅度增益平坦化,即所有通道擁有相對于頻率的恒定幅度響應。

為達到寬帶相位和幅度校正,通常還部署另一種DSP模塊。這種模塊被稱為有限脈沖響應濾波器(FIR)2。 FIR濾波器是一種數字濾波器,被大量用在DSP上,其系數決定了輸入數字信號的幅度和相位響應。允許更改這些系數的系統被視為可編程FIR濾波器(pFIR),用戶可根據每個通道生成自己需要的幅度和相位響應。

運用pFIR實現通道幅度對齊和增益平坦化

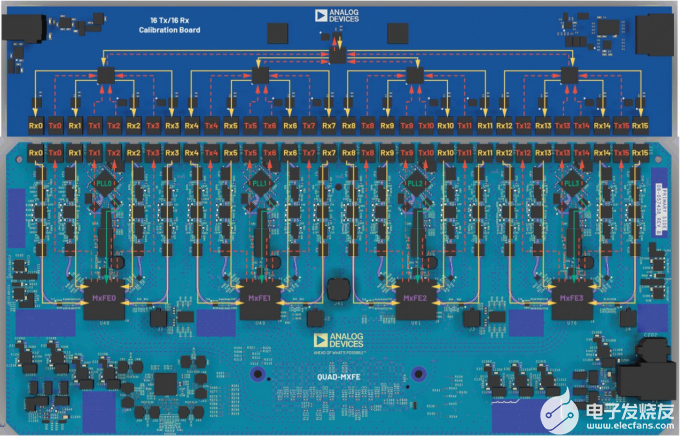

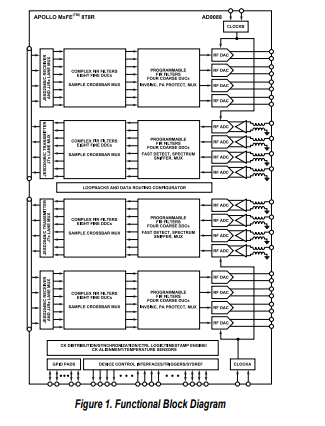

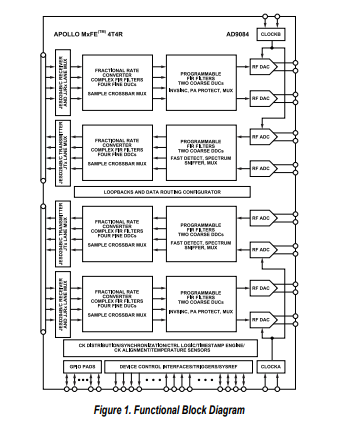

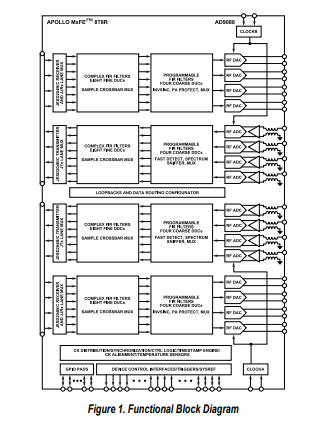

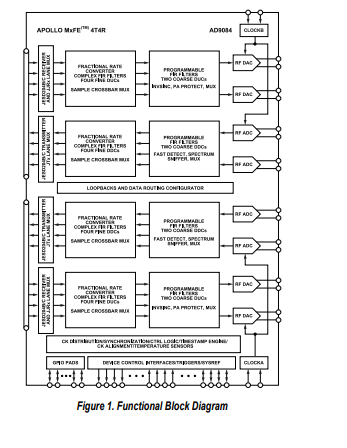

圖4是用于展示寬帶幅度和相位對齊以及增益平坦化的系統的高級框圖。該系統采用了四個數字化IC,各包含四個發射和四個接收模擬通道,或者八個發射和八個接收數字通道。當使用系統內的所有四個數字化IC時,總共可實現16個發射和16個接收模擬通道,或者32個發射和32個接收數字通道。單獨的鎖相環(PLL)頻率合成器IC用于給每個數字化IC提供轉換器采樣時鐘信號。此外,時鐘緩沖器IC用于提供多片同步算法所需的數字參考和系統參考時鐘1。 該系統起初配置在S頻段,設定NCO頻率,所有發射和所有接收通道的模擬信號頻率都在同樣的2.7GHz。所用的DAC采樣速率是12 GSPS,平臺會在第一奈奎斯特區合成發射通道。ADC采樣速率為4 GSPS,平臺會在第二奈奎斯特區采集接收通道。

圖3.實驗結果表明了16個接受通道的I/Q同時采集,利用數字化儀IC上的

DDC模塊提供的復雜NCO相位偏移嚴格進行相位對齊(而非幅度對齊)。

圖4.這個高級系統框圖用于證明多通道相位和幅度均衡/平坦度

如圖5所示,用連接的16發射/16接收校準板將組合通道發射信號準確地回送到每個單獨的接收通道,以便同時采集所有接收通道。系統的PLL頻率合成器再通過自身相位調整模塊對齊,發射通道和接收通道則使用DUC和DDC各自提供的NCO相位偏移模塊粗略對齊。這樣一來,子系統相位大致與校準頻率對齊,見圖3所示曲線,但未實現任何幅度對齊。盡管本文采用了16發射/16接收校準板,用電氣方法對齊系統,但還可通過系統校準反射器以無線方式獲得類似的配置,這也有助于校正任何天線通道間異常。

如圖4所示,96抽頭pFIR濾波器位于每個ADC的輸出,這樣每個ADC通道的相位和幅度響應可在整個ADC采樣速率的頻率范圍內彼此對齊。因此可將pFIR放在ADC和DDC模塊之間。這樣數字接口的數據速率就不同于pFIR的速率,所以需要知道系統頻率轉換和速率抽取的程度,以便采用pFIR進行通道幅度對齊。由于本文在每個ADC的輸入端采集實際數據,pFIR輸入為實值。此外,系統設計是可配置的,這樣每個ADC對的一個pFIR模塊就是已部署的解決方案,如圖4中的雙重實際模塊所示。這也允許在兩個獨立的ADC中使用I/Q復雜輸入,從而支持系統對齊。

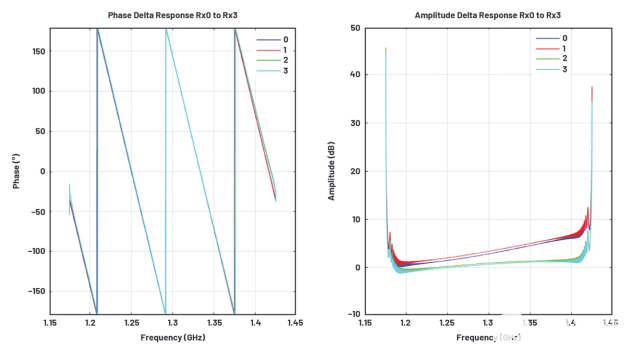

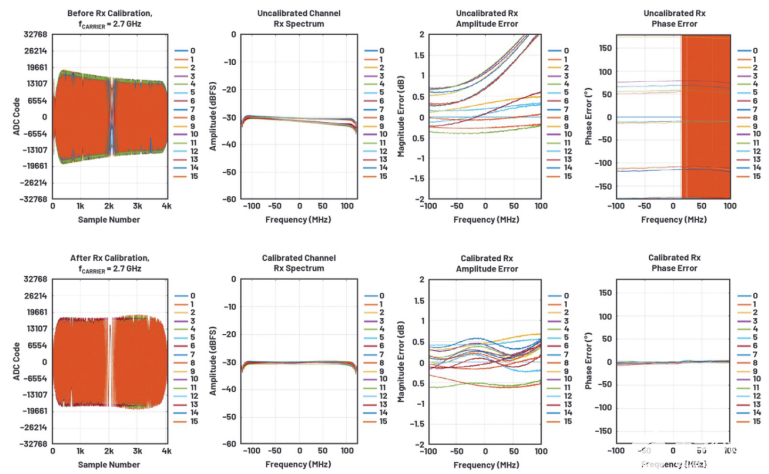

為實現系統內通道的幅度對齊和幅度平坦化,將寬帶掃頻波形載入每個發射通道,使得系統的I/Q帶寬中包含所有頻率。這樣用戶就能確定系統數據速率內所有頻率的頻率誤差響應。然后,在抽取的I/Q數據速率下獲得基線數據采集。本文的結論使用的是4 GSPS的ADC采樣速率和250 MSPS的I/Q數據速率。這樣每個發射NCO頻率設置為2.7 GHz,每個接收NCO頻率設置為1.3 GHz,原因是頻率從第二奈奎斯特區折疊到第一奈奎斯特區。基線數據利用MATLAB?系統接口采集,針對增益平坦化Rx0計算每個通道的幅度和相位誤差響應,這樣所有接收通道收到的最大值就是整個I/Q頻段的理想接收輸入。圖6顯示了系統內16個接收通道中四個通道的相位和幅度誤差響應。注意圖6左側,NCO相位偏移主要校正每個接收通道的相位誤差,但正如圖6右側所示,系統中的幅度誤差仍在。剩余的12個接收通道也有同樣的誤差響應。另外應注意,不僅接收幅度不同于Rx0,如果不使用其它校準技術,幅度平坦度也很差。這些異常是在ADC前端網絡中使用模擬濾波器時故意引入的,以便證明幅度平坦度和均衡。

圖5.測試設置了輸出發射(紅色)信號,然后利用連接的16發射/16接收校準板組合所有發射信號。再將組合后的信號進行均勻拆分,并回送到每個接收(橙色)通道。16發射/16接收校準板位于圖片頂部,與本文使用的獨立Quad-MxFE?平臺對接。PLL/頻率合成器信號(綠色)經過調整后可校正平臺上故意引入的熱損害。

圖6.每個通道相對于增益平坦Rx0的相位/幅度誤差響應有助于確定pFIR濾波器設計

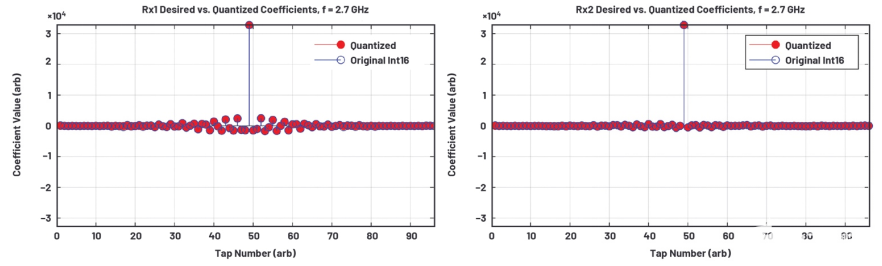

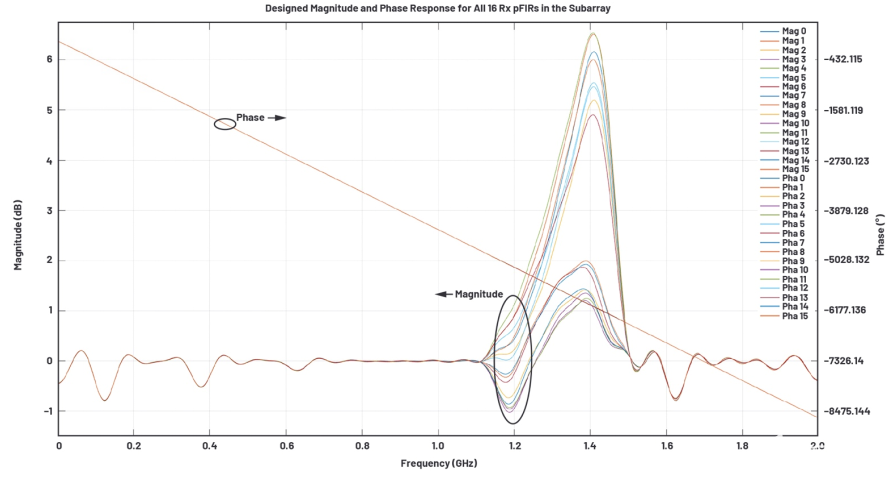

因此,為改進幅度對齊和幅度平坦度,根據每個通道相對于增益平坦Rx0的復值誤差響應設計實值96抽頭任意幅度和相位pFIR。應注意,pFIR設計算法更注重較窄目標I/Q波段的誤差響應。但是,完整的pFIR設計覆蓋更廣的全速率ADC奈奎斯特區,強制處于250 MHz子帶以外的區域使用統一的通帶響應。因此,本文中,集中在接收NCO頻率(1.3 GHz)的250 MHz子帶對pFIR設計而言比奈奎斯特區的剩余頻率更重要。這些pFIR采用MATLAB中DSP System Toolbox的濾波器設計功能,但同樣的算法也可用到現場系統的強化型數字電路中。圖7顯示了本文實例所用16個接收通道中兩個通道的96抽頭pFIR濾波器。剩下來的14個接收通道的pFIR設計相似。圖8顯示了針對子陣列中所有16個接收通道設計在全奈奎斯特區的pFIR幅度和相位響應。

必須注意,pFIR設計算法通常使用介于0到1之間的連續值系數空間。但是,硬件要求量化這些持續值系數,且必須位于系統可用的特定位寬內。系統為pFIR系數空間采用不同的位寬,這樣一來,一些系數是16位,一些是12位,還有一些只有6位。此外,12位系數必須在16位系數的旁邊。如圖7中的系數值所示,只有更大值的系數需要16位,更小值的系數只需要6位。但是,只要對理想的濾波器系數進行量化,都要引入量化誤差,應注意最小化本文中的這種量化誤差,設計的系數仍需擬合可用的系數空間。

量化完成后,借助數字化儀IC應用程序編程接口(API)功能,將pFIR系數載入每個通道。本文通過API使用串行外設接口(SPI)通信來修改每個通道的系數。但如果有必要,也可以使用專用的通用輸入/輸出接口(GPIO)信號在不同系數庫間進行更快切換。

圖7.單獨96抽頭pFIR旨在提供子陣列內的增益平坦和幅度對齊

圖8.針對所有接收通道設計的pFIR頻率響應顯示了每個通道應用的校準響應

圖9.為每個接收通道部署pFIR改進了相對于Rx0的幅度均衡和幅度平坦度

最后,獲得后續接收數據采集,同時啟用pFIR來分析pFIR設計的有效性。圖9頂部顯示了啟用pFIR前的結果。應注意,在幅度均衡步驟前,16個接收通道在感興趣的頻率范圍內有不同的幅度和相位。還應注意,八個接收通道的幅度平坦度響應與另外八個的不同。但在為每個接收通道設計和啟用pFIR后,如圖9最下方所示,所有接收通道的幅度在名義上實現了I/Q帶寬內的幅度均衡、幅度平坦以及相位對齊。幅度和相位均衡還可以通過更精細的pFIR設計實現改進,但這超出了本文的范圍。

數字化元件資源消耗與FPGA資源消耗

如上所述,片上強化型pFIR在抽取階段前就存在于ADC數據通路中。正如演示的,這些pFIR為用戶提供了重要的應用靈活性,但由于這個功能被卸載到數字化IC本身,因此它還使開發人員能夠大大減少FPGA資源。問題就變成:為什么要在數字化IC上而不是在FPGA的硬件描述語言(HDL)結構中使用強化型pFIR?這可以從幾個方面來回答:資源減少、設計復雜性和功耗。

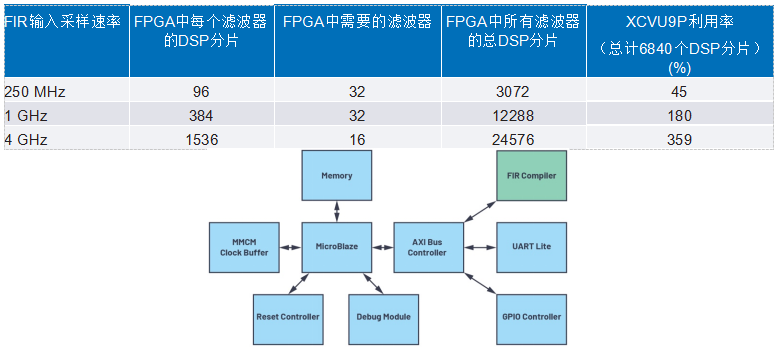

無論關注的領域是什么,資源減少向來都是一個重要的話題。數字化IC已經創建并安裝了強化型pFIR模塊。在FPGA中,可以從DSP分片上建立FIR濾波器,這些DSP分片包含特定的FPGA構造元件,意在提供DSP功能。FPGA DSP分片不同于傳統的邏輯門,比如觸發器,它會單獨計入FPGA資源利用率。要確定pFIR應用于數字化IC還是FPGA,FPGA的利用率——特別是DSP分片的利用率——變得至為重要。為了作對比,所選的VCU118平臺包含一個由6840個DSP分片組成的XCVU9P Virtex? Ultrascale+? Xilinx? FPGA。雖然DSP分片的數量已經相當可觀,但在確定結構中到底要放置多少個濾波器時,還必須考慮通道的數量。

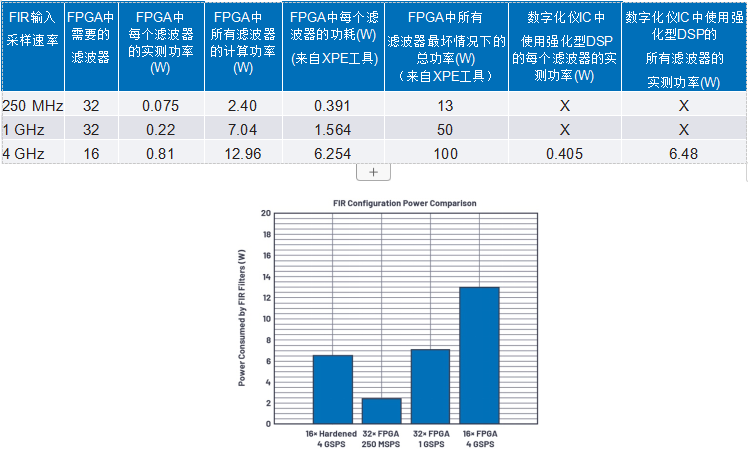

為此,必須知道濾波器所需的輸入采樣速率。表1顯示了在FPGA上合成一個FIR設計時所需的估計資源數量,針對的是能映射潛在數字化IC數據通道配置的幾個應用場景。這些為每個濾波器估計的資源來自Xilinx LogiCORE? IP FIR Compiler 7.2模塊摘要。為了查看這個概要,向Xilinx Vivado? Design Suite 2018.2創建的簡化MicroBlaze?設計添加了濾波器,如圖10所示。250 MSPS和1 GSPS速率的情況是FIR將使用從變頻器抽取的數據來運行,而4 GSPS的情況則是假設數據直接來自變頻器的未抽樣輸入。每個FIR濾波器的運行速度為250 MHz,以便模擬FIR濾波器在基帶數據通道中的運行速度,并且包含96個16位可重載系數。

鑒于XCVU9P FPGA的利用率,很顯然必須要用一個更大的FPGA,比如XCVU13P(包含12,288個DSP分片),來包含所有需要的濾波器。對于4 GSPS FIR濾波器這種情況,需要至少兩個XCVU13P設備來分擔所有濾波器的資源負載,這相應地減少了設計成本。相比之下,上文提到的用于強化型DSP pFIR部署的全部16個通道需要的所有濾波器全部包含在數字化IC本身中,目的是為了降低系統設計方法的復雜性。

表1.提高FIR采樣速率導致FPGA資源利用率超出現有能力,顯著增加了系統功耗

圖10.具有一個FIR濾波器的MicroBlaze設計在FPGA中啟用以確定資源利用率

FPGA中FIR的另一個主要問題是設計的復雜性,這與DSP分片資源利用率高有關。考慮如何構建濾波器。在硅片上,濾波器的設計被固定在芯片的單個位置,但系數和權重可以通過數字方式改變,從而實現一個相對靜態的執行。在FPGA結構中,FIR濾波器設計規定了那些DSP分片在芯片不同區域的布線。這意味著隨著濾波器的增加或變動,會消耗FPGA更多的區域,DSP分片之間的布線連接也變得越來越具有挑戰性。其次,擴展FIR濾波器設計可能會影響FPGA設計其余部分的布線,這會使時序關鍵布線變得很難,雖然在某些情況下并非不可能。

數字化元件功耗與FPGA功耗

行業總體趨勢是提高變頻器的采樣速率和多通道集成,這往往要求系統架構師在整體設計中實施DSP模塊時能分析系統功耗。過去這些DSP模塊通過可編程邏輯來實施,如FPGA中可看到的。但是,在FPGA內實施可配置模塊通常會產生過多的整體系統功耗。

為了嘗試直接比較兩個系統,我們為VCU118創建了幾個簡單的參考設計,目的是為了確定基于FPGA的濾波器方法在實際場景中功耗的相對差異。之所以選擇VCU118,因為當時它在Xilinx直接提供和支持的評估系統中擁有最多的DSP。基于VCU118,針對每個FIR輸入采樣速率創建了兩個Vivado項目:一個有濾波器,一個沒有。對于250 MHz和1 GHz這兩種情況,在設計中插入了八個FIR濾波器,如圖10所示。在4 GHz情況中,由于資源利用率高,設計中只插入了兩個FIR濾波器。每個濾波器使用輸出Xilinx LogiCORE DDS Compiler 6.0模塊饋送,以便確保使用的是有效數據。另外必須注意,在合成后要檢查RTL,以便驗證設計中保留了濾波器,確保它們沒有被優化掉。在針對每個采樣速率的第二個設計中,濾波器被移除,但所有其他IP模塊保留。

實施后啟動設計,采用電流測量創建一個相對功率偏差,以便隔離濾波器所需的額外功率。濾波器的電流消耗見表2每個濾波器的測量功率一欄。再通過設計中為數量有限的濾波器(八個濾波器用于250 MHz和1 GHz,以及兩個濾波器用于4 GHz)采集的數據推算出所有濾波器的總功耗。這個偏差是對比的基本單位,用于擴展到VCU118無法實施,但數字化儀IC可以實施的不同配置。作者認為,這對FPGA來說相對公平或可能有利,因為一個實際系統的功耗不可能會線性擴展。最后,將結果與Xilinx功耗估計器(XPE)工具為各種濾波器生成的功耗估值進行對比3。功耗估值遠遠高于推測的結果,但這也說明利用率提高造成的功耗是非線性增長的。

為了比較FPGA中FIR和數字化儀IC中的強化型pFIR的功耗,我們將簡單的濾波器設計測量的結果與多通道系統的實際電流消耗進行了比較,多通道系統使用數字化儀IC上的強化型pFIR DSP模塊。包括所有前端網絡和時鐘電路在內,使用未啟用強化型pFIR的數字化儀IC平臺的總系統功耗大約為98.40 W。如果所有16個強化型pFIR都啟用,使用數字化儀IC平臺的總系統功耗大約是104.88 W。因此,在多通道平臺使用強化型pFIR導致的功耗偏差總共約為6.48 W,包括了數字化儀IC系統上的所有16個接收通道。強化型pFIR直接接收來自ADC的數據,其運行速度必須為當前一代的ADC采樣速率(4 GSPS)。

表2.提高FIR采樣速率會導致系統功耗增加

圖11.數字化儀IC中的強化型DSP模塊改善了系統級功耗

但將這種功耗與假設有16個4 GSPS FPGA FIR的功耗作對比有點不切實際,因為對單個Virtex Ultrascale+系列FPGA而言,其資源利用率不可能很高。因此,將250 MSPS速率的FPGA FIR與強化型4 GSPS pFIR作對比,表2和圖11顯示了32個FPGA FIR(16個I FIR和16個Q FIR)的功耗是2.40 W。FPGA中的濾波器的運行速度比強化型數字化儀IC DSP模塊中的慢16倍多,但FPGA的功耗仍是強化型數字化儀IC功耗的0.37倍。將32個1 GSPS FPGA FIR與強化型4 GSPS pFIR相比,FPGA FIR的功耗約為7.04 W(其功耗要比強化型pFIR的高得多),運行速度則比強化型pFIR的慢4倍。將16個4 GSPS FPGA FIR與16個強化型4 GSPS pFIR作比較,FPGA的功耗是這個系統配置的2倍。總之,圖11表明數字化儀IC中強化型pFIR的功耗要低于相應的FPGA FIR濾波器的。此外,強化型pFIR降低了FPGA DSP片的利用率,這也降低了設計的復雜性和總功耗。利用更高速率的濾波器拓寬了250 MSPS濾波器數據速率不可能降低時的寬帶應用場景。

最后要考慮的一個因素是在過度依賴FPGA資源的設備中(如數字化儀IC AD9081)利用強化型DSP的可擴展性。在許多應用中使用16個通道,也許只是最終系統的一個小子陣列。對許多利用強化型DSP(如AD9081中)的系統集成商而言,與通過增加FPGA資源拓展后端處理相比,可以得到更靈活的規模級解決方案以及更簡單的信號鏈。關于這個爭論,作者主要考慮了擁有中央處理模型的系統,其中所有數據最終必須聚集到單個FPGA中。在這種情況下,隨著通道規模的擴大,向更多的數據變頻器增加內置濾波功能就需要更多的SERDES線路,從架構方面看,管理很簡單,因為并不需要更多FPGA資源。沒有這些強化型DSP功能,系統集成商就需要連接多個FPGA,以便針對同樣的應用獲得必要的資源,情況會非常復雜。

結論

本文介紹了一個在單片數字化元件IC中整合DSP模塊的系統,并用具體的例子證明了這些數字化模塊可以提供相控陣、雷達、衛星通信和電子戰應用所需的多通道幅度和相位均衡。一種采用pFIR數字濾波器和DUC/DDC NCO相位偏移的方法表明,無需將這些DSP模塊整合到FPGA中,也可實現多通道寬帶均衡。用來進行這種驗證的系統見圖12,稱為Quad-MxFE Platform4 ,可從ADI公司購買。明確來講,AD9081 MxFE IC已經成為子陣列設計的主干。Example HDL、MATLAB腳本和用戶證明文件可在ADQUADMXFE1EBZ產品維基頁面(ADI公司2020)上查看。16發射/16接收校準板(ADQUADMXFE-CAL)也已開售。儀器儀表和5G市場也許會對這些技術在子陣列測試和測量或基站開發方面的運用感興趣。

圖12.Quad-MxFE平臺可從ADI公司購買

-

adc

+關注

關注

99文章

6639瀏覽量

548260 -

數字濾波器

+關注

關注

4文章

272瀏覽量

47502

發布評論請先 登錄

AD9082四通道16位12GSPS RFDAC和雙通道12位6GSPS RFADC技術手冊

AD9088八通道、16 位、16 GSPS RF DAC和八通道、12位、8 GSPS RF ADC技術手冊

AD9084 Apollo MxFE四通道、16位、28 GSPS RF DAC和四通道、12位、20 GSPS RF ADC技術手冊

AD9177具有寬帶信道選擇器的四路、16位、12 GSPS RF DAC技術手冊

AD9088 Apollo MxFE 八通道、16位、16 GSPS RF DAC和八通道、12位、8 GSPS RF ADC技術手冊

AD9084 MxFE 四通道、16位、28 GSPS RF DAC和四通道、12位、20 GSPS RF ADC技術手冊

使用多片DAC61416芯片,如輸出50channel,這么多通道還能同時輸出嗎?

采用電容型PGA,納芯微推出高精密多通道24/16位Δ-Σ型ADC

AMC7812具有多通道模數轉換器(ADC)數模轉換器(DAC)和溫度傳感器數據表

AMC60804T具有電流和電壓輸出DAC和多通道ADC的4通道光學監視器和控制器數據表

AMC60304具有高電流輸出DAC和多通道ADC的4通道光學監視器和控制器數據表

AFE11612-SEP具有多通道ADC、DAC和溫度傳感器的耐輻射模擬監視器和控制器數據表

ADC/DAC IC上的集成強化型DSP改進寬帶多通道系統

ADC/DAC IC上的集成強化型DSP改進寬帶多通道系統

評論