如果您在通信行業工作,那么您可能很熟悉抖動對系統性能的影響。抖動不僅會降低數據轉換器的性能,而且還可在高速數字系統中產生誤碼。憑直覺判斷,給時鐘增加噪聲會增大系統其它部分的噪聲。因此我總是試圖通過選擇可帶來最小附加抖動的組件來最大限度地降低總體抖動。顧名思義,附加抖動就是由位于時鐘源(例如合成器或振蕩器)與被計時器件之間的組件所增加的噪聲。該附加噪聲可增大時鐘的不確定性,導致抖動增加。

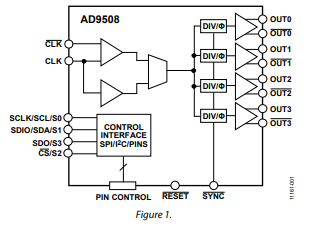

在實際系統中,一個時鐘源要驅動多個器件,因此可使用時鐘緩沖器(通常稱為扇出緩沖器)來復制信號源,提供更高的激勵電平。

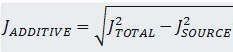

LMK00304 扇出緩沖器就是一個很好的例子。時鐘緩沖器產生的附加抖動主要影響時鐘的寬頻帶噪聲。它可使用圖 2 中所示的方根公式進行計算。

附加抖動的計算方法是:使用信號源 (J1) 測量出總體綜合抖動,然后加入緩沖器并在輸出端進行相同的測量。不過要小心一點,……如果您使用傳統信號發生器,那么時鐘的噪聲等級可能會誤導您,讓您以為所產生的附加噪聲微不足道。

良好的測量技術可確保測量所使用信號源的噪聲遠遠小于被測量器件。例如,使用一個由 Agilent E5052 信號源分析器和 Wenzel 100 MHz 振蕩器(具有信號調節)組成的測試裝置,我們將測量到大約 46fs 的綜合抖動。而在時鐘后面布置一個緩沖器并進行相同的測量,則可得到大約 102fs 的總體綜合抖動。使用以下公式計算附加抖動:

我們的測試裝置得到了大約 91fs 的附加抖動。如果我們將時鐘源改為高質量信號發生器等可能將要裝在您工作臺上的組件,信號源抖動將升高至 150fs 左右。這就越來越有意思了,……而且也不那么顯眼。如果現在我們將相同的緩沖器放在該噪聲源的后面并再次測量總體綜合抖動,得到的結果將大體相同,會讓我們認為附加抖動可以忽略。

因此,您在比較不同廠商時鐘緩沖器的產品說明書時,務必要查看參數說明(或者給應用工程師打個電話),了解抖動如何測量。如果時鐘源的噪聲相對于被測量器件而言比較高,那么抖動數字可能會有誤導性。您在自己進行測量時也要牢記這一點,否則您可能會發現尋找附加抖動的地方完全不對!

責任編輯:haq

-

時鐘緩沖器

+關注

關注

2文章

142瀏覽量

51244 -

模擬

+關注

關注

7文章

1436瀏覽量

84336 -

測量

+關注

關注

10文章

5167瀏覽量

112921

發布評論請先 登錄

AD9508 1.65GHz時鐘扇出緩沖器,集成輸出分頻器和延遲調整技術手冊

核芯互聯CLF04828超低噪聲時鐘抖動消除器介紹

抖動對系統性能的影響

抖動對系統性能的影響

評論