通過之前的介紹

USB3.0 PHY簡介

首先我們需要了解PHY具體完成哪些工作以及我利用FPGA能 實現哪些工作才能實現USB通信。

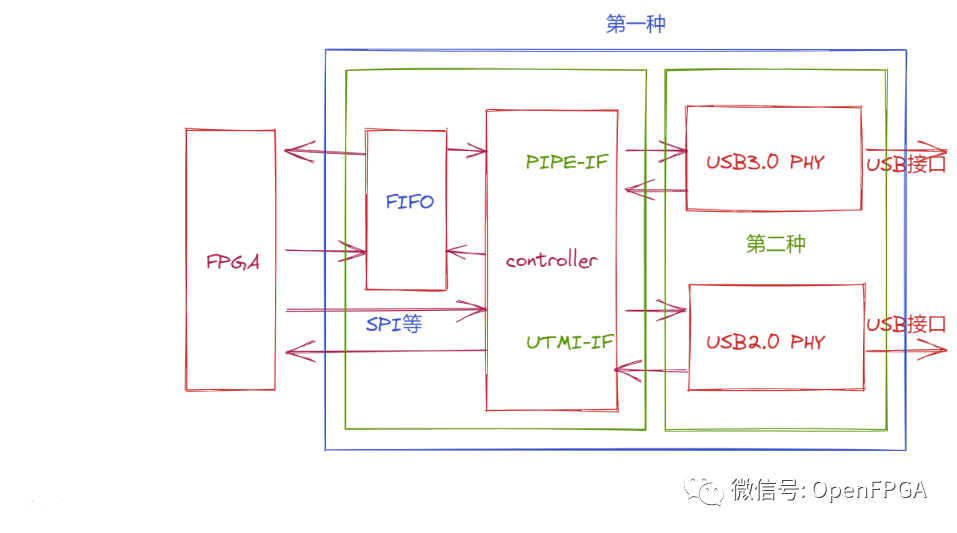

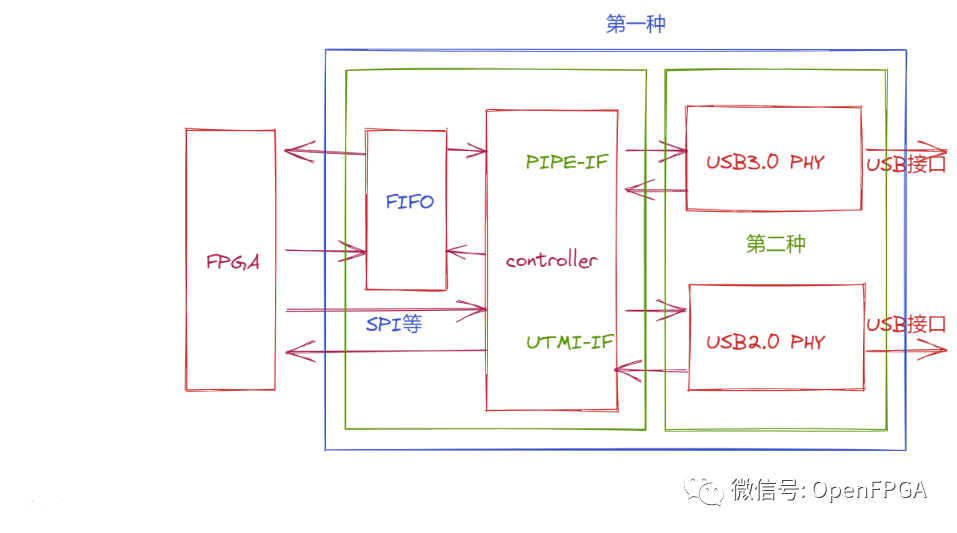

要實現USB通信大致需要兩部分:Controller和PHY兩部分,Controller大多為數字邏輯實現(邏輯控制主要分為:MAC、CSR以及FIFO,MAC部分主要按照USB協議進行數據的打包和分解,并按照PIPE(USB3.0)或者UTMI(2.0)的總線的數據格式發送給PHY(2.0或者3.0);

CSR部分主要進行寄存器的控制(軟件對寄存器進行操作主要是操作CSR寄存器;FIFO部分主要是實現高速和低俗轉換。));PHY通常為模擬邏輯實現(實現并轉串的功能,把UTMI或者PIPE口的并行數據轉換成串行數據,再通過差分數據線輸出到芯片外部)。大致的通信方式如下圖所示:

PHY部分負責最底層的信號轉換,作用類似于網口的PHY,這里如果大家需要了解具體的工作可以查看usb specification,因為和本文關系不大,所以不過多介紹了。

Controller部分主要實現USB的協議和控制。也是目前普通FPGA可以實現的,整個作用類似網絡中的MAC層。

PS:目前高級一點的FPGA(帶SerDes),可以在不借助外部PHY的情況實現USB(主要原因還是USB大量地借鑒了第二代PCIe協議,所以基本實現和PCIe差不多),但是相對外置PHY成本過高,需要使用IP等原因市場上還是很少這么做的。

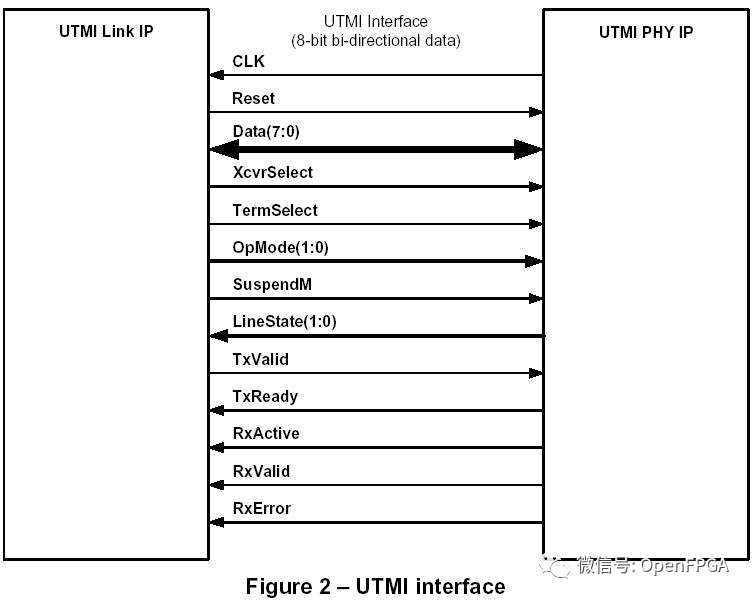

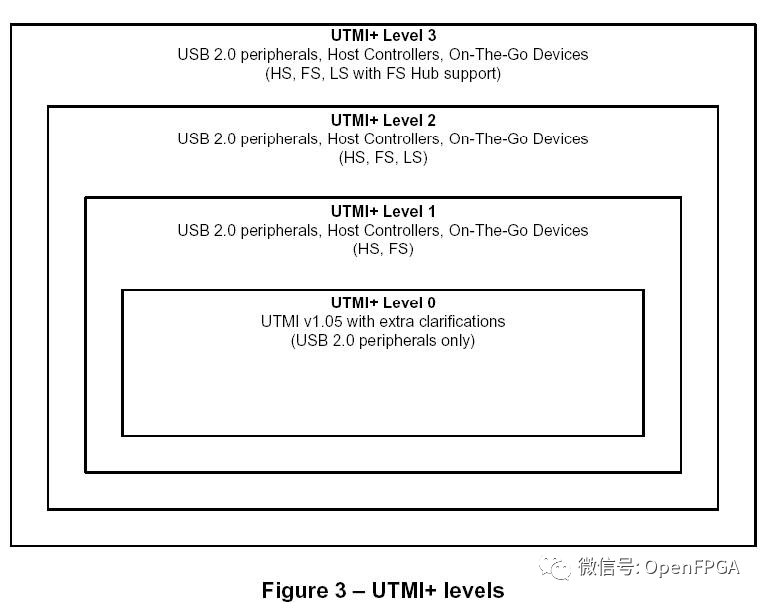

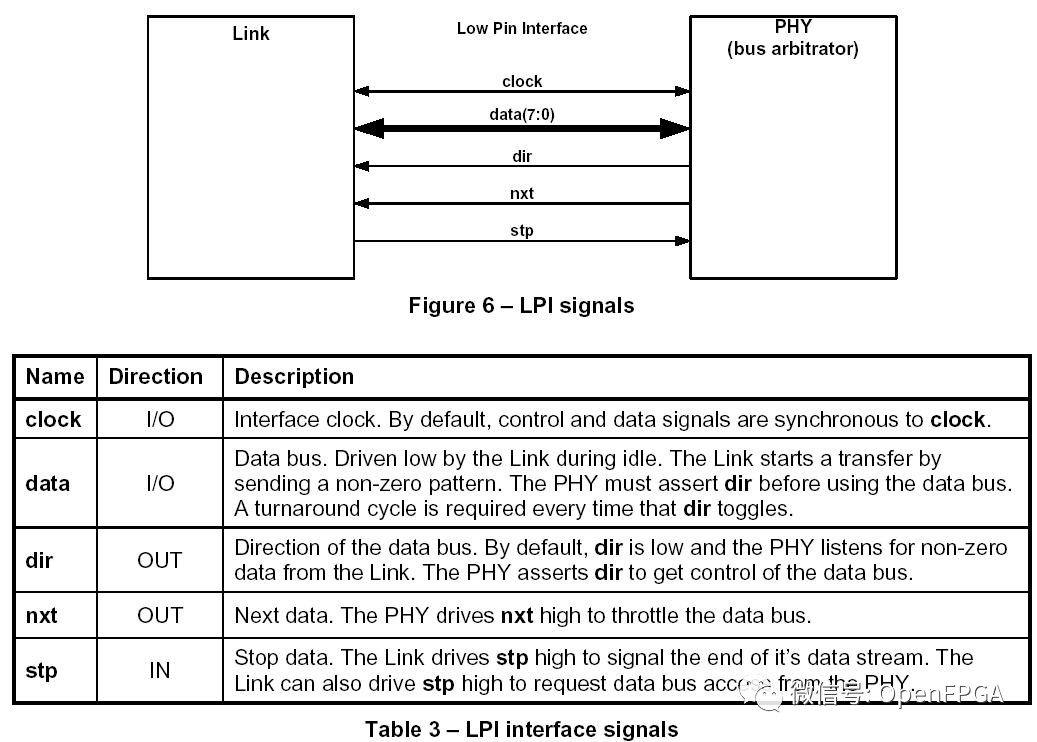

在上圖中還看到UTMI和PIPE,這是PHY和controller通信的接口,USB2.0PHY主要使用ULPI和UTMI,USB3.0主要使用PIPE,對于ULPI和UTMI的區別如下:

UTMI LEVEL0 通信連接示意圖

升級的UTMI+接口

ULPI(UTMI+ Low Pin Interface) 通信連接示意圖

以上三種接口都是和USB2.0 PHY通信的接口(如果還不理解的話,這三種接口類似網口中媒體接口-MII、RGMII、GMII等)。區別大概為USB PHY的位置:如果芯片的usb phy封裝在芯片內,采用UTMI+的接口。不封裝到芯片內的采用ULPI接口,這樣可以降低pin的數量。

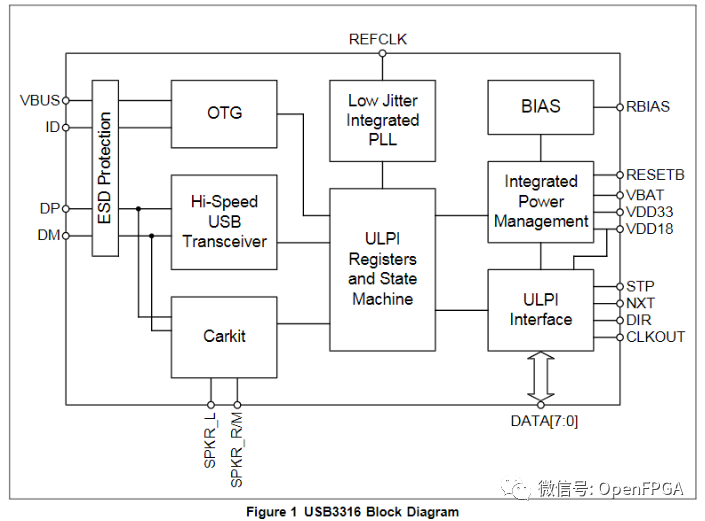

舉例如下:我用FPGA實現USB2.0通信,我使用邏輯實現cntroller+外掛USB PHY的方式,那么我的接口基本使用ULPI接口(降低pin的數量);

USB3316 芯片邏輯框圖 (來源:芯片數據手冊)

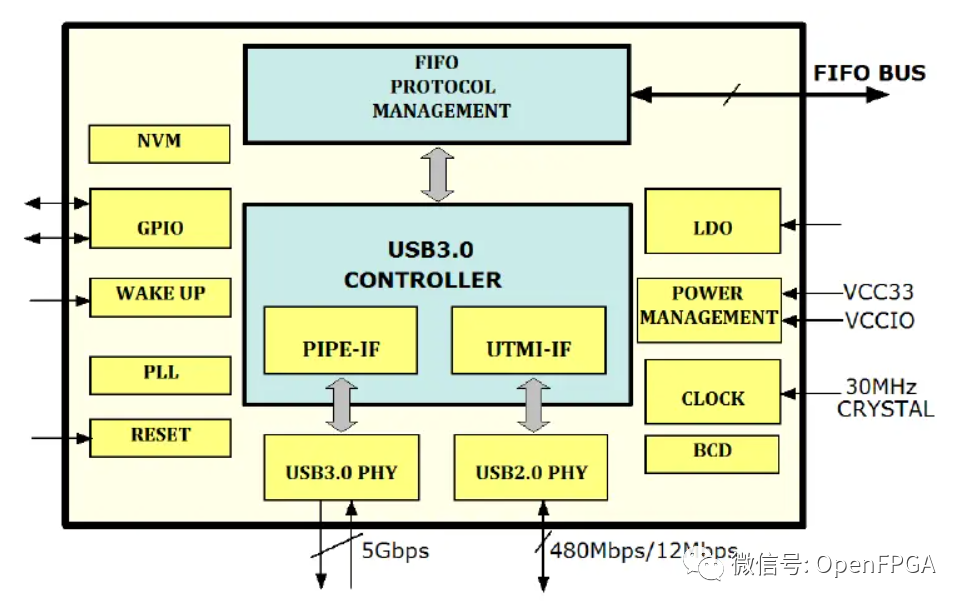

我覺得邏輯部分有點復雜,我想把邏輯部分放到外部PHY里,我只需要控制FIFO或者一些低速接口即可實現整個USB通信,這種芯片內部帶了cntroller+USB PHY,如下圖所示:

FTDI600/601Q 芯片邏輯框圖 (來源:芯片數據手冊)

上圖中可以看到FPGA和controller通信方式為FIFO或者SPI等接口,SPI主要時用在2.0/1.1時代,典型代表(MAX3421E)。而FIFO則是目前3.0時代比較常用的方式。

通過以上分析,其實目前常用的USB3.0 PHY也可以大致分為兩種:帶controller和不帶controller,這兩種PHY市場上傾向于帶controller的芯片,主要原因是簡單、方便、性價比高,這里在多說一句,目前市場上為了方便開發,USB3.0芯片內部會放置一個單片機,主要還是方便擴展接口,以方便芯片不單單只在USB3.0通信方面應用。下面一節我們就簡單介紹一下市場上常見的USB3.0 PHY片。

市場上常見的PHY

上圖中可以將PHY分為兩種,下面會標注是第一種還是第二種,兩種的區別在上一節中已經進行區分了,這里就不再贅述了。

| 公司 | 型號 | 功能 | APP接口 | 物理層接口 | CPU核 | 第幾種PHY |

|---|---|---|---|---|---|---|

| TI/ NI | TUSB1310A | 純PHY | / | PIPE 3 | 無 | 第二種 |

| Cypress | CYUSB3014 | OTG控制器(2.0)+PHY Slave控制器+PHY | GPIF II | 內部PIPE | ARM926EJ-S | 第一種 |

| FTDI | FT600/FT601 | FIFO interface bridge | / | FIFO | 無 | 第一種 |

| 南京沁恒 | CH569/565 | USB3.0 主機Host/設備Device模式、OTG功能,支持USB3.0 HUB | HSPI | / | RISC-V | 第一種 |

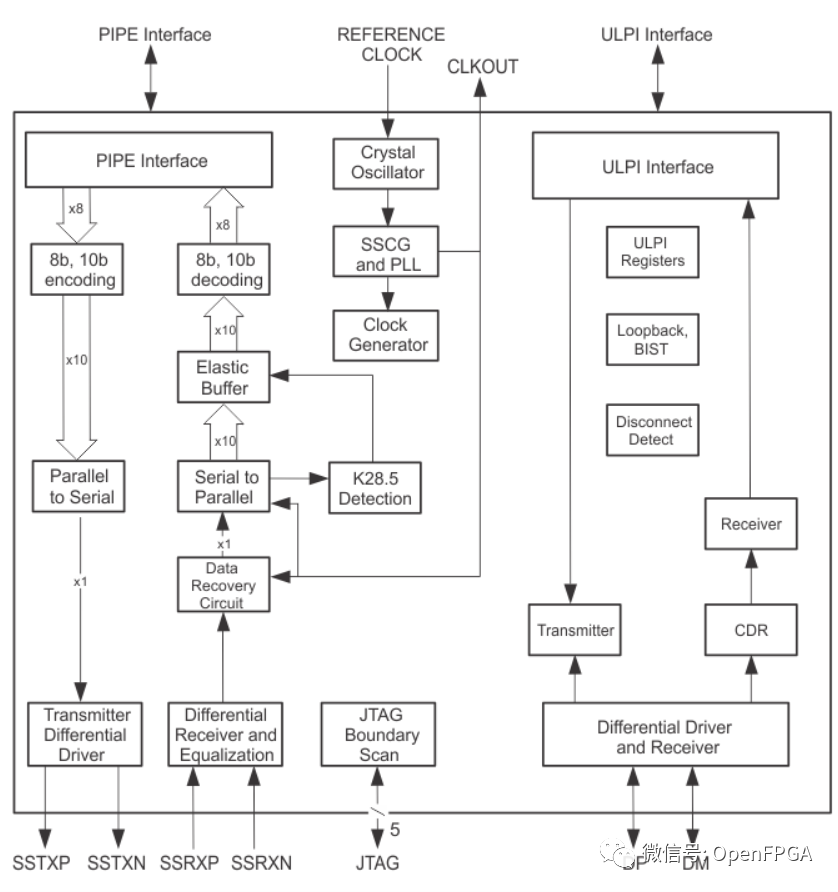

1、TUSB1310A

?

https://www.ti.com.cn/document-viewer/cn/TUSB1310A/datasheet

?

TUSB1310A 框圖

2、CYUSB3014

中文版數據手冊:

?

https://www.cypress.com/file/133711/download

?

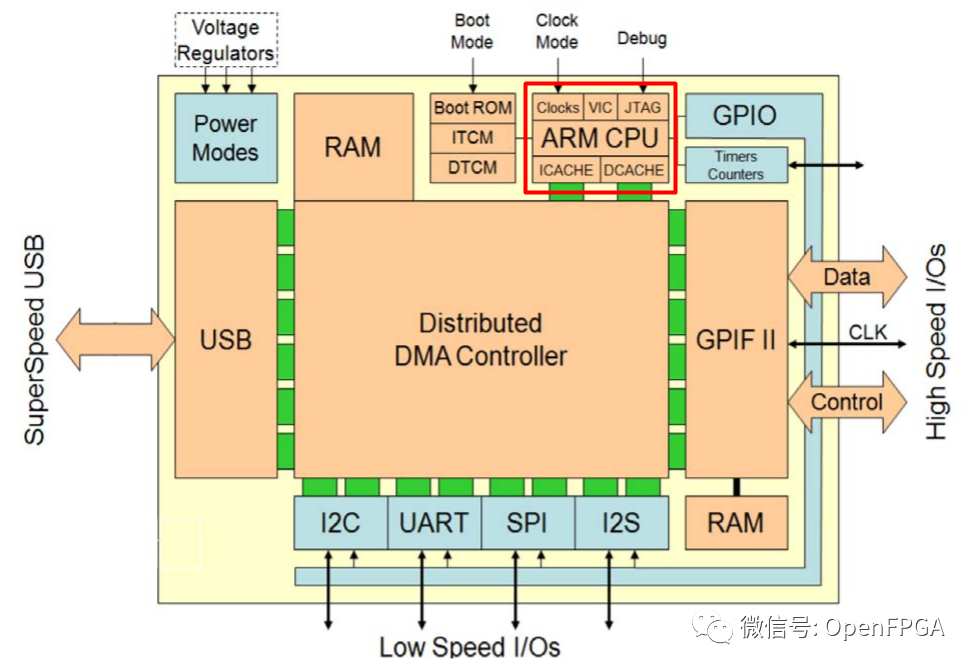

CYUSB3014 框圖

3、FT600/FT601

?

https://ftdichip.com/products/ft600q-b/

?

?

https://ftdichip.com/wp-content/uploads/2020/07/DS_FT600Q-FT601Q-IC-Datasheet.pdf

?

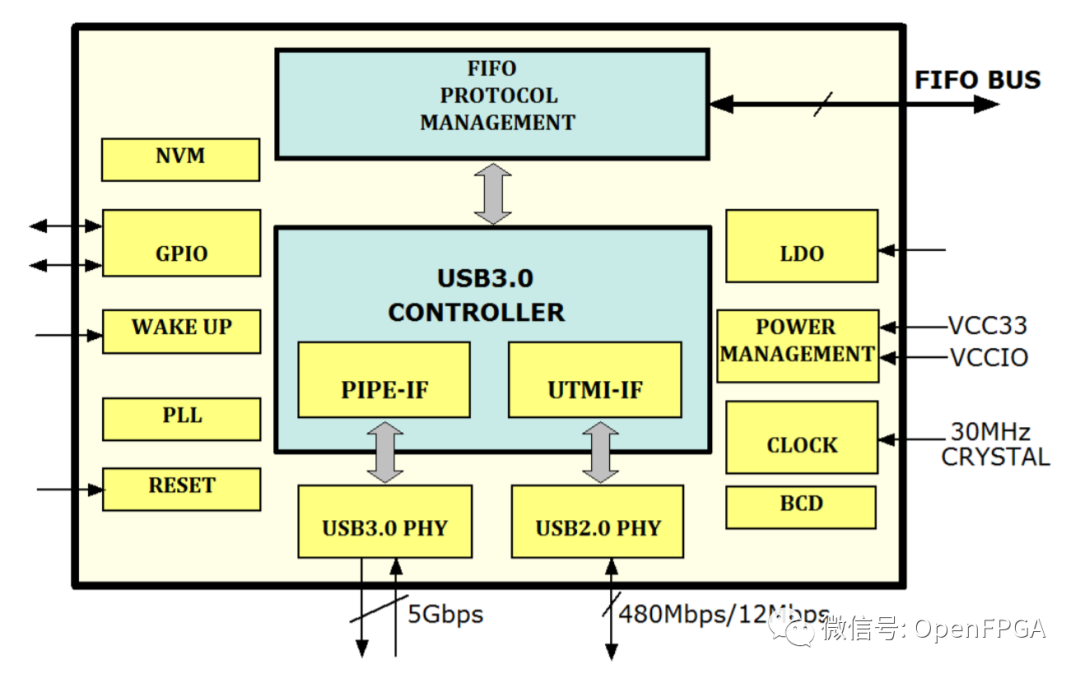

FT600/FT601 框圖

4、CH569/5

?

http://www.wch.cn/products/CH569.html

?

?

http://www.wch.cn/downloads/CH569DS1_PDF.html

?

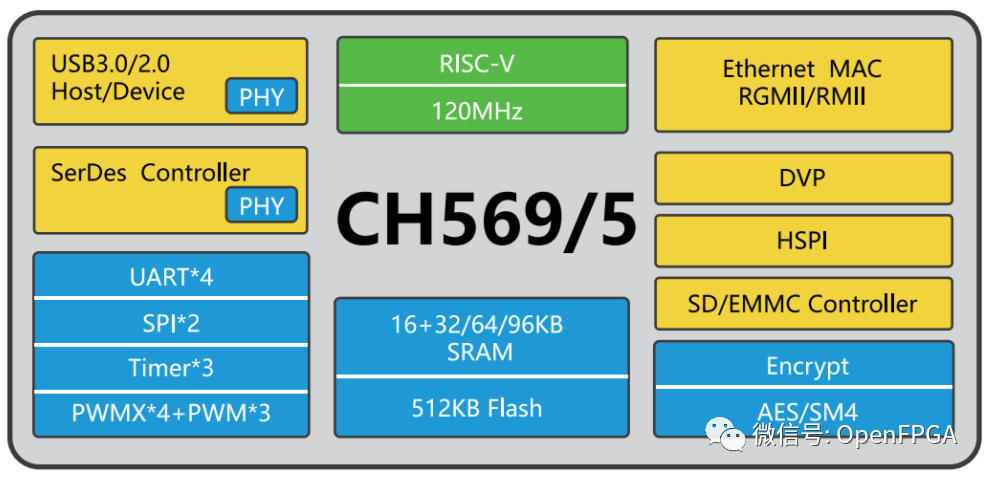

南京沁恒 CH569/565 框圖

PS:RISC-V內核,120MHz系統主頻,支持單周期乘法和硬件除法、可編程中斷控制器、低功耗兩級流水線。

總結

上面的表格也很清晰表現出各個芯片的區別,這里就不展開描述了,這里在介紹幾個USB 3.0 的ReDrive(NXP , PTN36221AHX 單通道橋,PTN36241BBS單通道橋,PTN36242LBS雙通道橋(數據手冊:https://www.nxp.com/docs/en/data-sheet/PTN36221A.pdf))。

今天的文章就到這里,綜合考慮上面的芯片,我們后續的方案使用使用廣泛的CYUSB3014繼續接下來的系列文章。

編輯:jq

-

FPGA

+關注

關注

1643文章

21956瀏覽量

614022 -

usb

+關注

關注

60文章

8137瀏覽量

270787 -

數據手冊

+關注

關注

95文章

6204瀏覽量

43478

原文標題:FPGA和USB3.0通信-USB3.0 PHY介紹

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

使用CYUSB3014作為USB3.0數據傳輸方案,USB3.0無法識別是什么原因?

PC電腦USB3.0接口無法識別CX3設備分辨率怎么解決?

在automaster和autoslave項目中如何配置參數來滿足usb3.0和usb2.0的數據傳輸?

是否可以與USB2.0集線器 (CYUSB2302) 共享USB2通道SS線路直接到USB3.0端口?

CYUSB3014無法識別為USB3.0設備怎么解決?

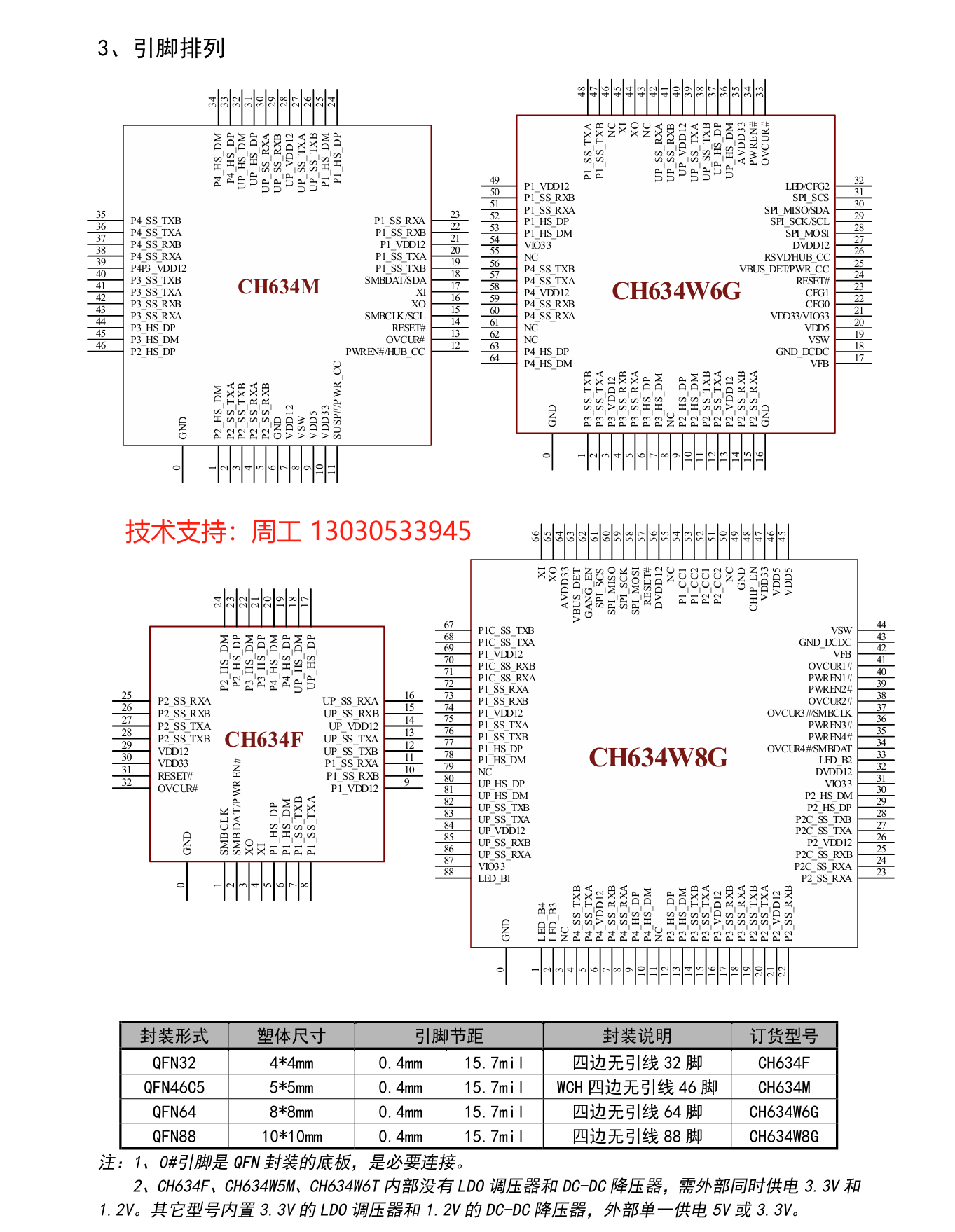

CH634USB3.0HUB控制芯片USB3.0國產控制芯片

基于FT600Q芯片 的USB3.0設計,為什么連接PC后設備無法識別?

軒展科技發布4K USB3.0編碼采集模塊

請問ISO7760能應用在USB3.0數據上隔離嗎?

USB3.0的識別問題

CYUSB3014是否會自動調整工作模式USB3.0還是USB2.0?

USB3.0/3.1靜電放電防護方案

FPGA和USB3.0通信-USB3.0 PHY簡介

FPGA和USB3.0通信-USB3.0 PHY簡介

評論