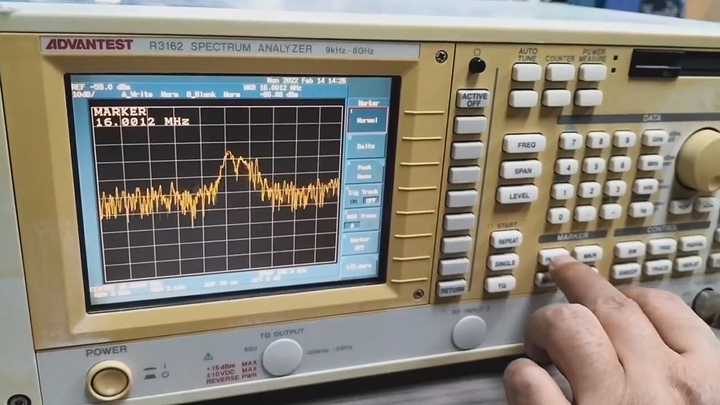

在設(shè)計(jì)FPGA項(xiàng)目的時(shí)候,對(duì)時(shí)鐘進(jìn)行約束,但是因?yàn)?a href="http://www.asorrir.com/v/tag/2562/" target="_blank">算法或者硬件的原因,都使得時(shí)鐘約束出現(xiàn)超差現(xiàn)象,接下來(lái)主要就是解決時(shí)鐘超差問(wèn)題,主要方法有以下幾點(diǎn)。

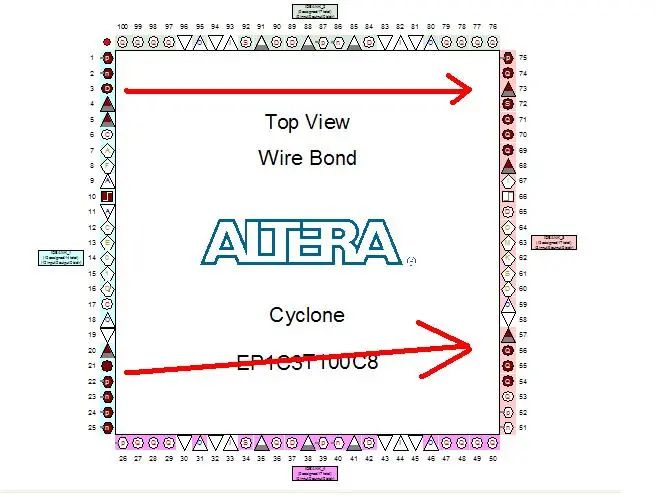

第一:換一個(gè)速度更快點(diǎn)的芯片,altera公司的cyclone系列FPGA,有6,7,8速度等級(jí)的,8的最慢,6的最快,或者cyclone系統(tǒng)4,5更快的芯片,當(dāng)然了成本會(huì)增加些的。

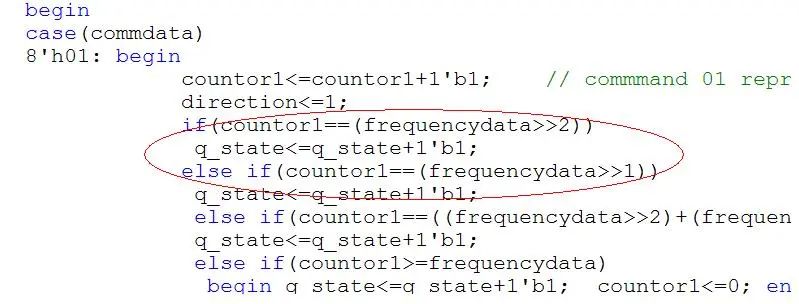

第二:盡量避免在FPGA中做乘法和除法的運(yùn)算,除非這個(gè)FPGA有硬件乘法器。我使用的這個(gè)FPGA沒(méi)有硬件乘法器,我就盡量利用左移或者右移來(lái)做乘法和除法運(yùn)算。

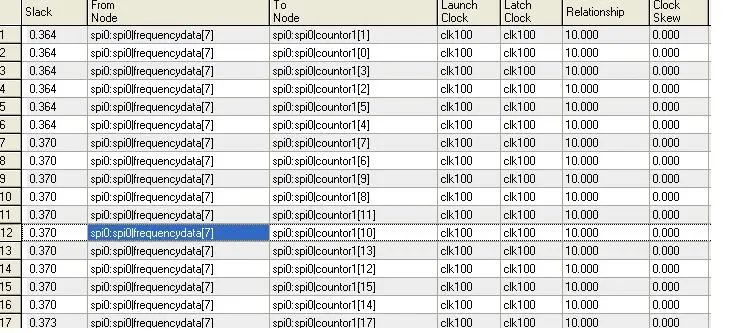

第三:重新分配一下IO管腳,這樣在布局布線的時(shí)候,會(huì)提高一定程度的時(shí)鐘余量。下圖是調(diào)整IO分配以后,時(shí)鐘余量提高了0.2ns。

第四:就是看看超差的那個(gè)線路,增加一些中間寄存器,或者使用流水線技術(shù),就是將組合邏輯和時(shí)序邏輯分開(kāi),大的時(shí)序邏輯,盡量?jī)?yōu)化成由很多小的時(shí)序邏輯組成一個(gè)大的時(shí)序邏輯。或者更該程序代碼,更該算法。到這一步就是沒(méi)有辦法的辦法了。

第五:有些時(shí)候在程序中加入一些和項(xiàng)目不相關(guān)的代碼,也可以提高正常程序的時(shí)鐘約束余量,估計(jì)是不相關(guān)代碼擠占了一些邏輯單元,使得正常程序在布局布線的時(shí)候,選擇了其他路徑吧。這個(gè)辦法不固定,瞎貓碰死耗子的事情。

主要就是這幾種方法了,首先要選好芯片,這是最重要的,不然為了省成本,最后發(fā)現(xiàn)芯片速度不夠,很煩人的。

最后提一下有些網(wǎng)友提到FPGA發(fā)熱厲害的現(xiàn)象,看看你在項(xiàng)目中是不是將unused pin 接地了,這樣芯片會(huì)發(fā)熱,最好將unused pin 微上拉,或者設(shè)置為輸入即可。

編輯:jq

-

FPGA

+關(guān)注

關(guān)注

1643文章

21954瀏覽量

613939 -

芯片

+關(guān)注

關(guān)注

459文章

52145瀏覽量

435915 -

乘法器

+關(guān)注

關(guān)注

9文章

211瀏覽量

37804

原文標(biāo)題:FPGA時(shí)鐘約束時(shí)鐘余量超差解決方法

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

晶振頻偏超差?這5個(gè)核心因素正在悄悄改變你的時(shí)鐘精度

FPGA時(shí)序約束之設(shè)置時(shí)鐘組

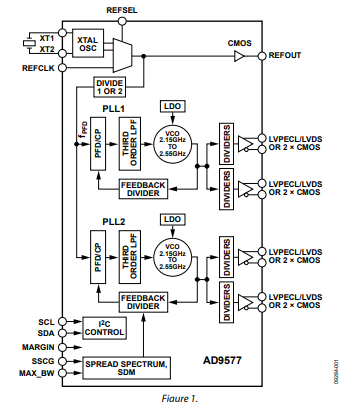

AD9577帶雙路PLL、擴(kuò)頻和余量微調(diào)功能的時(shí)鐘發(fā)生器技術(shù)手冊(cè)

FPGA是什么?應(yīng)用領(lǐng)域、差分晶振作用及常用頻率全面解析

基于FPGA的數(shù)字時(shí)鐘設(shè)計(jì)

xilinx FPGA IOB約束使用以及注意事項(xiàng)

使用DS90CR286A輸入穩(wěn)定的40M差分時(shí)鐘,輸出時(shí)鐘時(shí)有時(shí)無(wú),為什么?

請(qǐng)問(wèn)ADC32xx的時(shí)鐘由FPGA直接輸出嗎?

如果用FPGA采集AD1672,如何保障FPGA時(shí)鐘同1672時(shí)鐘一致?

ADS58C48的輸出給FPGA的時(shí)鐘怎樣產(chǎn)生的,是只要有輸入時(shí)鐘,就有輸出時(shí)鐘嗎?

時(shí)序約束一主時(shí)鐘與生成時(shí)鐘

FPGA如何消除時(shí)鐘抖動(dòng)

簡(jiǎn)述時(shí)鐘抖動(dòng)的產(chǎn)生原因

差分時(shí)鐘驅(qū)動(dòng)器和終端

簡(jiǎn)述FPGA時(shí)鐘約束時(shí)鐘余量超差解決方法

簡(jiǎn)述FPGA時(shí)鐘約束時(shí)鐘余量超差解決方法

評(píng)論