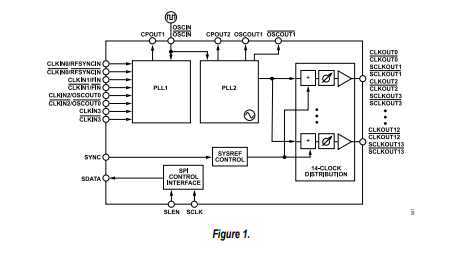

SC6302是一款兼容HMC7044的高性能雙環(huán)路整數(shù)、小數(shù)分頻抖動(dòng)衰減器,能夠執(zhí)行頻率轉(zhuǎn)換、選擇參考信號(hào)并生成超低相位噪聲的時(shí)鐘提供給并行或串行(JESD204B)接口的高速數(shù)據(jù)轉(zhuǎn)換器。SC6302提供14路低噪聲且可配置的輸出,可以靈活地匹配RF收發(fā)器系統(tǒng)中的許多不同器件接口,比如數(shù)據(jù)轉(zhuǎn)換器、本振、發(fā)送/接收模塊、FPGA和數(shù)字前端(DFE)ASIC。

SC6302可產(chǎn)生最多7對(duì)DCLK和SYSREF,符合JESD204B接口要求。該器件具有出色的串?dāng)_、頻率隔離以及雜散性能,支持單端和差分輸出頻率。DCLK和SYSREF時(shí)鐘輸出可配置為不同的輸出信號(hào)標(biāo)準(zhǔn),如CML、LVDS、LVPECL和LVCMOS。

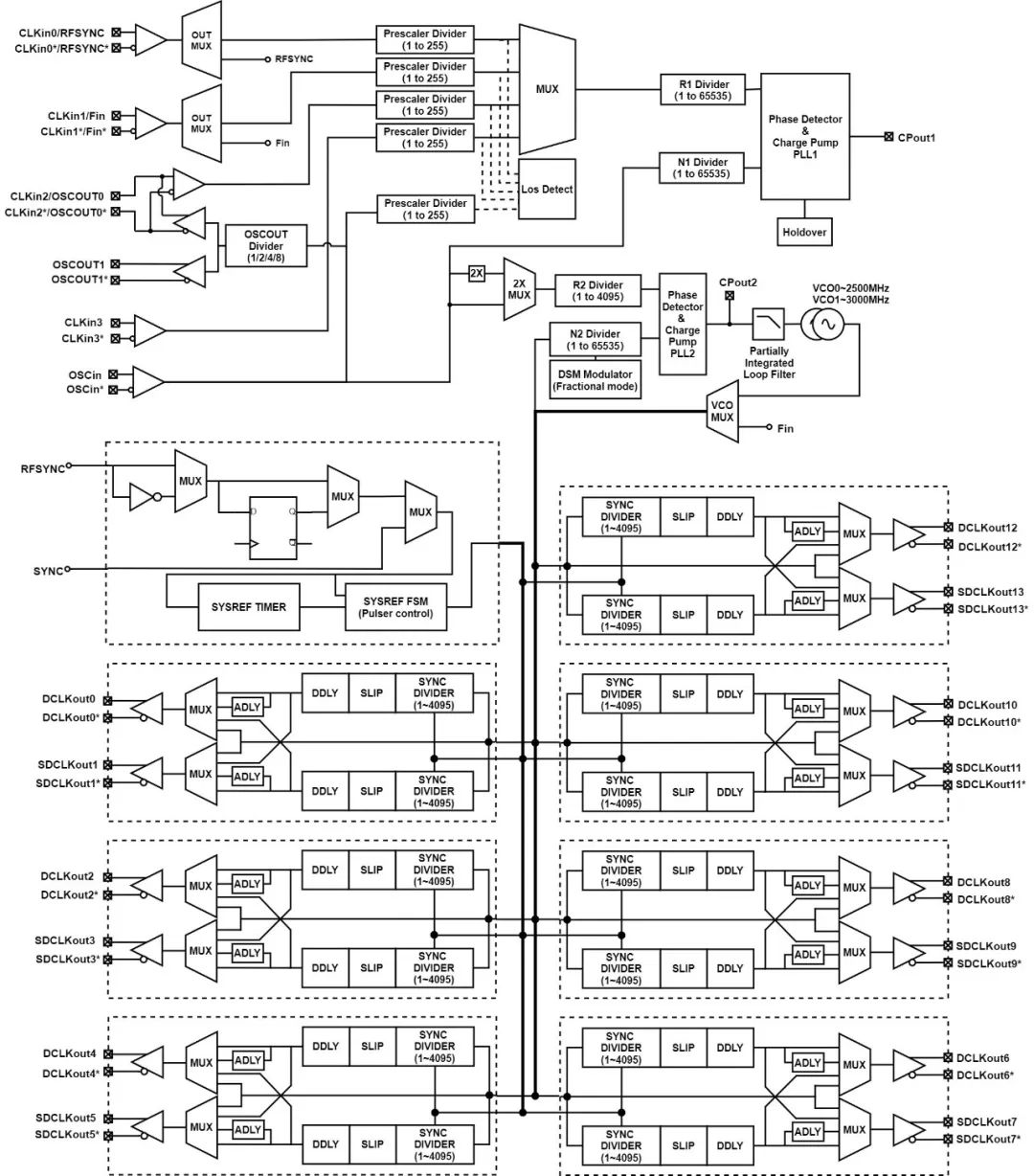

SC6302功能模塊示意圖

主要性能:

?支持JEDEC JESD204B

?超低RMS抖動(dòng)

48fs RMS Jitter(12kHz到20MHz)@2457.6M

底噪:-153dBc/[email protected]

?PLL2可提供多達(dá)14路差分時(shí)鐘

最多7個(gè)SYSREF時(shí)鐘

時(shí)鐘最大輸出頻率3.2GHz

支持LVPECL,LVDS,CML等輸出接口

?支持最多2個(gè)緩沖壓控振蕩器(VCXO)輸出

?信號(hào)丟失(LOS)檢測(cè)和無(wú)中斷參考切換

?4 個(gè)GPIO報(bào)警/狀態(tài)指示器

?支持最高3200MHz的外部VCO輸入

?工作溫度:-40℃到85℃

?工作電壓:3.15V到3.45V

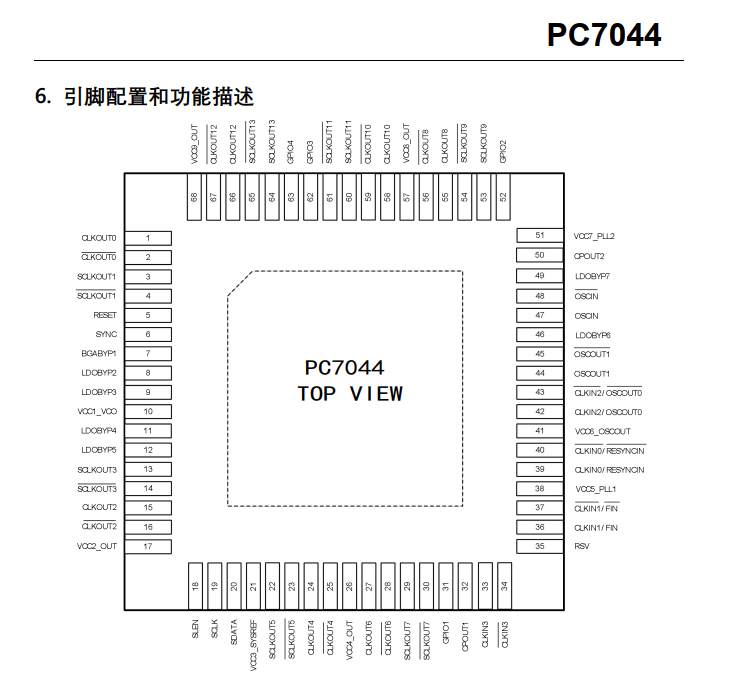

?QFN-68封裝

應(yīng)用場(chǎng)景:JESD204B時(shí)鐘產(chǎn)生、無(wú)線基礎(chǔ)設(shè)施(多載波GSM、LTE、W-CDMA)、數(shù)據(jù)轉(zhuǎn)換器時(shí)鐘、微波基帶卡、相控陣參考分配

注:如涉及作品版權(quán)問(wèn)題,請(qǐng)聯(lián)系刪除。

-

衰減器

+關(guān)注

關(guān)注

4文章

717瀏覽量

34952 -

消除器

+關(guān)注

關(guān)注

0文章

52瀏覽量

8815

發(fā)布評(píng)論請(qǐng)先 登錄

HMC7044外參考時(shí)鐘切換失敗的原因?

替代HMC7044超低噪高性能時(shí)鐘抖動(dòng)消除器支持JESD204B

請(qǐng)問(wèn)HMC7044鎖相環(huán)可以配出8路2.5G,相位可調(diào)的時(shí)鐘嗎?

請(qǐng)問(wèn)HMC7044的環(huán)路帶寬能用什么工具來(lái)仿真?

HMC7044時(shí)鐘輸出不穩(wěn)定

hmc7044使用外部VCO時(shí)鐘輸入時(shí),如何使得時(shí)鐘能夠相位對(duì)齊 ?

AD9172參考板上7044給出的時(shí)鐘電平是什么呢?

AD9524:帶6路差分或13路LVCMOS輸出的抖動(dòng)凈化器和時(shí)鐘發(fā)

HMC7044: 帶 JESD204B 接口的高性能、3.2 GHz、14 路輸出抖動(dòng)衰減器

UG-826:評(píng)估HMC7044雙環(huán)時(shí)鐘抖動(dòng)清除器

HMC7044B支持JESD204B和JESD204C的高性能、3.2GHz、14輸出抖動(dòng)衰減器技術(shù)手冊(cè)

PC7044高性能時(shí)鐘抖動(dòng)消除器支持JESD204B 時(shí)鐘生成

核芯互聯(lián)推出新一代高性能時(shí)鐘抖動(dòng)消除器CLF7044

14路差分輸出時(shí)鐘抖動(dòng)消除器SC6302,兼容HMC7044

14路差分輸出時(shí)鐘抖動(dòng)消除器SC6302,兼容HMC7044

評(píng)論