概述

HMC7044B 是 [HMC7044]的修訂版本,是一款高性能、雙環路、整數 N 抖動衰減器,能夠為具有并行或串行(JESD204B 和 JESD204C 類型)接口的高速數據轉換器執行參考選擇和超低相位噪聲頻率生成。在 HMC7044B 中,溫度和電源電壓等邊緣情況下的輸出相位對齊得到了改善。HMC7044B 具有兩個整數模式 PLL 和重疊片上 VCO,它們可通過 SPI 選擇,具有分別約 2.5 GHz 和 3 GHz 的寬調諧范圍。該設備旨在滿足 GSM 和 LTE 基站設計的要求,并提供廣泛的時鐘管理和分配功能,以簡化基帶和無線電卡時鐘樹設計。HMC7044B 提供 14 個低噪聲和可配置輸出,可靈活地與許多不同的組件(包括數據轉換器、現場可編程門陣列 (FPGA) 和混頻器本振 (LO))連接。

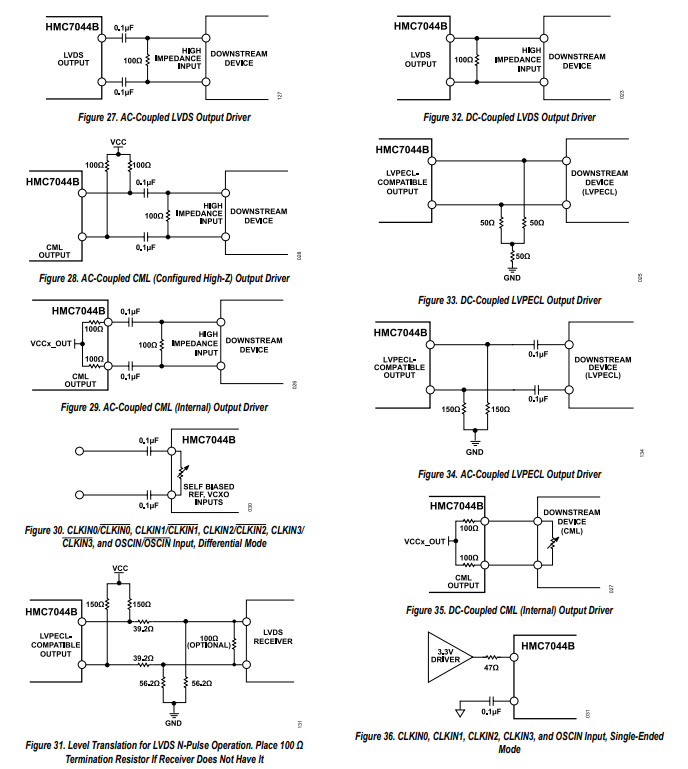

HMC7044B 的 DCLK 和 SYSREF 時鐘輸出可配置為支持信號標準,例如 CML、LVDS、LVPECL 和 LVCMOS,以及不同的偏置設置,以抵消不同的電路板插入損耗。

數據表:*附件:HMC7044B支持JESD204B和JESD204C的高性能、3.2GHz、14輸出抖動衰減器技.pdf

應用

- JESD204B 和 JESD204C 時鐘產生

- 蜂窩基礎設施(多載波 GSM、LTE、W-CDMA)

- 數據轉換器時鐘同步

- 微波基帶卡

- 相位陣列參考分布

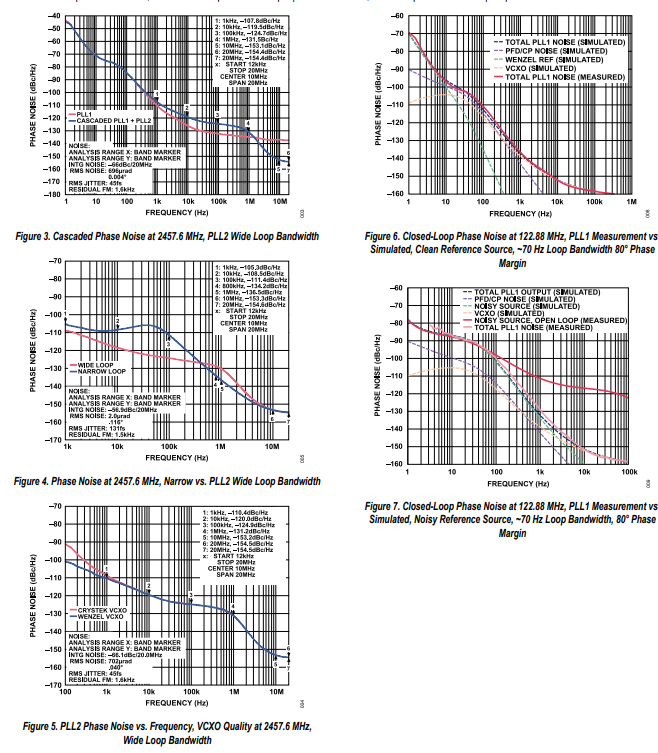

特性 - 超低均方根抖動:2457.6 MHz 時典型值為 44 fs(12 kHz 至 20 MHz)

- 本底噪聲:2457.6 MHz 時為 ?156 dBc/Hz

- 低相位噪聲:800 kHz、983.04 MHz 輸出時為 ?141.7 dBc/Hz

- 來自 PLL2 的最多 14 個 LVDS、LVPECL 或 CML 類型設備時鐘 (DCLK)

- 最大 CLKOUTx 和 SCLKOUTx 頻率高達 3200 MHz

- JESD204B 和 JESD204C 兼容系統參考 (SYSREF) 脈沖

- 窄帶,雙核心 VCO

- 25 ps 模擬和 ? VCO 周期數字延遲,可在每個 14 個時鐘輸出通道上獨立編程

- SPI 可編程相位噪聲與功耗

- SYSREF 有效中斷可簡化 JESD204B 和 JESD204C 同步

- 最多 2 個緩沖壓控晶體振蕩器 (VCXO) 輸出

- LVDS、LVPECL、CMOS 和 CML 模式下最多 4 個輸入時鐘

- 頻率保持模式可維持輸出頻率

- 信號丟失 (LOS) 檢測和無中斷參考切換

- 4× GPIO 警報/狀態指示器,用于確定系統的健康狀況

- 外部 VCO 輸入支持高達 6000 MHz

- 板載調節器可實現優秀的 PSRR

- 10 mm × 10 mm 68 引腳 LFCSP 封裝

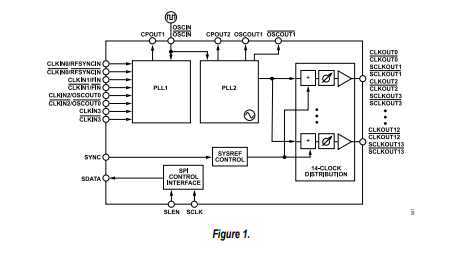

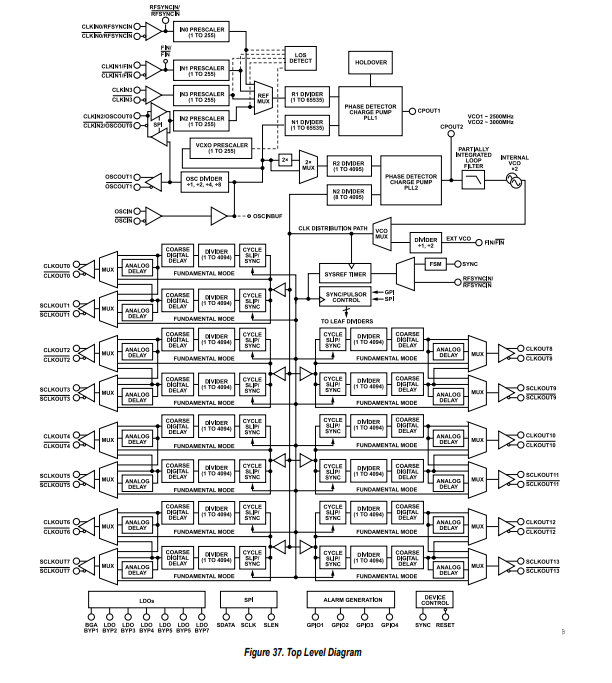

框圖

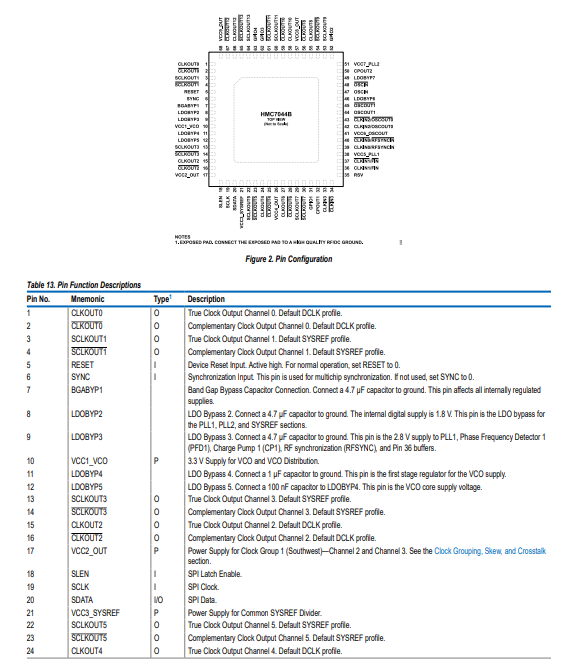

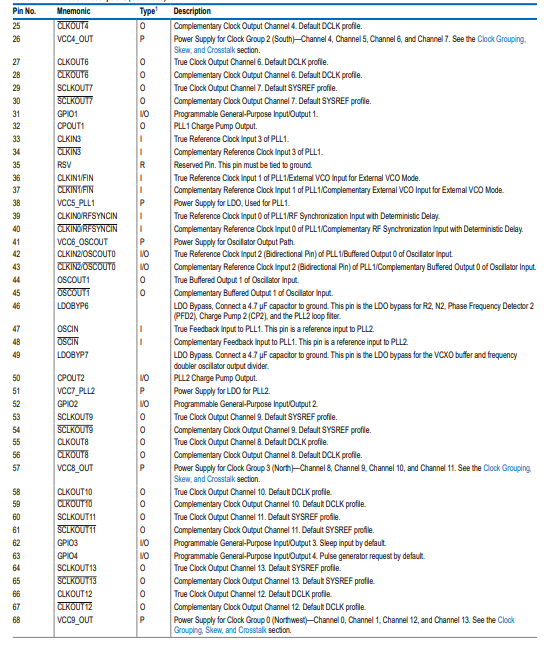

引腳配置描述

典型性能特征

典型應用電路

詳細框圖

-

衰減器

+關注

關注

4文章

717瀏覽量

34954 -

數據轉換器

+關注

關注

1文章

374瀏覽量

28718 -

環路

+關注

關注

0文章

51瀏覽量

12214

發布評論請先 登錄

替代HMC7044超低噪高性能時鐘抖動消除器支持JESD204B

JESD204B的系統級優勢

JESD204B串行接口時鐘的優勢

JESD204C的標準和新變化

如何采用系統參考模式設計JESD204B時鐘

HMC7044: 帶 JESD204B 接口的高性能、3.2 GHz、14 路輸出抖動衰減器

LTC6952:超低抖動、4.5 GHz PLL,帶11個輸出和JESD204B/JESD204C支持數據表

LTC6953:超低抖動、4.5 GHz時鐘分配器,帶11個輸出和JESD204B/JESD204C支持數據表

AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet

從JESD204B升級到JESD204C時的系統設計注意事項

JESD204B使用說明

LTC6953具有11個輸出并支持JESD204B/JESD204C協議的超低抖動、4.5GHz時鐘分配器技術手冊

HMC7044B支持JESD204B和JESD204C的高性能、3.2GHz、14輸出抖動衰減器技術手冊

HMC7044B支持JESD204B和JESD204C的高性能、3.2GHz、14輸出抖動衰減器技術手冊

評論