前面一篇文章中,已經詳細的分析了引導濾波的理論,公式的推導,以及和雙邊濾波的對比分析,即在邊緣的處理上雙邊濾波會引起人為的黑/白邊。我們已經知道何博士引導濾波的優秀之處,那么本篇文章,我帶你推演,如何用FPGA并行高速運算,最小的代碼實現實時的引導濾波算法。

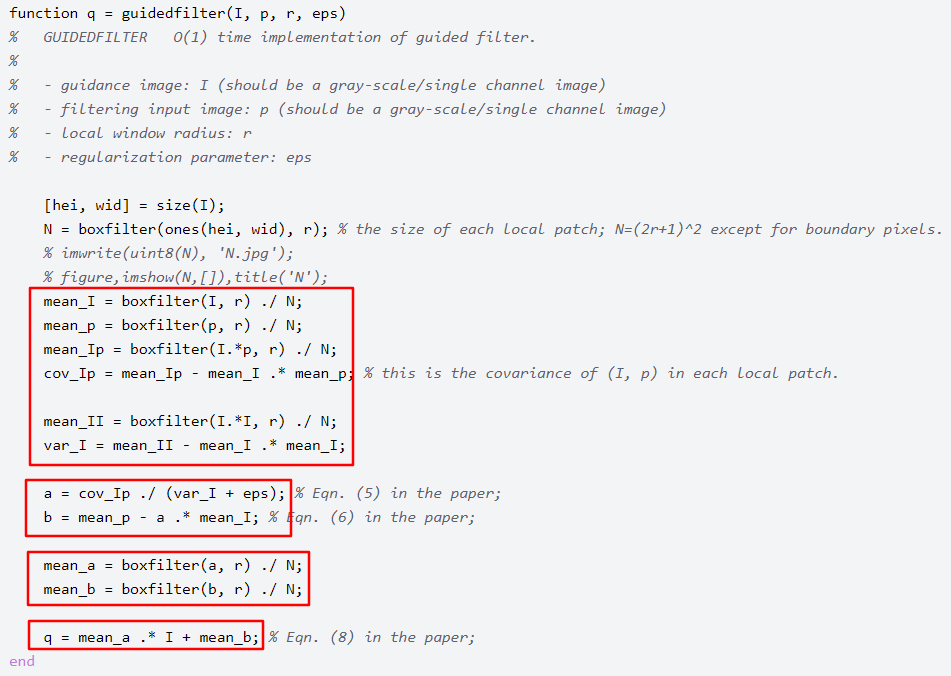

首先,給出上篇中最后的matlab 引導濾波的代碼,如下所示。

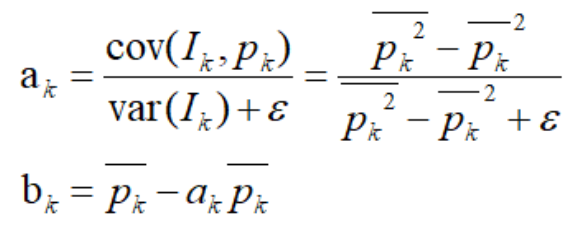

其中框框中為主要的計算過程,下一圖為計算a/b的最后的公式(引導圖=本身)。

雙邊濾波由于其只是在空間距離及像素相似度上進行權重計算,加權濾波,相對算法不是特別復雜,FPGA也易于實現(某司的USB工業相機2D濾波就是雙邊濾波),但是確實效果上不如引導濾波,那么引導濾波FPGA計算真有那么難嗎?為此我翻閱了一些資料,也從頭到尾推到計算了一遍,略有所成,出來和大家分享下。

在Matlab/C的加速中,引導濾波采用了盒式濾波的方式去加速,將運算復雜度從O(MN)的降低到了O(4),其方法就是先計算當前像素到原點像素組成的矩形區域的和/平方和等,對于線程的Matlab/C而言確實有很大的加速作用,相關的文章可以參考如下,對于軟件加速而言還是很不錯:

https://www.cnblogs.com/lwl2015/p/4460711.html

于是網上就有了一篇所謂的采用FPGA進行引導濾波加速的專利,鏈接如下:

https://www.doc88.com/p-4377429794731.html?r=1

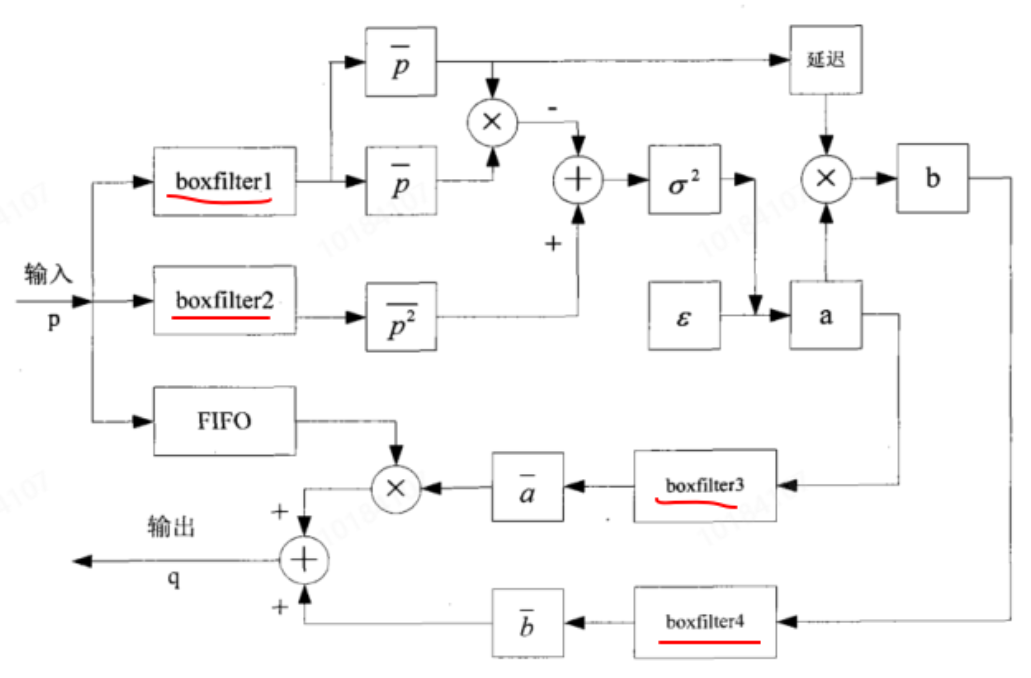

另附上架構實現圖,但我估計這幾個小朋友還沒有想明白boxfilter是怎么回事,生搬硬套軟件boxfilter加速的思維嘛???

圖中,計算均值,平方均值,a的均值,b的均值采用了4個boxfilter,也就是說如果輸入1280*720的圖像,那就需要緩存4個那么大地址空間的區域來存儲中間變量,這顯然是不適合FPGA加速運算的啊。FPGA的意義在于高速并行技術,盡可能的避免沖入進入緩存,而是以Pipeline的方式流水線完成運算,實現真正低延時+實時處理的目標。

所以為什么不能流水線完成所有的計算操作呢?

不服來戰,沒有啥難度的……下面開始我的表演。

【第一步】

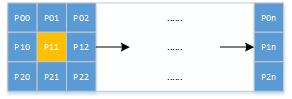

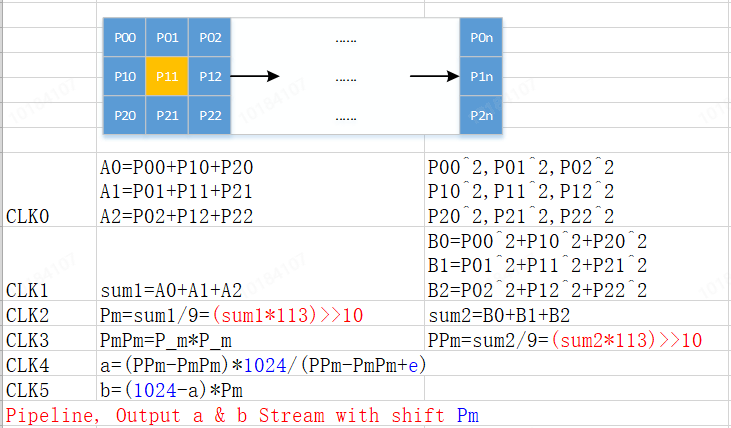

以3*3的濾波為例(這里的引導圖都是原圖),按行從傳感器或者DDR中讀取原圖,采用移位寄存后得到3*3的矩陣行,如下所示:

如上圖中,以P00-P22為例,這9個像素,我們可以通過計算得均值,以及平方的均值,緊接著繼續計算得到a與吧,詳見下圖,其中相關的參數定義如下:

P原始圖像像素集

Pm以當前像素為中心的3*3像素的均值

PPm以當前像素為中心的3*3像素平方的均值

sum1以當前像素為中心的3*3像素的和

sum1以當前像素為中心的3*3像素平方的和

a以當前像素為中心計算的參數a

b以當前像素為中心計算的參數b

am以當前像素為中心的3*3像素的a均值

bm以當前像素為中心的3*3像素的b均值

從上圖可知,通過三行組成的矩陣,以流水線方式,最快用了6個時鐘得到了參數a與b;

由于全圖流水線運行,因此從第6個時鐘開始,將持續的輸出每一個像素對應的a與b,等同于我們通過這一階段的實現方式,得到了參數a/b陣列。

另外,上圖中可知,除以9的運算我已經默默轉換為乘法與移位,clk4中將涉及到的小數點,已經提前擴大了1024倍,同等的b中也做了變更(紅/藍色字體),這就是FPGA定點化的加速的方式。

再者,由于最后的計算還需要P的參與,因此上述步驟中,需要將輸入的原始圖像進行移位延時,最終能和后續am/bm對齊。

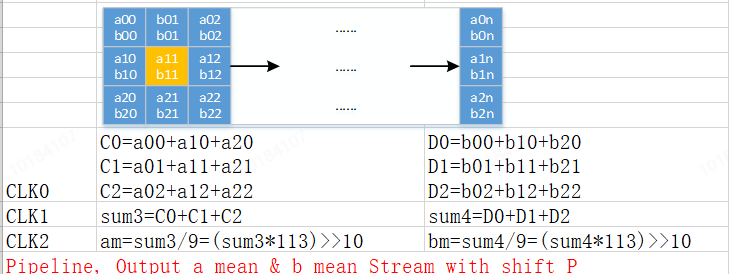

【第二步】

接下來,進一步計算am與bm,這個就簡單的多了,類似第一步,直接緩存3行得到3*3的矩陣行,通過加權后得到am與bm。這個過程中am與bm的計算可以完全并行,每個am/bm的計算耗時3個時鐘。

詳見下圖計算流:

【第三步】

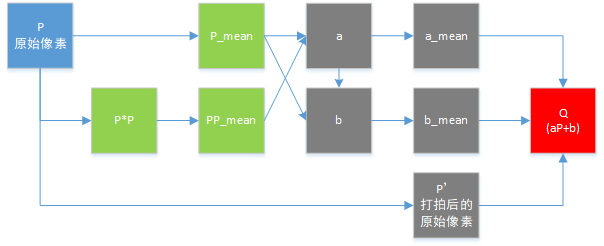

此時我們已經同時得到了am,bm,以及通過移位delay后和am/bm對齊的P,那么直接套用公式,我們就可以計算出每一個像素濾波后的值:

即輸出Q=(am*P+bm)》》10

這里還需要右移10bit,是因為前面第一步中,由于涉及到了小數,我們提前進行了1024倍的擴大,來減少計算誤差的損失。

至此,流水線操作,沒有使用boxfilter,沒有將數據回寫入DDR,我們采用了若干行line buffer的形式,完成了實時引導濾波的FPGA加速實現。

整體流程再梳理一下,相關的依賴以及流水方式,如下圖所示,應該可以看的更明白。其中綠色為第一步計,灰色為第二步計算,紅色為最后一步計算。

所以,這就是FPGA并行加速運算的價值與意義,按照我的實現方式,可以用最小的代碼實現實時的引導濾波,甚至連低端的EP4CE6E都不是問題。

同樣一個算法,可以有n種實現方式,你甚至可以把算法挪到MPSOC的PS中執行,然后忍受龜速的同時你可能還會抱怨FPGA跑的慢,CPU性能不足之類的,但是永遠不要忘記,架構的意義。正如軟件的優化,其實很多時候,并不是算法本身不行,而是你對系統底層,對計算優化的能力不行。

為什么我喜歡用FPGA加速,因為每一個門級電路,以何種并行度何種方式進行計算,一切都可以在我的掌控之中。

所以當年我說過一句話:掌握了FPGA,你便掌握了整個世界。

至此,從均值濾波到中值濾波、高斯濾波、雙邊濾波、引導濾波這些通用的2D降噪算法,我都已經通過公眾號/知識星球/博客的方式,從原理到FPGA加速實現闡述明白。

如果在這之間有任何疑問,或者我有什么不到之處的,歡迎以各種方式來跟我討論(伸手黨麻煩出門右轉)。

謝謝大家!

編輯:jq

-

FPGA

+關注

關注

1643文章

21966瀏覽量

614151 -

cpu

+關注

關注

68文章

11037瀏覽量

216015 -

濾波

+關注

關注

10文章

679瀏覽量

57159

原文標題:基于FPGA的引導濾波并行加速實現 推演

文章出處:【微信號:sim_ol,微信公眾號:模擬在線】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

進群免費領FPGA學習資料!數字信號處理、傅里葉變換與FPGA開發等

如何使用FPGA驅動并行ADC和DAC芯片,使用不同編碼方式的ADC與DAC時的注意事項

如何用FPGA并行高速運算實現實時的引導濾波算法

如何用FPGA并行高速運算實現實時的引導濾波算法

評論