高速并行總線的工作原理及其具體類型是一個涉及硬件技術和數據傳輸的復雜話題。以下是對高速并行總線工作原理的概述以及幾種常見的高速并行總線的介紹。

高速并行總線的工作原理

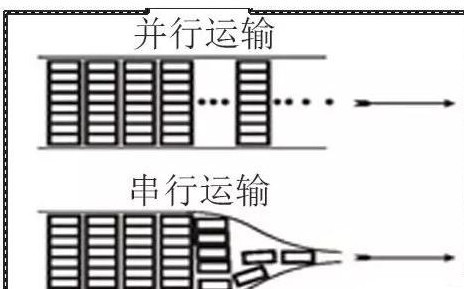

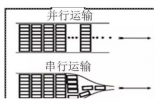

高速并行總線的工作原理主要涉及多個數據通道的同時傳輸。與串行總線相比,并行總線在同一時間內能夠傳輸多個數據位,從而提高了數據傳輸的速率。這種并行傳輸方式通常通過一組數據線來實現,每條線傳輸數據的一個位(bit)。為了確保數據的同步和完整性,還可能需要額外的控制線和時鐘信號線。

并行總線的工作原理可以概括為以下幾個步驟:

- 數據分割 :發送端將數據按照一定的位寬分割成多個數據位,每個數據位通過不同的數據線同時傳輸。

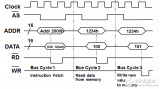

- 同步控制 :使用時鐘信號或其他同步機制來確保接收端能夠正確地接收和重組這些并行傳輸的數據位。

- 傳輸與接收 :數據在并行總線上同時傳輸,接收端則同時接收這些數據位,并按照一定的規則進行重組,以恢復原始數據。

- 錯誤檢測與校正 :在傳輸過程中,可能會遇到噪聲、干擾等問題,導致數據出錯。因此,并行總線通常需要實現某種形式的錯誤檢測與校正機制,以確保數據的準確性。

高速并行總線的類型

高速并行總線有多種類型,每種類型都有其特定的應用場景和優勢。以下是一些常見的高速并行總線:

- PCI(Peripheral Component Interconnect)總線

- 簡介 :PCI總線是早期計算機系統中廣泛使用的一種并行總線標準。它采用32位或64位數據傳輸,具有較高的數據傳輸速率和即插即用等特性。

- 特點 :支持多個設備同時連接,具有高速緩存技術,提高了數據傳輸速度。然而,隨著技術的發展,PCI總線逐漸被更先進的總線標準所取代。

- AGP(Advanced Graphics Port)總線

- DDR(Double Data Rate)總線

- 簡介 :DDR總線是一種用于內存模塊的高速并行總線標準。DDR總線通過在時鐘信號的上升沿和下降沿都傳輸數據,實現了雙倍的數據傳輸速率。

- 特點 :DDR總線具有較高的數據傳輸速率和較低的功耗,廣泛應用于計算機內存系統中。隨著技術的發展,DDR總線已經發展到了多個版本(如DDR2、DDR3、DDR4等),每個版本都在前一代的基礎上進行了改進和優化。

- 其他高速并行總線

從第一代DDR 開始,一直到即將推出的第五代的DDR,數據傳輸速率在一直在不斷增加,同時功耗及供電電壓在不斷降低。DDR系統要在這種越來越嚴苛的條件下還能保證良好的工作性能,就需要在信號完整性方面必須滿足特定的要求。保證整個系統的信號完整性不出問題對系統的正常工作而言非常關鍵, 或者說只有保證整個系統的信號完整性不出問題才能確保不同廠商生產的器件整合在一起時還可以正常工作。那DDR總線在傳輸數據中會有哪些信號完整性問題呢?

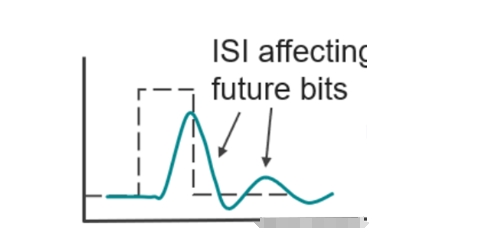

ISI

碼間干擾( Inter Symbol Interference, ISI)是指,當信號通過實際信道時,信號的帶寬變窄,同時信號的上升邊、下降邊變長。因此單位脈沖響應會變寬,即一個比特位所占有的時間會延長,并產生拖尾,如圖所示。

這樣接下來的比特位就會受到之前比特位的拖尾的影響。一個比特位可能會受到多個比特位的拖尾的影響,這個比特位的實際電壓值就等于本身的電壓值與諸多拖尾的電壓值的疊加值,這樣對該比特的電壓值就有可能產生誤判,導致本來是低電壓的比特位判定為高電壓,本來是高電壓的比特位判定為低電壓。

可以看出ISI產生的原因是單位脈沖響應的延展。而單位脈沖響應之所以產生了延展主要因為兩點,一是在信道上信號中的高頻部分和低頻部分的傳輸速度不一致,高頻部分的傳輸速度要大于低頻部分,造成信號在時域上的展寬,這種現象我們稱之為色散。二是在信道中,信號中高頻部分的衰減要大于低頻部分,這是因為信道的插入損耗隨著頻率的增加而變大,這也會造成信號在時域中的展寬。

同時,ISI和信道中所傳輸的具體碼型也有關系,傳輸的碼型不同,產生的ISI也會不同。由前面的解釋可以知道,當前比特位所受到的ISI與其前后的幾個比特位都有關系,因此不同的碼型會使邊沿變快或者變慢,導致其眼圖有多個交叉點存在。

總結

高速并行總線通過多個數據通道的同時傳輸來提高數據傳輸速率,廣泛應用于計算機系統和各種電子設備中。然而,隨著技術的發展和串行總線技術的普及,許多傳統的高速并行總線標準已經逐漸被更先進的串行總線標準所取代。這主要是因為串行總線在數據傳輸速率、信號完整性、功耗和布線復雜度等方面具有更多的優勢。

-

驅動器

+關注

關注

54文章

8637瀏覽量

149115 -

數據傳輸

+關注

關注

9文章

2005瀏覽量

65724 -

圖形處理

+關注

關注

0文章

46瀏覽量

13962 -

并行總線

+關注

關注

0文章

30瀏覽量

13650

發布評論請先 登錄

高速并行總線互連

什么是基于FPGA的ARM并行總線?

高速并行總線信號完整性測試技術

高速并行總線信號完整性測試技術

并行總線有哪些?串行總線有哪些?

并行總線是什么?(并行總線協議介紹)

基于FPGA的ARM并行總線和端口設計

高速并行總線的工作原理是什么 高速并行總線有哪些

高速并行總線的工作原理是什么 高速并行總線有哪些

評論