隨著空空導彈高速圖像信息處理板上DSP、FPGA等大規模數字集成電路的廣泛應用,信號的頻率也越來越高,圖像信息處理板出現電源壓降較大的問題。

頻率較低時,可將電源和地作為一個完整的參考平面,電源壓降較小。但高頻時,由于分布電感ESL的影響,電源、地平面相當于一個諧振腔,具有諧振特性。

電源平面其實可看成是由較多電感和電容構成的網絡,也可看作是一個共振腔,在一定頻率下,這些電容和電感會發生諧振現象,從而影響電源層的阻抗。隨著頻率的增加,電源阻抗是不斷變化的,尤其是在并聯諧振效應顯著的時候,電源阻抗也隨之明顯,因此在瞬間電流通過時便會產生一定的電壓降和電壓擺動。

而大部分數字電路器件對電源波動的要求在正常電壓的±5%范圍之內,因此造成數字電路器件不能正常工作。

本文將電源完整性理論和PCB設計實例相結合,在諧振、電源阻抗、避免重要信號線跨越平面層分割、直流壓降等方面做了電源完整性方面的優化設計。

1

通過諧振分析優化印制板布局

諧振模式計算分析的是由PCB中電源和地的結構而可能引發的風險,包括疊層、板材以及地電分割等,目的是使印制電路板在所關注的頻率范圍內不發生諧振。

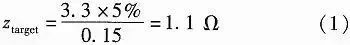

觀察PCB的諧振模式下的電壓分布,盡量避免將大電流IC放置在諧振位置或其附近位置。圖像信息處理板上電源和地的諧振圖,如圖1所示。

圖1 電源和地的諧振圖

從圖中可知,印制電路板右上角諧振較大,因此在印制電路板布局時大電流IC器件盡量避免放置在印制板的右上角。

2

降低電源阻抗優化電路設計

之前在EDA電子論壇看到過這樣一個內容:系統電源部分的好壞直接影響到系統的穩定性,甚至可能使得系統邏輯錯誤。一個低阻抗的電源分布系統是比較理想的,至少在整個系統的工作頻段內呈低阻抗,從而具有較小的壓降。

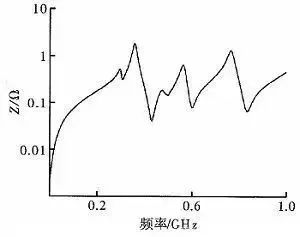

以圖像處理板上的FPGA為例,供電電源為3.3 V,電壓噪聲限為5%,最大瞬間電流為0.15 A,則設計的最大電源阻抗如式(1)所示

對FPGA的3.3 V電源做電源阻抗仿真,圖2所示為FPGA的3.3 V電源阻抗。

圖2 FPGA的3.3V電源阻抗

從圖中可看到,在357 MHz、765 MHz處諧振頻點阻抗較高,需要選擇合適的去耦電容,以改善電源阻抗特性。這里選取電容值為200 pF封裝為0603的電容作為FPGA的去耦電容,因為它的特征曲線與電源阻抗曲線峰值頻點一致,這樣可將電源阻抗的峰值降低。

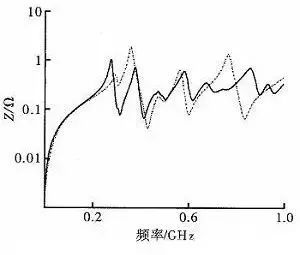

200 pF的去耦電容布局選擇在357 MHz諧振電壓波動最大的位置處,因在此處諧振比較明顯,同樣在728 MHz處諧振頻點電源阻抗也較高,因此再加上兩個62 pF電容后,電源阻抗如圖3實線所示,虛線為最初沒有加電容的電源阻抗。

圖3 最終優化后電源阻抗對比圖

從圖3中可看到,電源阻抗有了較大改善,滿足低于最大電源阻抗的要求。

3

避免高速信號線跨越平面層分割

電源和地分割、線寬以及過孔等都會造成PCB傳輸線的阻抗不連續,引起電源平面和地平面回流路徑不理想,造成電源完整性問題。

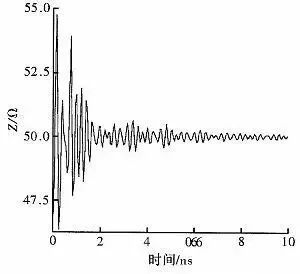

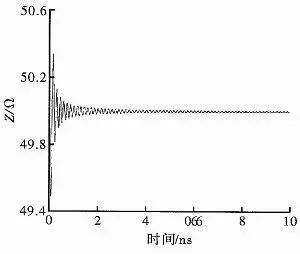

為得到更好的信號質量,可調節線寬和介質層的厚度以及電源和地的分割線來滿足特性阻抗的要求。以FPGA_CLK為例,在當前PCB中,其的傳輸線阻抗如圖4所示,阻抗在 43.5~54.7 Ω之間波動,波動過大。

圖4 FPGA_CLK傳輸線阻抗

為改善傳輸線特性,對PCB層疊做優化。通過調節線寬,介質層的厚度以及不要跨平面層分割等來滿足50 Ω特性阻抗的要求。

優化后的傳輸線阻抗如圖5所示。

圖5 優化后的傳輸線阻抗

FPGA_CLK在層疊結構優化后,傳輸線阻抗在49.5~50.5 Ω之間,滿足了阻抗匹配的要求。

電源地網絡和信號網絡不是割裂的,而是緊緊耦合在一起的,所以電源地的噪聲還會通過耦合影響信號線,或者輻射到外面,會產生EMI、EMC的問題。

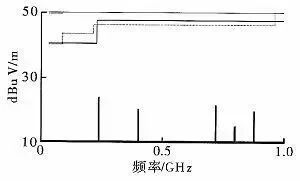

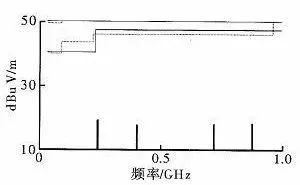

通過電磁輻射方面的對比,圖6為沒有優化時電磁輻射的波形,圖7為優化后電磁輻射的波形。

圖6 沒有優化電磁輻射圖

圖7 優化后電磁輻射圖

通過圖中對比,電磁輻射明顯降低。

4

直流壓降

在PCB設計中,由于平面層的分割,不理想的電流路徑和各種過孔信號線的分布,電源網絡的直流供電時常受到影響。直流壓降分析可顯示整個PCB上電流的流向、電路密度以及直流壓降等特性。

在產生3.3 V的芯片出口處設置電流源和電壓源,在印制板右上方放置電流源的探針和電壓源的探針。

可看到深色區域表示電流密度過大,在兩個DSP處紅色比較明顯,可減小隔離盤的大小,使電流通過,在3.3 V供電處可通過增大過孔的尺寸以及多打幾個過孔的方法使電流在幾個地方通過,以降低電流的密度。

再對其做電壓壓降仿真。

最低電壓為3.285 V,壓降為0.5%,滿足系統電壓波動在±10%要求。

5

結束語

電源完整性問題主要是由于去耦電容的設計不合理、回路影響嚴重、多電源/地平面的分割不好、地層設計不合理以及電流不均勻等問題引起的。

通過電源完整性仿真,找到這些問題,然后通過以下方法解決電源完整性問題:

通過調整PCB疊層線寬、介質層的厚度滿足特性阻抗的要求,調節疊層結構滿足信號線回流路徑短的原則,調整了電源/地平面的分割,避免了重要信號線跨分割的現象;

對印制板上用到的電源進行了電源阻抗分析,通過加入電容使其控制在目標阻抗之下;

在電流密度大的部分通過調整器件的位置,使電流從更寬的路徑通過。

原文標題:PCB上電源完整性僵局如何破?

文章出處:【微信公眾號:EDA365電子論壇】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

電源

+關注

關注

185文章

18391瀏覽量

256646 -

pcb

+關注

關注

4371文章

23520瀏覽量

410454

原文標題:PCB上電源完整性僵局如何破?

文章出處:【微信號:eda365wx,微信公眾號:EDA365電子論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

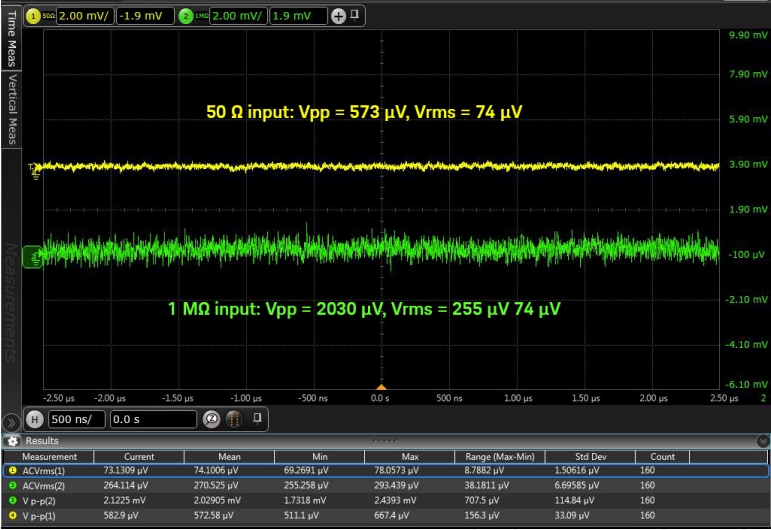

普源DHO3000系列示波器電源完整性測試

將電源完整性理論和PCB設計實例相結合

將電源完整性理論和PCB設計實例相結合

評論