在IEDM 2020上,英特爾展示了其基于nanoribbon板狀納米溝道的n/p型堆疊的器件,這種器件結構與IMEC研發制備的CFET結構近似,被認為是3nm之后晶體管結構的必然解決方案。

研究背景

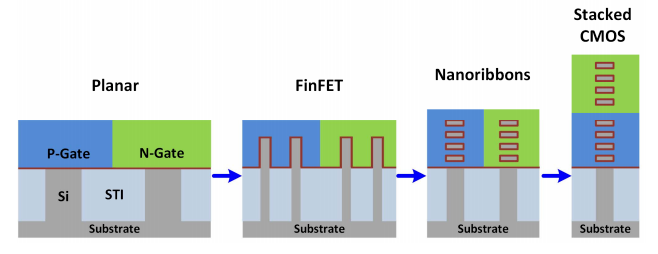

在先進邏輯集成電路的制造工藝進入10nm后,單純依靠縮小器件工藝單元尺寸已經無法獲得足夠的能效增益。在28nm向下前行的過程中,從平面CMOS工藝到FinFET工藝的轉變帶來了更強的溝道控制能力,同時縮小了柵極間距和工藝單元的高度。

而在nanoribbon*(以下簡稱NR)的加持下,對于溝道的控制能力進一步增強,并且可變的NR堆疊層數和NR寬度,可以允許更大的載流子通量,從而進一步提高單元密度。在NR基礎上,將nMOS和pMOS進行堆疊,可以進一步將摩爾定律推進到極限。

在IEEE IEDM 2020會議上,英特爾發布了基于NR的垂直堆疊CMOS結構的研究成果,這種結構與IMEC在VLSI國際會議上展示的CFET*的技術路線近似,都是在垂直方向上實現一個CMOS單元的構成,通過在y軸上同時堆疊pMOS和nMOS以縮小工藝單元的中心間距,實現晶體管面積的縮小。

*Nanoribbon:GAA環柵晶體管的一種形態,與nanosheet類似,同樣為片狀結構的溝道。

*CFET:Complementary Field Effect Transistor,是將nMOS和pMOS垂直堆疊的一種新型晶體管結構,通過將Contact Poly Pitch(PP)做到最小,極大地縮小了CMOS單元面積。

從平面CMOS晶體管結構到堆疊CMOS晶體管結構

該成果以“3-D Self-aligned Stacked NMOS-on-PMOS Nanoribbon Transistors for Continued Moore’s Law Scaling”為題發表,內容于2021年3月解禁,G. Dewey、E. Mannebach等28位英特爾研究人員共同完成了該成果,通訊作者為Cheng-Ying Huang。

研究內容

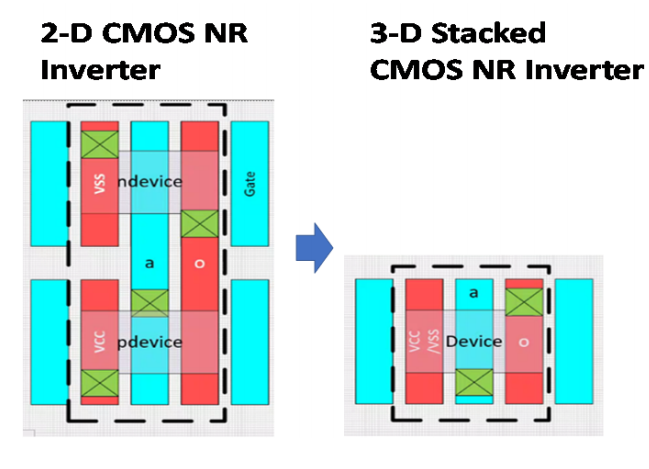

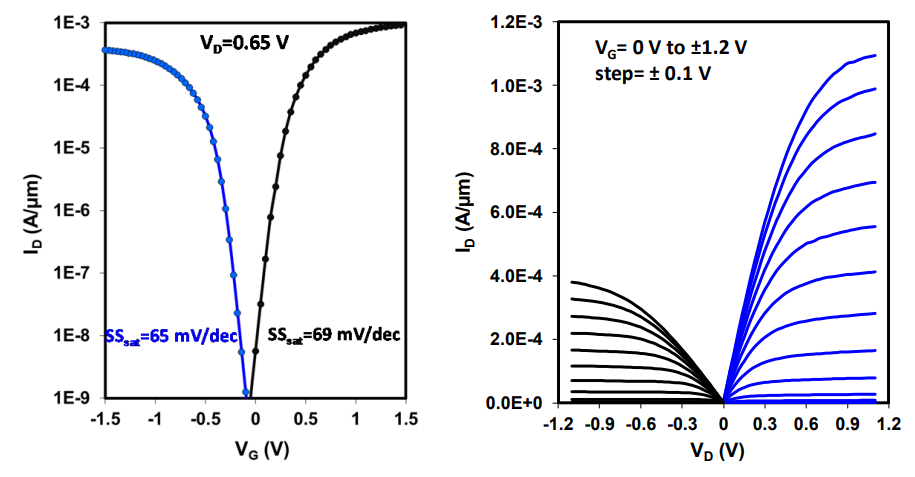

該成果展示了三維自對準*堆疊的nMOS-on-PMOS的NR結構晶體管,成功地在垂直方向上完成了CMOS工藝單元的集成,相比在平面上分別排布nMOS和pMOS的結構,可縮小50%的器件排布面積;該結構中上部的nMOS和底部pMOS均顯示出高導通性能和優秀的短溝道控制能力,在電特性測試中CMOS反相器也顯示出良好的電壓傳輸特性。英特爾的研究人員認為,這一新的器件結構將會延續摩爾定律的發展。

*自對準:制作大規模集成電路的一種重要工藝,可有效減少MOSFET中的寄生電容,提升電路工作頻率和速度。

n/p堆疊式的NR晶體管結構將節約50%的面積

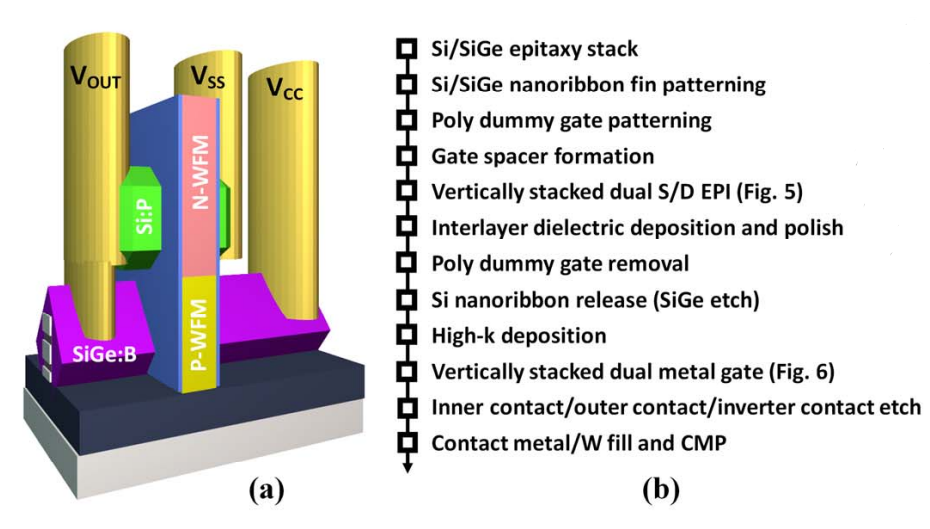

晶體管3D建模圖以及制造工藝流程

5層溝道堆疊結構的TEM形貌像

ID-VG特征曲線和ID-VD特征曲線,LG=75nm

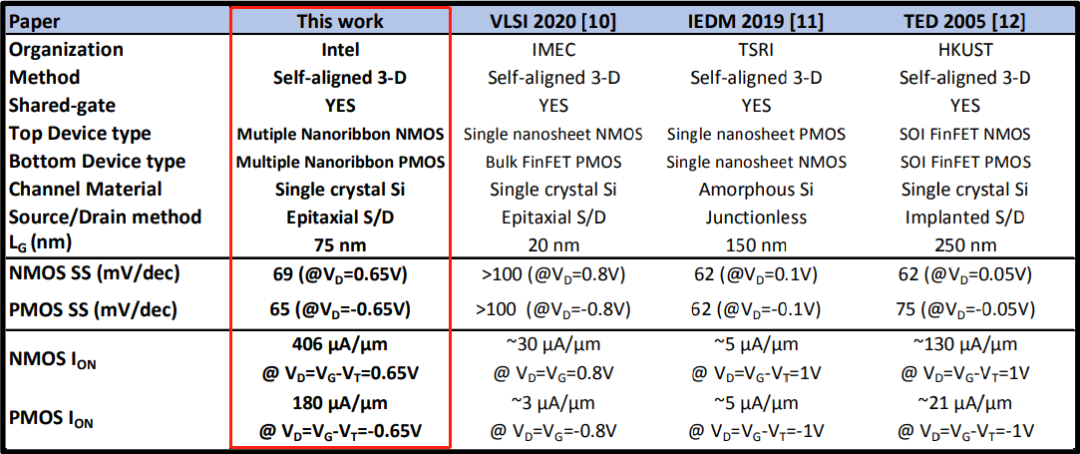

研究成果性能對比

前景展望

在過去的數年中英特爾受困于懸而未決的良率問題,技術節點停滯在14nm而更先進的10nm工藝則未能實現預期量產規模,使得一直以來的摩爾定律先鋒逐漸落后于臺積電。而在IEDM的新成果展示中,英特爾展示出了與IMEC的CFET技術路線類似的前沿研究成果,并喊出了“延續摩爾定律”的響亮口號。

根據英特爾公開的技術路線規劃,在5nm節點將會使用nanosheet或nanoribbon形態的GAA結構,本項成果作為GAA的再升級版本則可能在3nm或2nm量產,從具體技術參數來看,本項成果的柵長與對應節點的參數要求還有很大距離,恐怕僅僅是初步的技術原型,還有很多進一步的工作尚未完成。這會是英特爾王者歸來的助推劑,抑或是另一個久不落地的大衛星?讓我們拭目以待。

責任編輯:lq

-

英特爾

+關注

關注

61文章

10183瀏覽量

174167 -

晶體管

+關注

關注

77文章

9995瀏覽量

140966 -

堆疊

+關注

關注

0文章

37瀏覽量

16833

原文標題:科研前線 | 英特爾展示新型晶體管結構,摩爾定律的極限方案?

文章出處:【微信號:ICxpjm,微信公眾號:芯片揭秘】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

世紀大并購!傳高通有意整體收購英特爾,英特爾最新回應

下一代高速芯片晶體管解制造問題解決了!

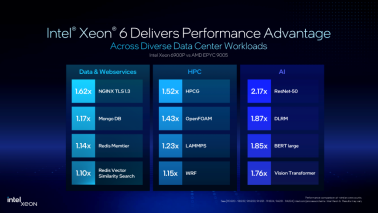

英特爾至強6:如何煉就數據中心“全能型選手”

英特爾進軍電動車powertrain域控,推出ACU U310

英特爾塑造未來出行:AI增強型軟件定義汽車

英特爾展示互連微縮技術突破性進展

英特爾推出全新英特爾銳炫B系列顯卡

英特爾為企業智能化發展注入新動力

英特爾聯合中科創達構建下一代智能座艙平臺

英特爾目標明年出貨1億臺AI PC

英特爾考慮出售Altera股權

英特爾股票分析:英特爾的困境能否結束?

英特爾展示了其基于nanoribbon板狀納米溝道的n/p型堆疊的器件

英特爾展示了其基于nanoribbon板狀納米溝道的n/p型堆疊的器件

評論