數據流模型化

本章講述Verilog HDL語言中連續賦值的特征。連續賦值用于數據流行為建模;相反,過程賦值用于(下章的主題)順序行為建模。組合邏輯電路的行為最好使用連續賦值語句建模。

7.1 連續賦值語句

連續賦值語句將值賦給線網(連續賦值不能為寄存器賦值),它的格式如下(簡單形式):assignLHS_target = RHS_expression ;例如,wire [3:0] Z, Preset, Clear; // 線網說明assign Z = Preset & Clear; //連續賦值語句連續賦值的目標為 Z,表達式右端為“ Preset & Clear”。注意連續賦值語句中的關鍵詞assign。連續賦值語句在什么時候執行呢 ?

只要在右端表達式的操作數上有事件 (事件為值的變化)發生時,表達式即被計算;如果結果值有變化,新結果就賦給左邊的線網。在上面的例子中,如果 P re s e t或C l e a r變化,就計算右邊的整個表達式。如果結果變化,那么結果即賦值到線網Z。連續賦值的目標類型如下:

1) 標量線網

2)。 向量線網

3) 向量的常數型位選擇4) 向量的常數型部分選擇5) 上述類型的任意的拼接運算結果下面是連續賦值語句的另一些例子:assgin BusErr = Parity| (One & OP) ;assign Z = ~ (A | B) & (C | D) & (E | F) ;只要A、B、C、D、E或F的值變化,最后一個連續賦值語句就執行。在這種情況下,計算右邊整個表達式,并將結果賦給目標 Z。

在下一個例子中,目標是一個向量線網和一個標量線網的拼接結果。wireCout, C i n ;wire [3:0] Sum, A, B;。 。 .assign{Cout, Sum} = A + B + Cin;因為A和B是4位寬,加操作的結果最大能夠產生 5位結果。左端表達式的長度指定為 5位(Cout 1位,Sum 4位)。

賦值語句因此促使右端表達式最右邊的 4位的結果賦給S u m,第5位(進位位)賦給C o u t。下例說明如何在一個連續賦值語句中編寫多個賦值方式。assgin M u x = (S = = 0)?

A : ‘bz, M u x = (S = = 1)?

B : ’bz, M u x = (S = = 2)?

C : ‘bz, M u x = (S = = 3)?

D : ’bz;這是下述4個獨立的連續賦值語句的簡化書寫形式。

assign M u x = (S = = 0)? A : ‘bz;assign M u x = (S = = 1)? B : ’bz;assign M u x = (S = = 2)? C : ‘bz;assign M u x = (S = = 3)? D : ’bz;

7.2 舉例

下例采用數據流方式描述1位全加器。

在本例中,有兩個連續賦值語句。這些賦值語句是并發的,與其書寫的順序無關。只要連續賦值語句右端表達式中操作數的值變化 (即有事件發生), 連續賦值語句即被執行。如果 A變化,則兩個連續賦值都被計算,即同時對右端表達式求值,并將結果賦給左端目標。

7.3 線網說明賦值

連續賦值可作為線網說明本身的一部分。這樣的賦值被稱為線網說明賦值。例如 :wire [3:0] S u m = 4‘b0;wire C l e a r = ’b1;wire A _ G T _ B = A 》 B, B_GT_A= B 》 A;線網說明賦值說明線網與連續賦值。說明線網然后編寫連續賦值語句是一種方便的形式。參見下例。wire Clear;assign Clear= ‘b1;等價于線網聲明e賦值:wire Clear= ’b1;不允許在同一個線網上出現多個線網說明賦值。如果多個賦值是必需的,則必須使用連續賦值語句。

7.4 時延

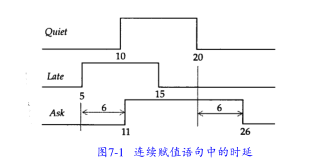

如果在連續賦值語句中沒有定義時延,如前面的例子,則右端表達式的值立即賦給左端表達式, 時延為0。如下例所示顯式定義連續賦值的時延。assign #6 Ask = Quiet | | L a t e;規定右邊表達式結果的計算到其賦給左邊目標需經過 6個時間單位時延。例如,如果在時刻5,L a t e值發生變化,則賦值的右端表達式被計算,并且 A s k在時刻11( = 5 +6)被賦于新值。圖7 - 1舉例說明了時延概念。

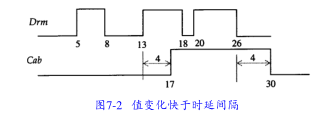

如果右端在傳輸給左端之前變化,會發生什么呢?在這種情況下,應用最新的變化值。下例顯示了這種行為:assign #4 Cab = Drm;圖7 - 2顯示了這種變化的效果。右端發生在時延間隔內的變化被濾掉。例如,在時刻 5,Dr m的上升邊沿預定在時刻9顯示在Cab上,但是因為Drm在時刻8下降為0,預定在Cab上的值被刪除。同樣, Drm在時刻1 8和2 0之間的脈沖被濾掉。這也同樣適用于慣性時延行為:即右端值變化在能夠傳播到左端前必須至少保持時延間隔;如果在時延間隔內右端值變化,則前面的值不能傳輸到輸出。

對于每個時延定義,總共能夠指定三類時延值:1) 上升時延2) 下降時延3) 關閉時延這三類時延的語法如下:

在第一個賦值語句中,上升時延、下降時延、截止時延和傳遞到 x的時延相同,都為 4。在第二個語句中,上升時延為4,下降時延為8,傳遞到x和z的時延相同,是4和8中的最小值,即4。在第3個賦值中,上升時延為 4,下降時延為8,截止時延為6,傳遞到x的時延為4 ( 4、8和6中的最小值)。在最后的語句中,所有的時延都為 0。上升時延對于向量線網目標意味著什么呢 ? 如果右端從非0向量變化到0向量,那么就使用下降時延。如果右端值到達z,那么使用下降時延;否則使用上升時延。

7.5 線網時延

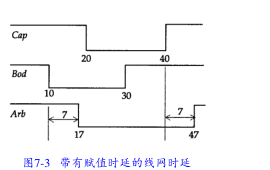

時延也可以在線網說明中定義,如下面的說明。wire #5 A r b;這個時延表明A r b驅動源值改變與線網A r b本身間的時延。考慮下面對線網 A r b的連續賦值語句:

assign # 2 Arb = Bod & Cap;

假定在時刻1 0,B o d上的事件促使右端表達式計算。如果結果不同,則在 2個時間單位后賦值給 A r b,即時刻1 2。但是因為定義了線網時延,實際對 A r b的賦值發生在時刻17( = 10 + 2 + 5)。圖7 - 3的波形舉例說明了不同的時延。圖7 - 4很好地描述了線網時延的效果。首先使用賦值時延,然后增加任意線網時延。如果時延在線網說明賦值中出現,那么時延不是線網時延,而是賦值時延。下面是 A的線網說明賦值,2個時間單位是賦值時延,而不是線網時延。w i r e #2 A = B - C; // 賦值時延

7.6 舉例

7.6.1 主從觸發器

下面是圖5 - 9所示的主從觸發器的Verilog HDL模型。

7.6.2 數值比較器

下面是8位(參數定義的)數值比較器數據流模型。

原文標題:Verilog入門-數據流模型化

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

Verilog

+關注

關注

28文章

1366瀏覽量

111810 -

HDL

+關注

關注

8文章

330瀏覽量

47820

原文標題:Verilog入門-數據流模型化

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

在testbench中如何使用阻塞賦值和非阻塞賦值

一文詳解Verilog HDL

淺談Verilog和VHDL的區別

Verilog HDL語言中連續賦值的特征

Verilog HDL語言中連續賦值的特征

評論