近日,美光發布了用于DRAM的新型1α制造工藝。并計劃首先將其用來制造DDR4和LPDDR4存儲器,并在之后將其用于生產他們所有類型的DRAM。如今,擴展DRAM已經變得異常困難。但據介紹,該制造技術有望顯著降低DRAM成本。這個神秘的“1α”會有多神奇?我們一起來看看。

芯片制造的目標就是縮小電路以在芯片上容納更多的晶體管或存儲單元。60年前,第一批芯片的元件——晶體管可以用肉眼看到。現在相同的組件只有幾納米寬。那是它的十億分之一!

更小的晶體管開關速度更快,能耗更少,而且,通過純粹的規模經濟,制造成本也更低。跳到我們最新的技術節點,它是當今世界上最先進的。它在性能、能效和制造成本方面都會有重大改進。

想象一下,如果汽車以同樣的速度進步的話。他們可以在一眨眼的功夫從0加速到60英里/小時,只需要幾滴燃料就可以環游地球。

現在,制造芯片這個事是復雜的。制造一個現代芯片需要一千多個獨立的過程和測量步驟——所有這些步驟都必須近乎完美。這些步驟是在先進的設備上完成,這些機器由數百家專業公司生產,使用超純材料,在巨大的潔凈室中進行,那里的空氣中顆粒比月球上的空氣還要少。

由于這種復雜性,行業往往遵循類似的節奏從一個節點到另一個節點。并通過芯片上最小的特征來引用它們。例如,在很久之前,我們還處于180納米節點,大約十年前,我們已在22納米節點上。

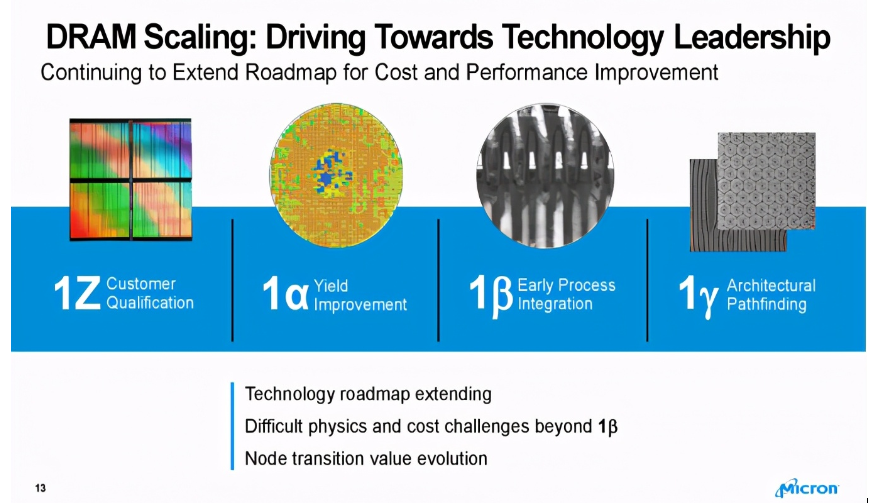

但是幾年前,在內存世界里發生了一件有趣的事情。我們不再討論確切的數字,而是開始使用像1x, 1y和1z這樣的術語。特別是DRAM,節點的名稱通常對應于存儲單元陣列中活動區域的一半間距的大小——“半間距”。至于1α,你可以把它看作是第四代的10nm級別,其半節距從10到19nm。當我們從1x納米到1y 1z和1α時,這個尺寸會變得越來越小。我們從1x開始,但隨著我們繼續縮小并命名下一個節點,我們到達了羅馬字母表的末尾。這就是為什么我們改用希臘字母α,β的緣故。

從尺寸的角度來看,我們說的小到底有多小?

芯片在直徑300mm的硅片上可一次制造數百個。每個芯片都有指甲蓋那么大。如今,一個晶體管在一個典型的存儲芯片上,能有著80億比特的存儲空間。

限制光刻

半導體行業每年或每隔二十年就會收縮設備。我們知道如何在只有一個原子厚的材料薄膜上進行刻蝕,我們也會有選擇地去除材料的能力。那么,現在有什么不同呢?

也許最困難的挑戰是定義晶圓片上的電路模式。第一部分叫做光刻(用光在石頭上寫字!)。它類似于前數碼攝影的過程,光線通過一個小的透明版的照片照射到光敏紙上。在我們的案例中,我們使用巴士大小的機器,通過放置在透明方形石英上稱為光掩模的模式照射深紫外光。但原理是一樣的。

這是一個物理問題。多虧了 “瑞利準則”,或者衍射極限,這讓人們認為不可能投射出一個小于所用光波長一半的特征的圖像。只是不可能制造出足夠銳利的光束來做出精確的圖案。在我們的例子中,波長是193nm,所以我們的工作遠遠低于衍射極限。

現在有一種新的光刻工具,它使用更小的32 nm波長的極紫外線(EUV),但由于一些復雜的原因,我們認為它還沒有準備好。其中一個原因是波長太短,光線不能穿過玻璃,所以傳統的光學透鏡不起作用。15年前,人們認為EUV光刻技術可以用于32納米節點。EUV的時代將會到來,但它不是1α在微米級別的正確解決方案。

“愚弄”光線,違背瑞利準則

我們使用許多技術來繞過衍射極限。第一種方法是修改光掩模上的圖案,使其形成尖銳的特征。目前最先進的技術被稱為計算光刻技術,它使用大量的處理能力從晶圓上所需的圖案有效地進行反向工程掩模。

第二是利用水對光的衍射比空氣小這一事實,使晶圓在水下暴露。實際上,我們用一滴水來取代最終鏡頭和晶圓片表面之間的氣隙。這種方法可以使我們達到40nm以下,這是一個很大的改進,但并不是一直都能成功。

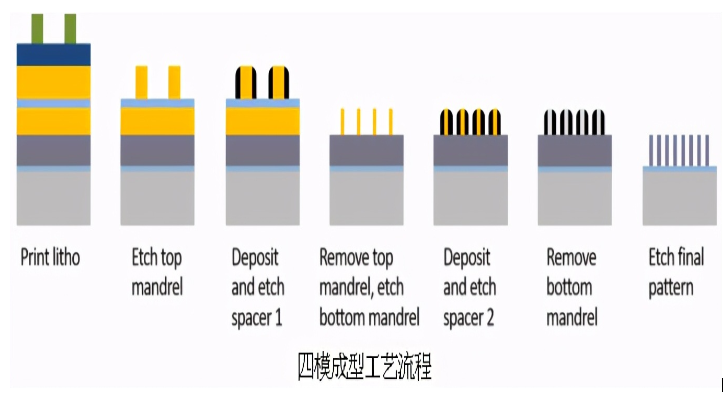

多重圖案

解決分辨率的方法是添加一系列非光刻步驟,神奇地將一個“大”特征變成兩個,成為四個特征,每個特征的大小都是原來的四分之一。有很多不同的方法可以同時實現這一點,但我必須指出,早在2007年,美光是第一個使用雙模式開發閃存的公司。

這樣簡化了很多工作,基本的想法是用步進器創造特征,在這些特征的側面涂上不同的材料,然后去掉原來的特征(sacrificial features)。得到Voilà -兩個半尺寸的功能!重復這個過程,我們有了所需的 1α的四個特征大小。

清洗和重復

現在我們知道我們可以精確地繪制出我們需要的微小特征,但我們離一個完整的模具還有很長的路要走,更不用說大批量生產了。我們只是為一層的功能做了輪廓,要知道每個芯片中有幾十層。自豪的是,我們可以精確地將層層對齊,這稱之為疊加。準確無誤地做到這一點是讓整個過程順利進行的關鍵。

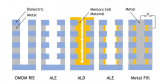

然后,我們必須把圖案轉換成有功能的電路設備,比如控制讀寫數據的晶體管,以及能夠存儲代表“1”和“0”的電荷的又高又瘦的電容器。這一過程意味著要精確控制材料的組成以及這些材料的機械和電學特性,而且每次都要做完全相同的事情。

我們不僅整合了我們自己的創新,而且與供應商合作伙伴緊密合作。我們正在將最新和最先進的技術應用于各個領域:新材料(如更好的導體和更好的絕緣體),以及用于沉積、修改或選擇性去除或蝕刻這些材料的新機械。

我們已經將晶圓廠發展成一個以AI驅動、高度自動化的智能工廠。正如我前面提到的,要在晶圓廠內制造一個現代化的芯片,需要一千多步驟,每一步都必須完美。

半導體制造不像制造汽車。你不能返回并修復流程中早期引入的缺陷。任何缺陷都被埋在后面的層下面。成功的關鍵是數據,以及從數據中獲得的洞察力。來自幾十萬個傳感器的數據涌入我們10千萬億字節的制造執行系統。我們每天通過檢查系統輸入100多萬張圖像,并使用深度學習在問題發生之前發現問題。芯片制造可能是地球上最復雜的工程了。

我們是怎么做到的?

美光的工程團隊是如何能夠在短時間內將1α節點拉下來,并將我們置于行業前沿的。答案就在美光數萬名工程師和科學家身上。

從我們的技術開發、設計、產品和測試工程人員到制造和質量,這是所有相關學科之間協作精神的證明。這也證明了我們的團隊成員的熱情和堅韌,以永久的“全員待命”模式運作,這使美光走在DRAM技術的前沿。

責任編輯人:CC

-

制造工藝

+關注

關注

2文章

196瀏覽量

20242 -

工藝技術

+關注

關注

0文章

19瀏覽量

9617

發布評論請先 登錄

一文詳解快速熱處理技術

BiCMOS工藝技術解析

陶瓷基板五大工藝技術深度剖析:DPC、AMB、DBC、HTCC與LTCC的卓越表現

一文詳解銅大馬士革工藝

ALD和ALE核心工藝技術對比

詳解電容的測試條件

一文詳解1α工藝技術

一文詳解1α工藝技術

評論