作者:吳均 一博科技高速先生團隊隊長;文章來源:高速先生微信公眾號

關于等長與等時

繞線系列的第一篇文章發完之后,就開始準備美國研討會,然后就是長達一個月的出差。終于有時間繼續這個話題了,先來看看之前大家的回復,我隱去了回復者的名字,只保留了答案:

游戲開始,大家直接回復高速先生本微信號,列舉下自己做過的,或者認可的等長設計要求,之前的部分答復如下:

…… ……

之前也提過,現在流行重要的事情說三遍:

1. 等長從來都不是目的,系統要求的是等時……

2. 除了差分對內的等時是為了相位之外,絕大多數的等時都是為了時序!

3. 為了時序而繞線,就一定要搞通時序關系,看懂時序圖

每次看到時序圖的時候,都會眼前一黑有沒有?

時序是大家非常頭痛,也覺得非常復雜的話題,所以高速先生小陳在之前的時序話題中試圖用兩對戀人的戀愛關系來解釋時序問題,繞口令式的比喻不知道有多少人真正看懂了?給我的感覺是80、90后們好像很快領悟了小陳的意思,而70后們普遍表示更暈了有沒有。

想把時序問題簡單講清楚,是一個巨大的挑戰,高速先生的精神就是迎難而上,前仆后繼。我的目標是不給大家看復雜的時序圖,也不引用什么比喻聯想,讓大家簡單理解時序。

借用一張很好的圖,一下子看懂主要的三種時序系統(這里忽略應用較少的內同步時鐘系統)

并行總線包括了早期的共同時鐘和現在流行的源同步時鐘,然后就是串行總線。區分三種系統也很簡單,后續文章分別與大家一一道來。

共同時鐘時序

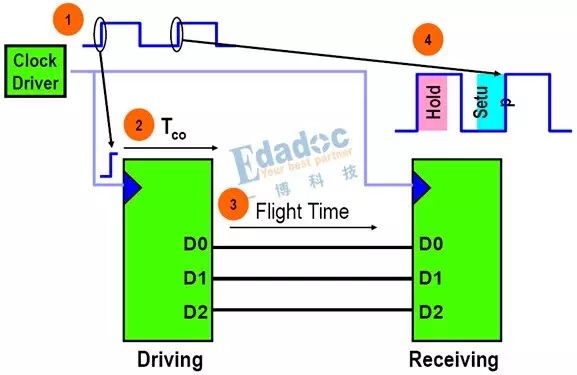

共同時鐘的并行總線,十幾年前的技術,跟不上高速設計的需求,但是現在還有一些應用,比如常見的Local bus基本是共同時鐘總線。還有CPCI總線,PCIX總線,早期的SDRAM等。判斷是否共同時鐘總線的主要特征是:外部時鐘分配器(或者FPGA)分別送出時鐘線到發送與接收芯片。如下圖所示,能找到外部同步時鐘的,一定是共同時鐘總線。

共同時鐘總線的時序特點是,時鐘的上一個邊沿,發送芯片打出數據,然后在下個時鐘邊沿,接收芯片接收數據。為了簡化后面的理解,假定時鐘達到驅動端和接收端的時間一致,也就是時鐘線等長(這也是最常規的設計思路)。

影響時序的因素有Tco,Tskew,Tjitter,Tcrosstalk……,看起來很復雜,簡單來說,只要滿足兩個條件,即可達成時序要求:

一個時鐘周期之內,數據要完成從驅動端發出,到達接收端,并有足夠的建立時間

第二個數據來到之前,前一個數據要有足夠的保持時間

滿足條件1,就要求Tclk能包容數據到達所需的是所有時間,這些時間包括了數據輸出延時(Tco),數據飛行時間(Tflighttime),數據保持時間要求(Tsu),以及所有七七八八影響時序的因素(Tcrosstalk,Tjitter……),并且所有這些因素都要取最惡劣情況。

TPCB skew+Tclock skew +Tjitter +Tco data +Tflt data +Tsetup

滿足條件2,就是下個數據最快會在最小數據輸出延時(Tco min)加上最小數據飛行時間(Tflighttime min)之后達到,數據必須在下個數據達到之前有足夠的保持時間。

Tco data +Tflt data +Tclock skew+Tpcb skew>Thold

真正設計的時候,我們需要從器件手冊查找相應的數據來進行時序計算。從理解角度來說,卻不用那么復雜。

0.3ns

上圖是一個實際案例計算后的結果,我們從中只要看懂兩個事情:

一、共同時鐘總線時序關系隨著TClk的減小,難度急劇加大。33M、66M的共同時鐘總線,適度關注拓撲結構和端接來保證信號質量就夠了,不需要任何繞線。100M以上的共同時鐘總線時序開始變得緊張,133M以上的系統,建議一定要做時序分析,否則風險很大。

二、共同時鐘總線時序是對總長的要求,不是等長,借用Cadence Allegro的規則管理器來解釋,共同時鐘總線最合適的電子規則是Total Etch Length,而不是我們常用的各種Propagation Delay。

注:100M或者133M以上的時候,由于時序非常緊張,有可能通過控制外部時鐘Skew(布線或者調整寄存器)的方式來調節時序,這時對以上不等式兩邊進行調整的過程中會涉及到總長的差異問題。但是也還是用Total Etch Length的規則來約束設計,而不是Propagation Delay

講了這么多,大家繼續暈菜有沒有?想把時序講簡單,是不是Mission Impossible?

還是簡單總結一下:

1. 共同時鐘總線時序關系隨著速率增加,時鐘周期減小,設計難度增加

2. 共同時鐘總線時序是對總長的要求,一般情況下可以理解為盡量走短;沒有等長要求

3. 如果因為時序調整的原因,需要繞線的時候,盡量保證長線不要繞的更長

4. 100M以上的共同時鐘總線,建議進行時序計算,避免風險

審核編輯:何安

-

PCB設計

+關注

關注

396文章

4801瀏覽量

90408

發布評論請先 登錄

高速PCB設計挑戰 Allegro Skill布線功能 自動創建match_group

PCB設計,輕松歸檔,效率倍增!

原理圖和PCB設計中的常見錯誤

必學!PCB設計布線技巧、電機控制、電源管理設計教程等精華資料

SMT貼片前必知!PCB設計審查全攻

電子工程師的PCB設計經驗

PCB設計中常見的DFM問題

PCB設計等長與等時

PCB設計等長與等時

評論