光纖光柵傳感器是利用光纖光柵受外界物理作用時(shí)其反射中心波長(zhǎng)會(huì)發(fā)生偏移的機(jī)理制成的,光纖光柵傳感器具有體積小、重量輕和抗電磁干擾等特點(diǎn),被廣泛應(yīng)用于變壓器、水泵等特殊環(huán)境下的溫度監(jiān)測(cè)。在光纖光柵測(cè)溫系統(tǒng)中,光纖光柵傳感器采集的反射光通過光電檢測(cè)與轉(zhuǎn)換電路把光信號(hào)轉(zhuǎn)換成電信號(hào),經(jīng)高精度的AD轉(zhuǎn)換器得到數(shù)字信號(hào),再經(jīng)過一系列的數(shù)據(jù)處理后得到溫度值。為提高測(cè)量精度和穩(wěn)定性,本文提出了以16位模數(shù)轉(zhuǎn)換器AD7705為核心的光信號(hào)采集系統(tǒng),闡述了FPGA控制模塊的設(shè)計(jì)思路及VHDL實(shí)現(xiàn)方法,并以FPGA作為控制器實(shí)現(xiàn)AD7705邏輯控制,利用QuartuslI對(duì)系統(tǒng)進(jìn)行仿真驗(yàn)證。

1.系統(tǒng)總體結(jié)構(gòu)

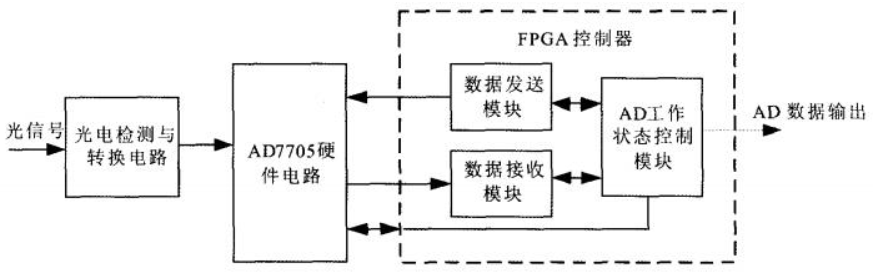

光信號(hào)采集系統(tǒng)總體方框圖如圖1所示,主要由光電檢測(cè)與轉(zhuǎn)換電路、AD7705接口電路、FPGA控制模塊等部分組成,光電檢測(cè)與轉(zhuǎn)換電路把光信號(hào)變成電信號(hào)放大后再送入AD7705電路,AD7705在FPGA的控制下完成AD轉(zhuǎn)換,并把數(shù)據(jù)送入后續(xù)信號(hào)處理模塊處理,計(jì)算出具體的溫度值。

圖1 系統(tǒng)總體結(jié)構(gòu)

2.光電檢測(cè)與轉(zhuǎn)換電路

光纖光柵傳感器反射回來的光信號(hào)功率一般較低,經(jīng)過長(zhǎng)距離傳輸后到達(dá)光電檢測(cè)器的信號(hào)也就非常微弱,而且在放大電路中還存在器件的固有噪聲以及供電電源引起的噪聲,因此,在微弱信號(hào)電路設(shè)計(jì)中必須采取多項(xiàng)措施抑制噪聲,以滿足后續(xù)數(shù)字信號(hào)處理電路的需要。電路采用高精度、低溫漂、低損耗的OP07作為運(yùn)算放大器,該放大器偏置電流非常小,適合用作小信號(hào)放大。光電檢測(cè)與轉(zhuǎn)換電路如圖2所示,光電探測(cè)器采用PIN管,其相當(dāng)于電流源,完成光功率到電流的轉(zhuǎn)化,由于信號(hào)較小,電路采用三級(jí)放大其中一、二級(jí)主要完成光信號(hào)到電流再到電壓的放大與轉(zhuǎn)換,第三級(jí)主要對(duì)電壓進(jìn)行放大,放大后的電壓信號(hào)送入AD7705進(jìn)行AD轉(zhuǎn)換,為減小電源噪聲干擾,每個(gè)電源端需加上耦電容。

圖2 光電檢測(cè)與轉(zhuǎn)換電路

3.AD7705硬件電路

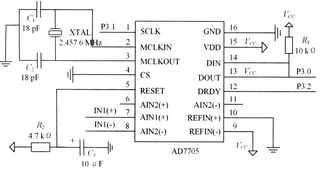

AD7705是AD公司生產(chǎn)的適合測(cè)量低頻信號(hào)的16位AD轉(zhuǎn)換器,片內(nèi)帶有數(shù)字濾波和增益可編程的∑-?轉(zhuǎn)換技術(shù),能夠直接將傳感器測(cè)量到的微小信號(hào)進(jìn)行AD轉(zhuǎn)換,具有寬動(dòng)態(tài)范圍、高分辯率等特點(diǎn),在儀器儀表測(cè)量、工業(yè)控制等領(lǐng)域有廣泛的應(yīng)用。AD7705配有串行通信接口,可配置成三線或四線接口模式(CS、SCLK、MOSI、MISO),其增益值、信號(hào)的極性以及更新速率可由軟件靈活配置。AD7705外圍接口電路如圖3所示。

圖3 AD7705硬件接口電路

AD7705主要引腳及功能:兩組模擬信號(hào)輸入端AIN1(+)、AIN1(-)和AIN2(+)、AIN2(-),分別可配置成單極性輸入和差分輸入,通信接口為片選端,低電平有效,DIN為串行數(shù)據(jù)輸入端,DOUT為轉(zhuǎn)換結(jié)果的串行數(shù)據(jù)輸出端,SCLK為串行移位脈沖,一般由控制芯片提供,DRDY為邏輯輸出,高電平表示數(shù)據(jù)正在更新中,低電平表示AD轉(zhuǎn)換結(jié)束可以讀取數(shù)據(jù),REF(+)、REF(-)為基準(zhǔn)輸入端,由于基準(zhǔn)電壓對(duì)轉(zhuǎn)換結(jié)果影響較大,本設(shè)計(jì)采用低動(dòng)態(tài)阻抗、低噪音的LM285D作為基準(zhǔn)電源,為AD提供2.5V基準(zhǔn)電壓。

4.FPGA控制器設(shè)計(jì)

用戶對(duì)AD7705的功能設(shè)置以及AD轉(zhuǎn)換結(jié)果輸出都是采用串行接口方式訪問片內(nèi)寄存器,本設(shè)計(jì)采用VHDL語言把通信接口配置成四線工作方式,即與AD7705的CS、SCLK、DIN、DOUT端口進(jìn)行通信,完成串行數(shù)據(jù)的發(fā)送和接收。

4.1數(shù)據(jù)發(fā)送模塊

數(shù)據(jù)發(fā)送模塊SPI_WRITE就是把各種控制字以串行方式寫入AD7705內(nèi)部相應(yīng)的寄存器,實(shí)現(xiàn)各種功能。在寫入過程中必須按AD7705的工作時(shí)序要求傳送數(shù)據(jù),才能保證數(shù)據(jù)準(zhǔn)確性和有效性,該模塊采用VHDL進(jìn)行設(shè)計(jì),其端口設(shè)置如下:

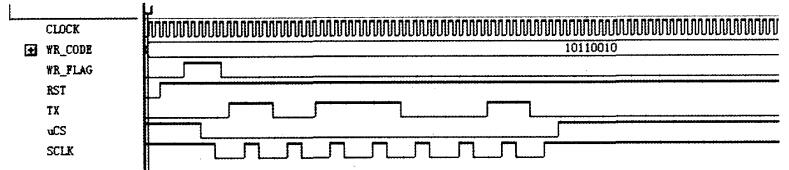

由于與寫入有關(guān)的寄存器均為8位寄存器,因此,把SPI_WRITE模塊設(shè)計(jì)成一個(gè)8位并入串出移位寄存器,當(dāng)WR_FLAG控制信號(hào)為高電平時(shí),讀入WR_CODE[7.。.0]中控制字的值,同時(shí)在SCLK上產(chǎn)生8個(gè)移位脈沖,并在移位脈沖的作用下把8位輸人數(shù)據(jù)轉(zhuǎn)換為串行數(shù)據(jù)從TX端輸出,在這移位期間uCS輸出保持低電平,數(shù)據(jù)移位完后重新回到高電平,并等待下一個(gè)寫入控制脈沖,其仿真結(jié)果如圖4所示。

圖4 數(shù)據(jù)發(fā)送模塊仿真

4.2數(shù)據(jù)接收模塊

數(shù)據(jù)接收模塊SPI_READ主要是讀取AD7705內(nèi)部數(shù)據(jù)寄存器中已轉(zhuǎn)換好的AD值,其設(shè)計(jì)原理與數(shù)據(jù)發(fā)送模塊類似,該模塊端口設(shè)置如下:

由于AD7705內(nèi)部數(shù)據(jù)寄存器是一個(gè)16位寄存器,因此,SPI_READ模塊是一個(gè)串入并出的16位移位寄存器,當(dāng)DRDY為低電平,且RD_FLAG為高電平時(shí),系統(tǒng)開始讀取AD7705的16位串行數(shù)據(jù),經(jīng)過16個(gè)脈沖后,完成串并轉(zhuǎn)換,RECE_OK結(jié)束標(biāo)志位置高電平,同時(shí)輸出并行數(shù)據(jù)RECE_DATA[15.。.0],仿真結(jié)果如圖5所示。

圖5 數(shù)據(jù)接收模塊仿真

4.3AD7705工作狀態(tài)控制模塊

AD7705工作狀態(tài)控制模塊STATE_CTR是根據(jù)AD7705工作流程,完成各種設(shè)置并讀取AD轉(zhuǎn)換值,AD7705內(nèi)部主要有通信寄存器、設(shè)置寄存器、時(shí)鐘寄存器、數(shù)據(jù)寄存器等,其中通信寄存器主要管理通道選擇,并決定下一個(gè)操作是讀操作還是寫操作,以及下一次讀或?qū)懩囊粋€(gè)寄存器,所有與器件的通信必須從寫入通信寄存器開始。該模塊采用VHDL有限狀態(tài)機(jī)實(shí)現(xiàn),該控制器由7個(gè)工作狀態(tài)組成,其狀態(tài)轉(zhuǎn)換圖如圖6所示。

圖6 AD7705工作狀態(tài)轉(zhuǎn)換

S0狀態(tài):初始化,寫通信寄存器20H,將下一個(gè)操作設(shè)為對(duì)時(shí)鐘寄存器進(jìn)行寫操作;

S1狀態(tài):寫時(shí)鐘寄存器04H,外部時(shí)鐘頻率設(shè)為4.9152MHz,更新頻率為50Hz;

S2狀態(tài):寫通信寄存器10H,選擇通道1為輸入端口,將下一個(gè)操作設(shè)為設(shè)置寄存器寫操作;

S3狀態(tài):寫設(shè)置寄存器40H,增益設(shè)為1,差分輸入,自校準(zhǔn)模式;

S4狀態(tài):查詢DRDY端口值,如果為低電平表示AD轉(zhuǎn)換結(jié)束,可以讀出轉(zhuǎn)換結(jié)果;否則數(shù)據(jù)尚在更新中,繼續(xù)待待;

S5狀態(tài):寫通信寄存器38H,將下一個(gè)操作設(shè)為對(duì)數(shù)據(jù)寄存器進(jìn)行讀操作;

S6狀態(tài):從數(shù)據(jù)寄存器中讀取AD值,重新返回S4狀態(tài),重復(fù)上面的步驟,并可連續(xù)讀出AD的值。

4.4FPGA控制器結(jié)構(gòu)

FPGA控制器結(jié)構(gòu)圖如圖7所示,由FENPING分頻模塊、SPI_WRITE數(shù)據(jù)發(fā)送模塊、SPI_READ數(shù)據(jù)接收模塊及STATE_CTR工作狀態(tài)控制模塊組成。AD7705外接時(shí)鐘為4.9152MHz,設(shè)計(jì)選用更新速率為50Hz,同時(shí)從AD手冊(cè)可知串行時(shí)鐘脈沖寬度不得小于100ns,即時(shí)鐘不得大于5MHz,F(xiàn)PGA開發(fā)板上配有50MHz時(shí)鐘源,通過分頻模塊FENPING得到3MHz輸出頻率,再經(jīng)過SPI_READ和SPI_WRITE模塊后產(chǎn)生500kHz的移位脈沖頻率,即每寫入一個(gè)字節(jié)需要16ms,因此,在STATE_CTR模塊中,每寫入一個(gè)控制字需要等待16ms以上才能進(jìn)入下一個(gè)狀態(tài),而數(shù)據(jù)寄存器是16位的,因此,在讀出AD轉(zhuǎn)換數(shù)據(jù)時(shí)需要等待32ms以上,才能進(jìn)入下一個(gè)狀態(tài),讀取下一個(gè)數(shù)據(jù)。

圖7 FPGA控制器結(jié)構(gòu)

5.系統(tǒng)測(cè)試與仿真

在QuartuslI平臺(tái)上對(duì)FPGA控制模塊進(jìn)行了仿真測(cè)試,其仿真結(jié)果如圖8所示。

圖8 FPGA控制器仿真波形

從圖8中可以看出,前面4組寫入脈沖分別寫入20H、04H、10H、40H,當(dāng)DRDY端信號(hào)為低電平時(shí)表示AD數(shù)據(jù)已轉(zhuǎn)換結(jié)束,再寫入38H,再經(jīng)過16個(gè)脈沖讀出轉(zhuǎn)換數(shù)據(jù),然后又繼續(xù)等待DRDY變?yōu)榈碗娖剑芏鴱?fù)始,并可連續(xù)讀取AD轉(zhuǎn)換值。根據(jù)測(cè)試數(shù)據(jù)進(jìn)行分析,符合AD7705工作時(shí)序要求,最后把設(shè)計(jì)文件下載至CycloneII的EP2C8Q208C7芯片進(jìn)行驗(yàn)證測(cè)試,實(shí)現(xiàn)相關(guān)功能。

結(jié)束語

本文總結(jié)了基于AD7705與FPGA的光信號(hào)采集系統(tǒng)設(shè)計(jì)。該系統(tǒng)采用高精度的AD轉(zhuǎn)換器,利用FPGA及VHDL有限狀態(tài)機(jī)完成對(duì)AD7705的時(shí)序邏輯控制,完成光信號(hào)的檢測(cè)與放大及數(shù)據(jù)轉(zhuǎn)換,以軟件方式實(shí)現(xiàn)硬件電路,控制靈活、轉(zhuǎn)換精度高、穩(wěn)定性好,在水泵的溫度檢測(cè)應(yīng)用系統(tǒng)中有良好應(yīng)用,同時(shí)對(duì)于一些精度要求高,而輸入信號(hào)較小的其他模擬量檢測(cè)也有較好的應(yīng)用參考價(jià)值。

責(zé)任編輯人:CC

-

FPGA

+關(guān)注

關(guān)注

1643文章

21957瀏覽量

614026 -

光信號(hào)

+關(guān)注

關(guān)注

0文章

455瀏覽量

28061 -

AD7705

+關(guān)注

關(guān)注

2文章

39瀏覽量

20814

發(fā)布評(píng)論請(qǐng)先 登錄

AD7705采樣通道2沒有數(shù)據(jù)輸出

AD7705應(yīng)用經(jīng)驗(yàn)總結(jié)

AD7705的基本特性是什么?怎樣對(duì)AD7705進(jìn)行校準(zhǔn)?

AD7705的應(yīng)用經(jīng)驗(yàn)以及注意要點(diǎn)

求助,關(guān)于AD7705采樣的幾個(gè)問題

AD7705/AD7706的原理與應(yīng)用

基于AD7705的安全帽質(zhì)量檢測(cè)

基于AD7705的在線激光功率檢測(cè)系統(tǒng)設(shè)計(jì)

基于AD7705的雙路信號(hào)采集板已批量生產(chǎn)

基于AD7705與FPGA的光信號(hào)采集系統(tǒng)設(shè)計(jì)資料下載

基于AD7705與FPGA的光信號(hào)采集系統(tǒng)設(shè)計(jì)

基于AD7705與FPGA的光信號(hào)采集系統(tǒng)設(shè)計(jì)

評(píng)論