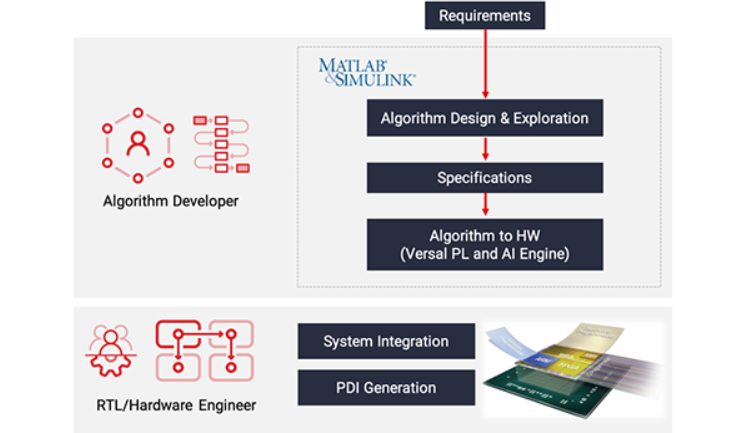

賽靈思MATLAB & Simulink Add-on插件是將ModelComposer和System Generator forDSP完美結合的統一工具。它是一種基于模型的設計工具,幫助算法和 RTL /硬件開發者在MathWorks Simulink環境中以賽靈思器件為目標,快速開展設計與探索。

該工具提供高級性能優化模塊,并可通過系統級仿真驗證功能正確性。此外,它還能將算法規范轉換為有可產品化的質量保證的實現方案,并通過自動代碼生成加快設計產品化速度。

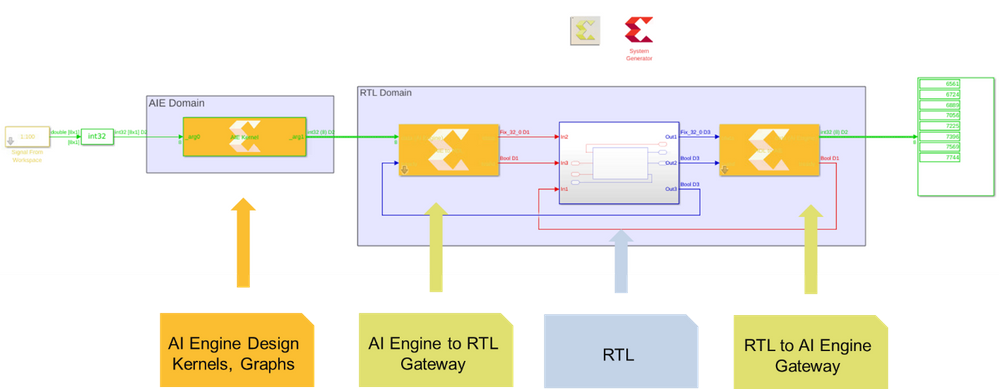

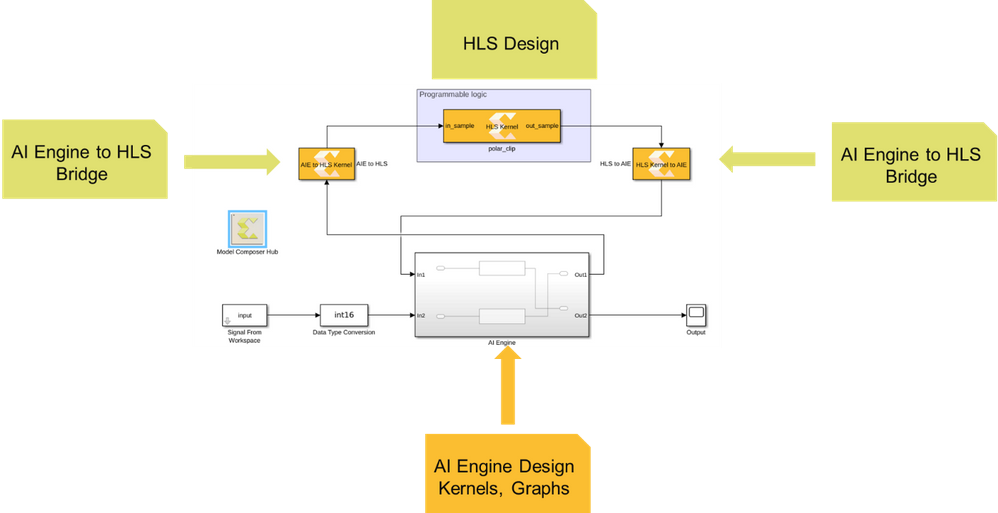

MATLAB & Simulink Add-on 插件涵蓋了可編程邏輯 (PL) 域和 AI 引擎域。對于 PL 域,您可以使用基于 RTL 的模塊(周期精度)或基于高層次綜合 (HLS) 的模塊。

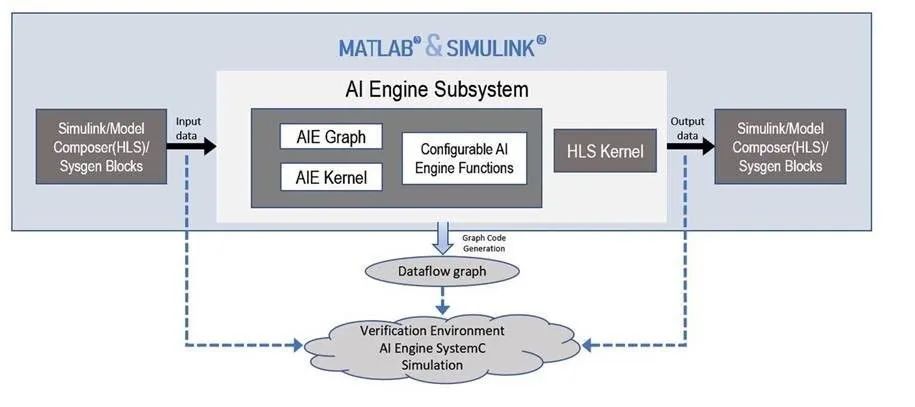

在2020.2 版中,MATLAB & Simulink Add-on插件可支持賽靈思 Versal 平臺。它能夠在 Simulink 環境中完成算法 (面向 AI 引擎) 的快速仿真、探索和代碼生成。用戶能夠通過下列方式來實現這個:

以模塊的方式導入 AI 引擎內核和數據流圖 (多核設計) 。

通過可參數化的模塊,可以控制AI 引擎內核和和數據流圖 (多核設計) 的配置。

從現有的 AI 引擎 DSP 庫模塊添加可配置的 AI 引擎函數。

通過將示波器、顯示器和頻譜分析器等 Simulink 模塊與設計內的任何信號進行無縫連接,可實現仿真結果的可視化。這將顯著簡化模型的分析與調試工作。此外,還可以將仿真結果發送到 MATLAB 工作空間進行深入分析。

MATLAB 與Simulink 插件提供了一組 AI 引擎庫模塊,以便在 Simulink 環境中使用,包括:

導入面向 Versal 器件的 AI 引擎的內核和流圖 (多核設計) 模塊。

導入面向 Versal 器件的 PL 部分的 HLS 內核的模塊。

支持 AI 引擎與賽靈思 HDL 模塊集相連的模塊。

可配置的 AI 引擎函數。

連接HLS 內核塊、HDL 庫塊和 AI 引擎塊就能為異構平臺建模仿真,并且允許異構平臺同時指向 Versal 平臺上的可編程邏輯和 AI 引擎。這種功能仿真的運行速度顯著高于周期精度仿真,同時支持設計的快速迭代。

在功能仿真之外,用戶也可以使用 MATLAB 與 Simulink Hub 插件生成數據流圖和測試文件。此外,該工具能夠以最優方式運行測試文件,確保所生成的graph code的周期精度 System C 仿真器的輸出與 Simulink 環境下基準設計的結果吻合,為最終用戶節省大量時間。

典型的 AI 引擎設計流程如下圖所示:

MATLAB & SimulinkAdd-on插件可以為Versal各平臺實現混合域設計:

AI 引擎+HDL (SystemGenerator)

AI 引擎 + HLS (高層次綜合)

責任編輯:lq

-

matlab

+關注

關注

188文章

2998瀏覽量

233281 -

賽靈思

+關注

關注

33文章

1795瀏覽量

132132 -

算法

+關注

關注

23文章

4700瀏覽量

94790

原文標題:使用賽靈思MATLAB & Simulink Add-on插件面向 Versal AI 引擎設計

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

智多晶FIFO_Generator IP介紹

**【技術干貨】Nordic nRF54系列芯片:傳感器數據采集與AI機器學習的完美結合**

Flexusx 實例與 Harbor 私有鏡像倉庫的完美結合

望獲實時Linux系統與Betaflight的結合:計算與飛控的完美協作

構建高效搜索解決方案,Elasticsearch & Kibana 的完美結合

MCX接頭技術全解析:高頻傳輸與快速插拔的完美結合

如何將MSP430FR6047 Clock System域與USS振蕩器同步

統一多云管理平臺怎么用?

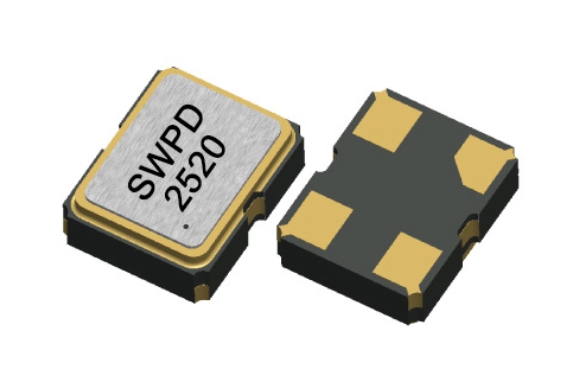

石英 CMOS 振蕩器 PD2520 系列 1 to 200 MHz :卓越性能與廣泛應用的完美結合

將ModelComposer和System Generator forDSP完美結合的統一工具

將ModelComposer和System Generator forDSP完美結合的統一工具

評論