本月初,由七名Arm Research工程師組成的小組成立了一家名為Cerfe Labs的初創公司,以將過去五年來與位于科羅拉多州的Symetrix共同致力于的實驗存儲技術商業化。而這項稱技術就叫做CeRAM(correlated electron)。按照他們的說法,這種技術可能會成為當今處理器高級高速緩存中使用的快速訪問嵌入式SRAM的非易失性替代產品。除了能夠在沒有沒有電源的情況下保存數據之外(SRAM做不到),CeRAM的尺寸可能比SRAM還要小得多,這可能會緩解IC領域的問題,因為業界保持縮小晶體管的能力已到盡頭。

大多數半導體物理學都依賴于可以單獨處理電子的假設。但是半個多世紀以前, Neville Francis Mott指出,在某些材料中,當電子被迫聚在一起時,“ [這些材料]會產生奇怪的事情,”前Arm研究部研究員,現為Cerfe Labs首席技術官的Greg Yeric說,其中之一是金屬狀態和絕緣狀態之間的可逆轉換,稱為莫特轉換(Mott transition)。世界各地的實驗室一直在研究氧化釩和其他材料中的這種現象,而HP Labs最近則描述了一種依賴該原理的類似神經元的設備。

Yeric說:“通過與Symetrix的合作,我們認為我們擁有的是電控相關電子(correlated-electron)開關,這種材料可以切換電阻狀態。”

這些公司正在探索多種材料,但是到目前為止,他們投入最多的材料是碳摻雜的氧化鎳(carbon-doped nickel oxide)。氧化物的自然狀態是不導電的。也就是說,與原子結合的電子的允許能態與自由移動的能態之間存在間隙。但是隨著碳的摻雜,材料成為導體。碳改變了能帶結構以減小間隙。Yeric解釋說,這種從應有的氧化物到金屬的變化是由于“相關”的電子-電子相互作用。如果從材料中提取出足夠多的電子,則效應會降低到臨界點,并且能帶會分開,從而使材料再次成為絕緣體。

Yeric說:“我們有一組材料表現出這種轉變,并且重要的是,在每一側都具有非易失性狀態”。

設備本身只是夾在兩個電極之間的相關電子材料,其結構類似于電阻式RAM,相變RAM和磁性RAM,但復雜性不如后者。就像這三個一樣,它是在硅上方的金屬互連層中構造的,與SRAM的六個晶體管相反,它僅需要硅層中的一個晶體管即可訪問它。Yeric說,該公司已經制造出了適合7納米CMOS工藝的設備,并且它們的尺寸和電壓都應可擴展,以適應未來的尖端半導體工藝節點。

但是CeRAM的速度可以使其很好地替代SRAM。迄今為止,他們已經使CeRAM具有2納秒的脈沖寬度來寫入數據,這與處理器的L3高速緩存所需的速度相當;Yeric說他們希望隨著開發速度的提高。

碳摻雜的氧化鎳材料還具有遠遠超過當今的非易失性存儲器所能實現的性能,但尚未得到充分證明。例如,Cerfe Labs已證明該設備可在低至1.5開爾文的溫度下工作,這遠遠超出任何非易失性存儲器的工作溫度范圍,并且在量子計算控制電路中的作用范圍內。在另一個方向,他們展示了器件在最高150°C的溫度下工作,并表明其在最高400°C的溫度下仍能保持其工作狀態。但是這些數字受到該公司可用設備的限制。此外,該器件的工作原理表明,CeRAM應該自然抗電離輻射和磁場干擾。

Symetrix公司還開發了鐵電RAM,在一項名為FRANC的美國國防高級研究計劃局(DARPA)計劃的理論研究中,探索了相關的電子材料,從而為新型計算奠定了基礎。Symetrix“將模型放在一起,并能夠預測材料”,另一位Arm老將CEO Eric Hennenhoefer說。

Yeric說:“系統設計人員一直在尋求改進的內存,因為幾乎每個系統都在某種程度上受到它可以訪問的內存的限制。” “在[Arm]討論可能的未來技術時,我們遇到了Symetrix技術。我們最終基于該技術的許可(非常早且具有推測性),在不折衷的前提下提高了嵌入式內存的速度,密度,成本和功耗。

他說,CerfeLab的目標不是制造CeRAM,而是將技術開發到大型制造商將要接管開發的地步。新的內存技術從發現到商業化的過程通常至少需要八到九年的時間。他估計,CeRAM大約只需一半的時間。

在尚待解決的問題中,涉及存儲器的耐用性-在存儲器開始出現故障之前可以切換多少次。從理論上講,CeRAM 設備中沒有任何元件會磨損。但是認為現實世界中不會有問題是天真的。Yeric說:“總是有外在的東西限制耐力。”

責任編輯:lq

-

處理器

+關注

關注

68文章

19811瀏覽量

233600 -

sram

+關注

關注

6文章

782瀏覽量

115680 -

存儲技術

+關注

關注

6文章

754瀏覽量

46233

原文標題:?【行業資訊】這種存儲旨在替代SRAM

文章出處:【微信號:gh_c8682fd6f974,微信公眾號:半導體促進會】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

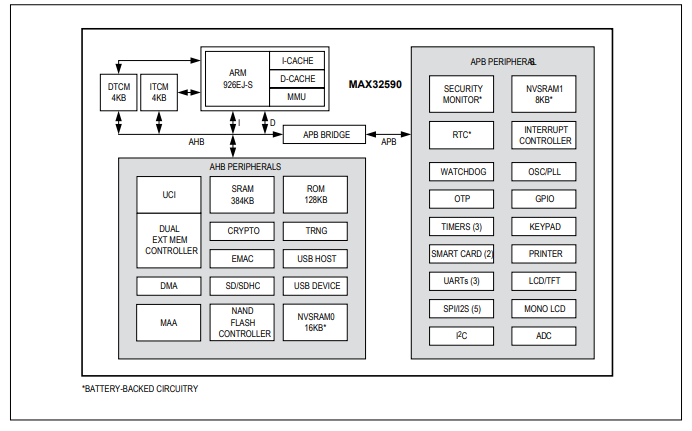

MAX32590 DeepCover安全微處理器,集成ARM926EJ-S處理器核技術手冊

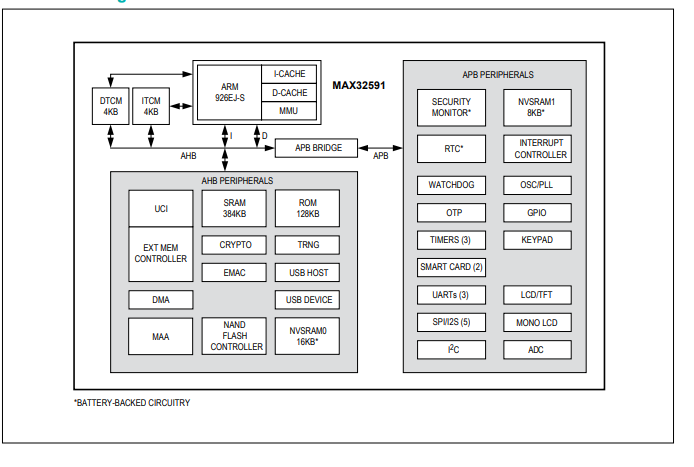

MAX32591 DeepCover安全微控制器,集成ARM926EJ-S處理器核技術手冊

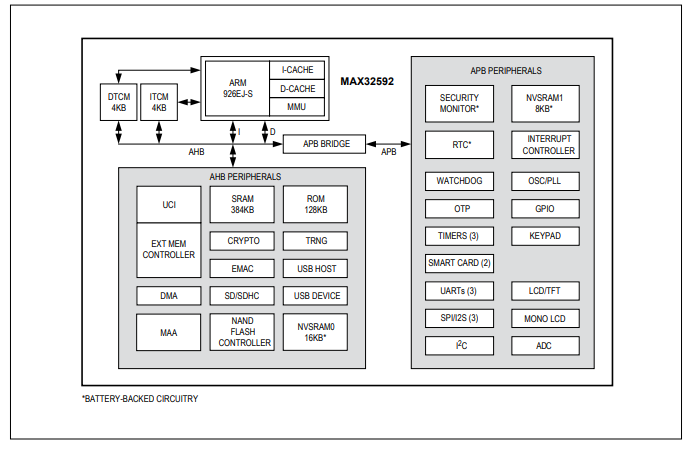

MAX32592內置ARM926EJ-S處理器核的DeepCover安全微控制器技術手冊

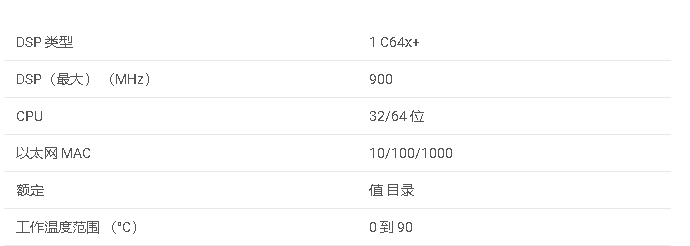

TMS320C6452 C64x+ 定點 DSP - 高達 900MHz,1Gbps 以太網數據手冊

高速ADC、DAC與處理器之間是怎么通信的呢?

緩存對大數據處理的影響分析

什么是緩存(Cache)及其作用

TMS320C64x在高性能DSP應用中的高速緩存使用情況

寄存器和高速緩存有什么區別

CP3SP33帶高速緩存、DSP、藍牙、USB和雙CAN接口的連接處理器數據表

什么是ARM處理器?與x86的比較及其優缺點

這種技術可能會成為處理器高級高速緩存中使用的SRAM的替代產品

這種技術可能會成為處理器高級高速緩存中使用的SRAM的替代產品

評論