搞SI和RF的都知道“阻抗”這個詞,其在電路設計中的重要性,尤其高速高頻,PCB工程師常用PolarSi9000計算阻抗,很方便。IC封裝設計同行的也用其來計算封裝基板的走線阻抗。封裝基板也是PCB,這樣做肯定也行,但個別地方需要注意。

1.Stripline的阻抗計算,用PolarSi9000完全沒有問題,因為信號走線完全埋在Substrate里,結構跟PCB相同;

2.Micronstripline的阻抗計算則務必留意,塑封封裝后基板的上表面會覆蓋塑封料(見下圖),計算時必須考慮到。

塑封料是一種混合物,一般由樹脂(環氧、酚醛)、填充劑(二氧化硅粉)、硬化劑、脫模劑等混合而成。作為絕緣介質,會對阻抗產生影響。

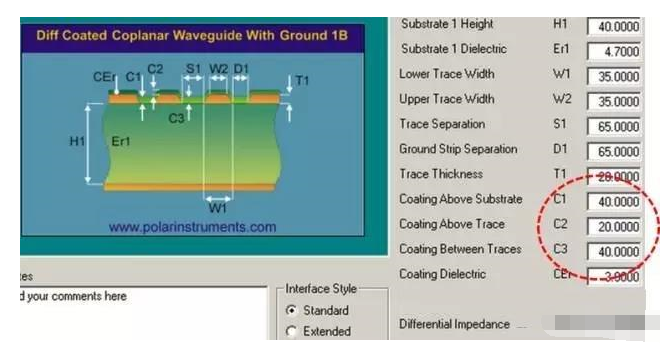

下面我們看封裝基板上90Ohm的差分微帶,不考慮塑封料的影響,按一般的結構PolarSi9000計算結果如下,差分阻抗90.75Ohm:

由于封裝基板表面會有阻焊覆蓋,實際的截面如下,一般阻焊是平整的,而不是上圖想當然的階梯形。我們按實際結構計算,差分阻抗87.49Ohm,相比90.75Ohm,差了3.6%,還好。

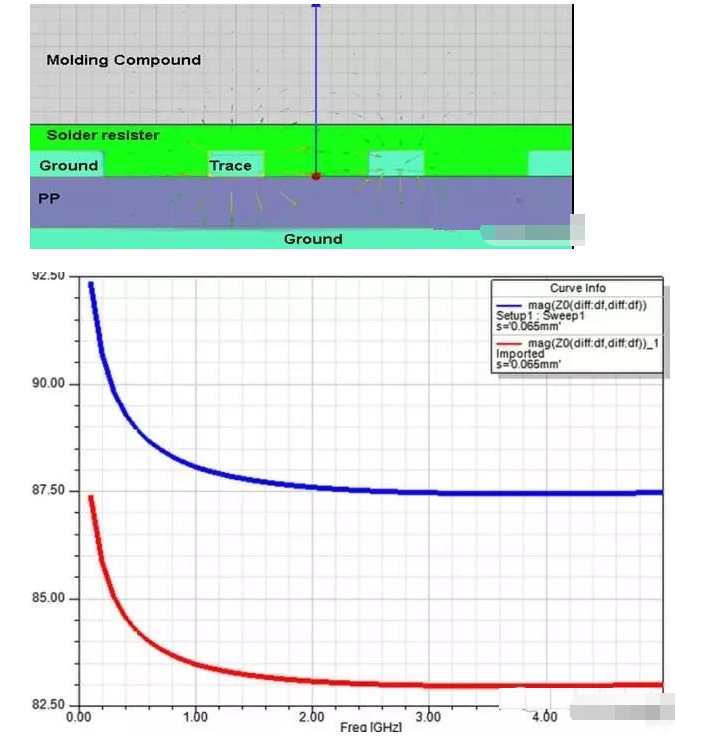

下面我們考慮塑封料(厚度700um,Dk/Df=4/0.01),為了直觀的看出塑封的影響,我們在Q2D中建模如下圖。

按上面PolarSi9000中的結構建模、仿真、后處理。我們從電場分布中,可以直觀的看到部分電場已超出綠油的范圍,滲透到塑封料內部。如果計算不考慮塑封,而默認為自由空間的話,最終封裝后實際的阻抗會偏離預定目標。

下圖紅色曲線是實際的阻抗曲線,2Ghz處約為83Ohm,與上面不考慮塑封料的87.49Ohm比較,相差了5%。(藍色曲線是作為驗證對比,按照PolarSi9000中的模型不考慮塑封料計算,得出2Ghz處差分阻抗87.5Ohm,與PolarSi9000中的計算結果87.49Ohm基本相同,說明兩種軟件計算結果相同。)

若不考慮阻焊和塑封料的實際結構,我們實際得到的阻抗是83Ohm,與90.75Ohm相比差了8.5%,跟加工誤差一個級別了,這會對高頻高速信號產生嚴重影響。

由于PolarSi9000中還沒有上面對應的結構,所以各位需要計算類似結構的,就采用其他工具吧,推薦Q2D。

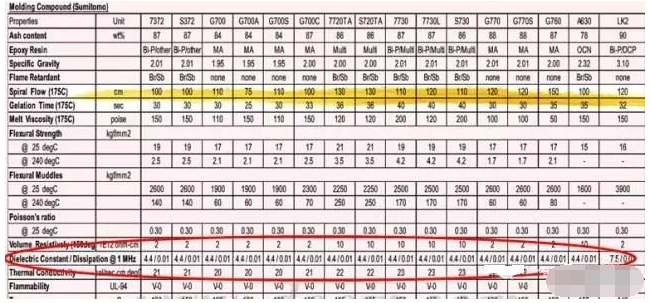

另外,下面附上部分塑封料的材料參數,僅供參考。

責任編輯人:CC

-

封裝

+關注

關注

128文章

8484瀏覽量

144776 -

基板

+關注

關注

2文章

298瀏覽量

23424

發布評論請先 登錄

玻璃基板時代,TGV技術引領基板封裝

求微帶線的阻抗公式的教科書

如何進行ML605疊加阻抗計算?

芯片那么小,封裝基板走線損耗能大到哪去?

特性阻抗公式 (含微帶線,帶狀線的計算公式)

如何用HFSS-API來設計指數漸變傳輸線?

一文知道封裝基板微帶阻抗計算

一文知道封裝基板微帶阻抗計算

評論