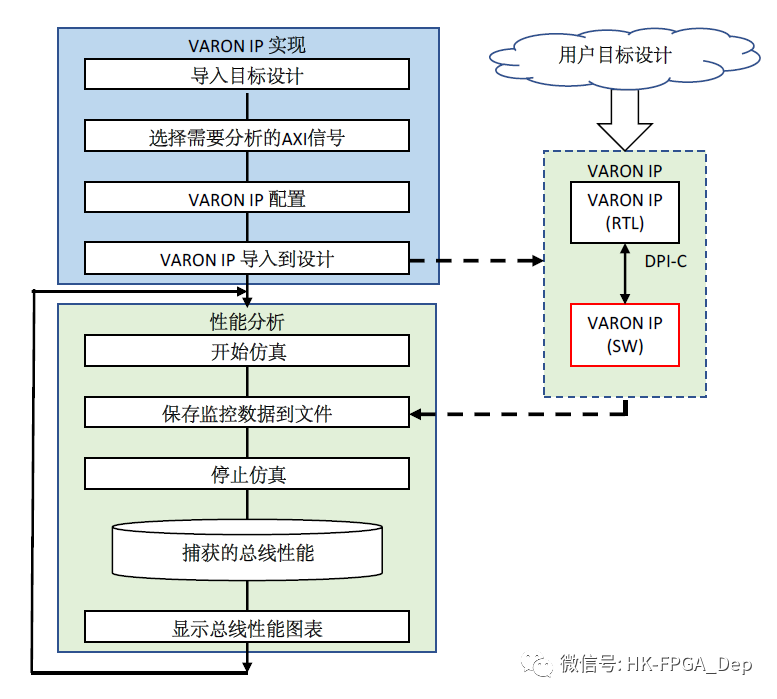

下圖顯示了VARON的設計流程。

第一步,將VARON IP導入用戶的目標設計。VARON IP用RTL(Verilog HDL)編寫。這允許用戶將VARON IP導入到Verilog HDL或VHDL編寫的用戶設計和環境中。

第二步是選擇要觀察的AXI信號,然后完成VARON IP配置并注入用戶設計。VARON IP實施完成后,運行仿真,將選擇的信號數據提取到文件中并進行仿真。

最后,啟動VARON監控器并加載總線性能數據,然后使用各種性能分析工具開始性能分析。

01

VARON IP配置

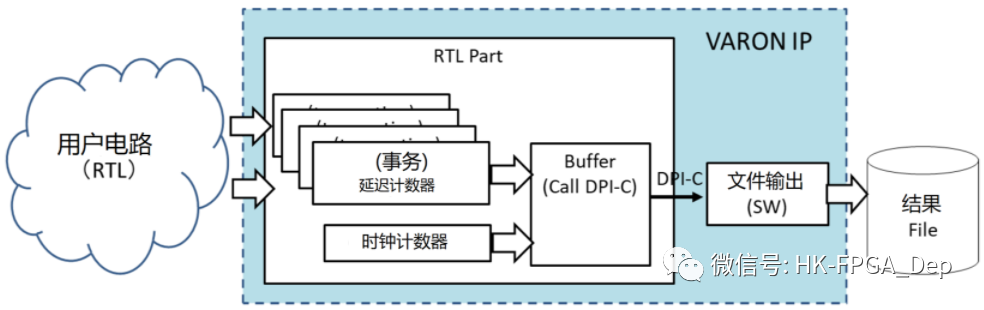

下圖顯示了VARON IP。

VARON IP由時鐘計數器,讀取側/寫入側的延遲計數器和RTL編寫的緩沖區組成,以及由C語言編寫的文件輸出軟件組成。

1. 時鐘計數器

ACLK的計數(由ARESETn初始化)

單位時間的測量:

周期間隔(單位時間)可以從仿真參數中設置。

2. 延遲計數器(事務)

一個延遲計數器可以捕獲1個AXI總線端口。

捕獲交易時間和突發長度。

3. 緩沖區(DPI-C)

收集時鐘計數器和每個端口的事務處理信息,并通過DPI-C將其傳遞到文件輸出軟件以輸出文件。

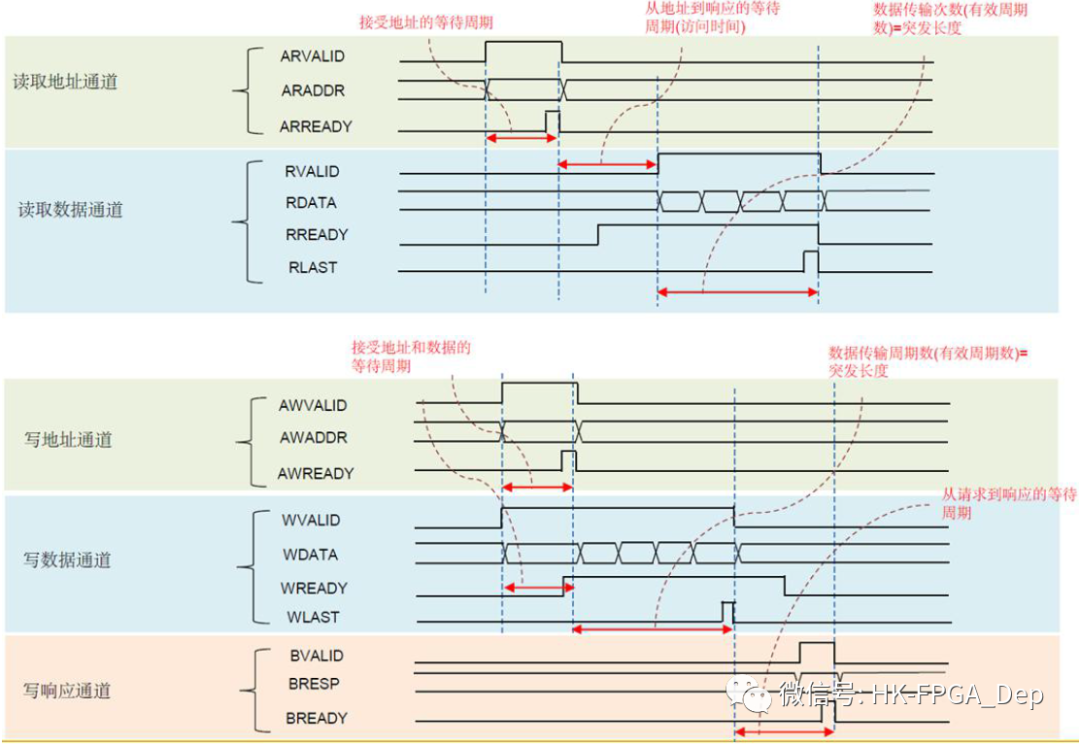

該圖顯示了在AXI總線標準上讀取/寫入事務的捕獲時序。

例如,VARON測出讀取事務需要3個等待周期。

地址等待周期是從ARVALID聲明到ARREADY聲明,它表示從主機到主機發送地址到從機的延遲。

訪問時間是指從接受地址到開始數據傳輸的時間。

數據周期是從接收到的第一個突發數據到最后一個接收的突發數據的周期,取決于RVALID和RREADY握手,它可能與真實的傳輸突發長度不同。

02

示例設計

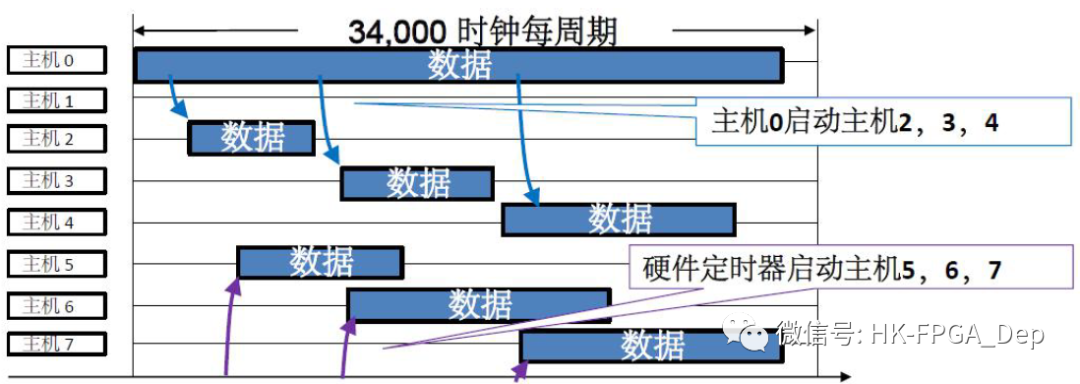

下圖顯示了一個簡單的示例設計。該示例設計包含8個讀/寫主通道,這些通道由主控器和2個從屬端口連接到MEMC AXI總線互連,通過主控器的AXI ID和接收到的端口號產生從屬(連接到MEMC)端口AXI ID。

在典型的性能分析中,用戶希望捕獲來自MEMC端口的數據傳輸量和突發長度,以及來自主端口的等待周期,等待時間周期和數據傳輸量。此示例將連接主機和互連的AXI總線記錄為“主側”,將連接互連和MEMC的AXI總線記錄為“從側”。

該圖是運行此示例設計的34,000個周期時仿真結果的主機訪問圖像視圖。對于兩個MEMC端口,VARON每200個時鐘周期(單位時間)捕獲一次數據傳輸量。

03

結果分析

示例設計中的VARON監控器分析圖示例如下圖所示。VARON 仿真版本,允許用戶通過一次仿真獲得所有分析圖。該仿真運行80,000個時鐘周期,單位時間(用于測量數據量的間隔時間)為200個時鐘周期。

以下是圖中分析結果圖表的列表。

每個AXI ID和單位時間的從站側讀取數據傳輸量

每個AXI ID和單位時間的從站側讀取數據傳輸量分布

每個端口/ ID的主站側讀取事務時序圖

每個端口的主端讀取延遲分布

VARON監視器允許用戶對分析圖進行以下操作。

垂直度/水平滾動(通過滾動條和光標鍵。

)

放大,縮小和縮放適合(通過按鈕和按鍵+,-,f。

)

工具提示:

將鼠標移至捕獲并顯示值。

指定顯示的時鐘周期數(時間序列圖)

搜索意外值(按鈕和按鍵:

Ctrl-F)

打開對話框->設定范圍(最小和最大值)->以紅色突出顯示超出范圍的捕獲

以下是查找具有較大延遲值的事務的示例。

1. VARON通過“按端口讀取延遲數字直方圖”圖表幫助用戶查找延遲值超出目標范圍的事務。

①單擊“按端口讀取延遲號直方圖”圖。

②單擊“查找超出范圍的值”按鈕。

③為Port0設置等待時間0的最小值和等待時間100的最大值,然后單擊確定。

④超出范圍的事務將突出顯示為紅色。

2.此示例通過“按端口/ ID讀取事務時序圖”圖表查找延遲值超出目標范圍的事務。

①點擊“按端口/ ID讀取交易時序圖”圖。

②單擊“查找超出范圍的值”按鈕。

③為Port0設置等待時間0的最小值和等待時間100的最大值,然后單擊“確定”。

④超出范圍的事務將突出顯示為紅色。

⑤單擊工具欄的向右箭頭按鈕,然后搜索下一個錯誤。

VARON

VARON是一款針對Soc開發的硬件仿真進行優化的軟件,運行于Cent OS Linux系統,適用于集成度偏高的Soc開發。VARON能夠監測AXI總線上的多種屬性和性能,從而使開發者能夠更直觀的觀測系統的運行情況,從而有針對性的進行優化調整。

原文標題:VARON設計流程及示例

文章出處:【微信公眾號:FPGA技術支持】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

數據

+關注

關注

8文章

7255瀏覽量

91812 -

信號

+關注

關注

11文章

2851瀏覽量

78253

原文標題:VARON設計流程及示例

文章出處:【微信號:HK-FPGA_Dep,微信公眾號:FPGA技術支持】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

一文看懂芯片的設計流程

芯片失效分析的方法和流程

NX CAD軟件:數字化工作流程解決方案(CAD工作流程)

Vivado之實現布局布線流程介紹

MOSFET晶體管的工藝制造流程

數字設計ic芯片流程

接單流程設計探索

VARON的設計流程

VARON的設計流程

評論