本文用的芯片型號為xcku115-flvd1924-1L-i,時(shí)鐘頻率為400MHz。

兩個(gè)有符號數(shù)相加

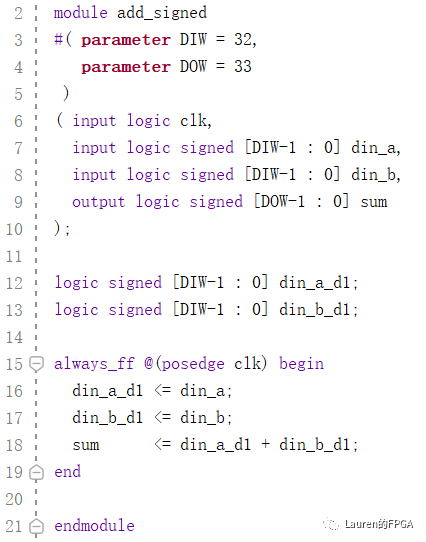

采用RTL代碼描述位寬相同的兩個(gè)數(shù)相加或相減,無論是有符號數(shù)還是無符號數(shù),Vivado綜合后的結(jié)果是一致的。以32bit數(shù)據(jù)為例,相應(yīng)的代碼如下圖所示。這里考慮到兩個(gè)32bit數(shù)據(jù)相加其結(jié)果可能為33bit,同時(shí)對于高速設(shè)計(jì)(時(shí)鐘頻率至少400MHz)為了滿足性能,對輸入和輸出分別添加了流水寄存器。

最終的資源利用率如下圖所示。

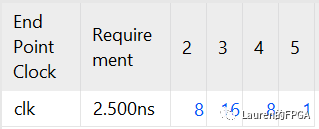

從邏輯級數(shù)的角度看,邏輯級數(shù)最大為5(有一條),大多數(shù)路徑為3,如下圖所示。

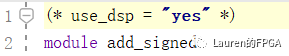

從綜合屬性角度看,可以通過use_dsp屬性使得該加法操作映射到DSP48中,該屬性的使用方法如下圖所示。

采用DSP48實(shí)現(xiàn)時(shí),上述代碼可達(dá)到完全映射,不會(huì)消耗SLICE中的任何資源。假定時(shí)鐘頻率為400MHz,對比使用LUT+FF和DSP48兩種實(shí)現(xiàn)方式,不難看出后者在時(shí)序(邏輯級數(shù)降低至1)和功耗方面均有優(yōu)勢。

-

寄存器

+關(guān)注

關(guān)注

31文章

5433瀏覽量

124427 -

RTL

+關(guān)注

關(guān)注

1文章

389瀏覽量

61081 -

代碼

+關(guān)注

關(guān)注

30文章

4900瀏覽量

70697

原文標(biāo)題:兩個(gè)數(shù)相加,三個(gè)數(shù)相加有什么不同

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

如何使用 SPI 全雙工在兩個(gè) 5LP MPU 之間連接 RAM?

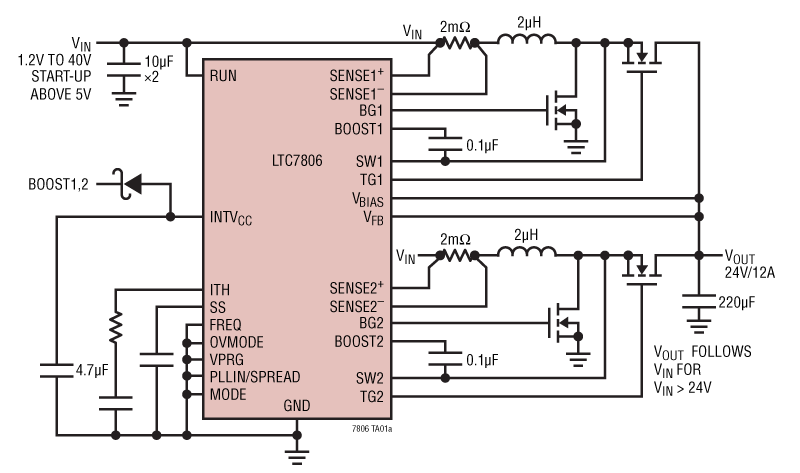

Analog Devices Inc. LTC7806兩相同步升壓控制器數(shù)據(jù)手冊

變頻器相同的故障原因不同的故障代碼分類

數(shù)字電路—14、加法器

STM32H747I DSI模塊采用一個(gè)數(shù)據(jù)通道無法顯示圖片怎么解決?

ADS4149 datasheet里面描述的register map有兩個(gè)地方與實(shí)際測試出來的結(jié)果有出入,求解答

如何把兩個(gè)數(shù)據(jù)返回給調(diào)用函數(shù)

ADS125H01測量結(jié)果在兩個(gè)數(shù)值之間跳變,如何規(guī)避此類問題?

邏輯異或和邏輯或的比較分析

Verilog表達(dá)式的位寬確定規(guī)則

實(shí)現(xiàn)兩個(gè)單一頻率正弦波相加的加法器的芯片選取有什么特殊要求嗎?opa2320可以嗎?

【CAN總線知識(shí)】為什么CAN節(jié)點(diǎn)ID不能相同?

采用RTL代碼描述位寬相同的兩個(gè)數(shù)相加或相減

采用RTL代碼描述位寬相同的兩個(gè)數(shù)相加或相減

評論