繼美光之后,SK海力士宣布完成了業(yè)內(nèi)首款多堆棧176層4D閃存的研發(fā),容量512GB/64GB,TLC。SK海力士透露,閃存單元架構(gòu)為CTF(電荷捕獲),同時(shí)集成了PUC技術(shù)。公司將樣品提供給controller公司去制作解決方案產(chǎn)品

海力士一直在推廣96層NAND Flash產(chǎn)品中的4D技術(shù),該產(chǎn)品將電荷阱閃存(CTF)與高集成度Peri相結(jié)合,并采用單元(PUC)技術(shù)。新的176層NAND閃存是第三代4D產(chǎn)品,從制造上來(lái)說(shuō),其能夠確保業(yè)內(nèi)最佳的每片晶圓產(chǎn)出。與上一代相比,除了容量增加35%,它采用2分裂單元陣列選擇技術(shù)后,單元的讀取速度比上一代提高了20%,在不增加進(jìn)程數(shù)量的情況下,采用加速技術(shù)的數(shù)據(jù)傳輸速度也提高了33%,達(dá)到1.6Gbps。

電荷阱閃光燈(CTF)

與浮柵將電荷存儲(chǔ)在導(dǎo)體中不同,CTF將電荷存儲(chǔ)在絕緣體中,消除了電池之間的干擾,提高了讀寫(xiě)性能,同時(shí)與浮柵技術(shù)相比,減少了單位電池面積。在CTF架構(gòu)中,沒(méi)有浮柵,數(shù)據(jù)被臨時(shí)存放在閃存內(nèi)由氮化硅成的非傳導(dǎo)層,也就是所謂的保持室(Holding Chamber)中,從而可以獲得更高等級(jí)的可靠性與更好的存儲(chǔ)電路的控性。大多數(shù)3D NAND公司正在采用CTF。

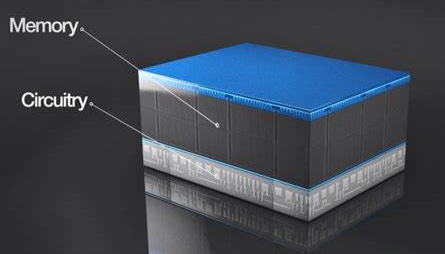

PUC技術(shù)

這是一種通過(guò)在電池陣列下放置外圍電路而使生產(chǎn)效率最大化的技術(shù)。那SK海力士的4D NAND與競(jìng)爭(zhēng)“對(duì)手”3D NAND的區(qū)別是什么呢?SK海力士稱其結(jié)合了自身CTF設(shè)計(jì)與Periphery Under Cell(PUC)技術(shù)。簡(jiǎn)單來(lái)說(shuō),3D閃存由陣列和外圍電路兩個(gè)主要組件組成。與傳統(tǒng)3D NAND相同,SK海力士的陣列是垂直堆疊的層用于存儲(chǔ)數(shù)據(jù),而外圍電路排列在單元邊緣。由電路控制陣列,但隨著NAND層的增加,它就會(huì)消耗芯片空間,增加復(fù)雜性與尺寸大小,由此增加產(chǎn)品的最終成本。

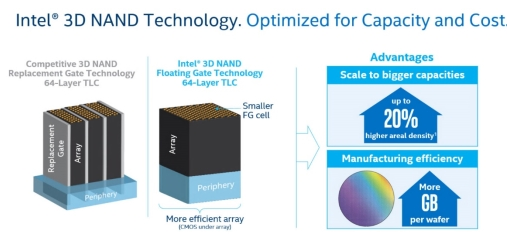

為了解決這一問(wèn)題,SK海力士的4D NAND采用了PUC設(shè)計(jì),將外圍電路放置在陣列之下而不是圍繞,來(lái)提高存儲(chǔ)密度,同時(shí)降低成本。然而,這與英特爾和美光首次推出第一代3D閃存設(shè)計(jì)相同,那邊稱之為“CMOS under Array”(CuA)。并且,三星也已經(jīng)宣布其將來(lái)會(huì)轉(zhuǎn)向CuA型設(shè)計(jì),因此這絕不能算是新技術(shù)了。

2分單元陣列選擇技術(shù)(2-division cell array selection technology)

字線在NAND閃存電路中向電池施加電壓。層數(shù)越多,字線越薄,就會(huì)降低細(xì)胞的高度,對(duì)字線的電阻越大,就會(huì)影響速度。通過(guò)將連接字線的電池與現(xiàn)有的電池相比分成兩部分,可以降低電阻,從而縮短施加電壓的時(shí)間,提高讀取速度。

電池層間高度降低技術(shù)

隨著層數(shù)的增加,通過(guò)鉆孔形成存儲(chǔ)單元就會(huì)變得困難。這導(dǎo)致電阻增加,電流減少,難以保證性能和可靠性。為此,這就需要盡可能降低單元間層的高度,但這會(huì)增加單元間的干擾和缺陷率。電池層間高度降低技術(shù)不僅大幅降低了176層的電池層間高度,而且通過(guò)相關(guān)工藝和設(shè)計(jì)技術(shù)確保了具有競(jìng)爭(zhēng)力的性能/可靠性。

層變定時(shí)控制技術(shù)

增加層數(shù)和降低層高往往會(huì)導(dǎo)致通道孔扭曲和單元散射惡化,從而降低每一層的性能和可靠性。該技術(shù)根據(jù)每層的特性調(diào)整施加電壓的數(shù)量和時(shí)間,以保持均勻的電池特性,提高了性能和可靠性。

超精密定位技術(shù)

由于隨著層數(shù)的增加,不可能一次鉆出用于單元形成的孔,所以使用兩次鉆出孔的雙堆疊工藝。雙堆疊技術(shù)的核心是使堆疊誤差最小化。如果堆棧沒(méi)有正確對(duì)齊,將導(dǎo)致堆棧之間的電流流動(dòng)不順暢,并發(fā)生惡化,降低成品率、性能和可靠性。SK海力士自2017年推出72層的產(chǎn)品以來(lái),就一直在使用雙堆疊技術(shù),對(duì)176層產(chǎn)品進(jìn)行了改進(jìn),并基于自身的專業(yè)知識(shí),實(shí)時(shí)自動(dòng)校正孔的位置和尺寸。

存儲(chǔ)廠商們各自努力,176層頂峰見(jiàn)實(shí)力

在全球NAND市場(chǎng)份額中,雖然美光排在第七位,但是在堆疊能力方面,美光卻毫不遜色。美光是第一家發(fā)布176層3D NAND的存儲(chǔ)廠商,其第五代3D NAND閃存是176層構(gòu)造,這也是自美光與英特爾的存儲(chǔ)器合作解散以來(lái)推出的第二代產(chǎn)品。2020年11月9日,美光宣布將批量發(fā)售世界上第一個(gè)176層3D NAND。

據(jù)美光官網(wǎng)介紹,該176層NAND采用了獨(dú)特的技術(shù),替換門(mén)架構(gòu)將電荷陷阱與CMOS陣列下(CuA)設(shè)計(jì)相結(jié)合,與同類最佳競(jìng)爭(zhēng)產(chǎn)品相比,其die尺寸減小了約30%。

三星電子作為全球NAND領(lǐng)導(dǎo)者,占有33.8%的市場(chǎng)份額,如果三星想在很長(zhǎng)一段時(shí)間內(nèi)保持這一頭把交椅,就必須始終走在前面。三星電子計(jì)劃在2021年上半年大規(guī)模生產(chǎn)具有170層或更多層的第七代V-NAND閃存,并將使用字符串堆疊方法,結(jié)合兩個(gè)88L模具,新芯片還將采用“雙棧”技術(shù)。行業(yè)觀察家表示,由于三星電子改變了其堆疊方法,該產(chǎn)品的發(fā)布已被推遲。

西部數(shù)據(jù)于今年1月份宣布,它已經(jīng)成功開(kāi)發(fā)了其第五代3D NAND技術(shù)BiCS5,BiCS5設(shè)計(jì)使用112層,而B(niǎo)iCS4使用96層。

長(zhǎng)江存儲(chǔ)進(jìn)步非凡,他們堅(jiān)持創(chuàng)新發(fā)展,走差異化的路線,于2018年7月正式推出自家的獨(dú)門(mén)絕技Xtacking?架構(gòu)。傳統(tǒng)3D NAND架構(gòu)中,外圍電路約占芯片面積的20~30%,降低了芯片的存儲(chǔ)密度。隨著3D NAND技術(shù)堆疊到128層甚至更高,外圍電路可能會(huì)占到芯片整體面積的50%以上。Xtacking?技術(shù)將外圍電路置于存儲(chǔ)單元之上,從而實(shí)現(xiàn)比傳統(tǒng)3D NAND更高的存儲(chǔ)密度。2020年4月,長(zhǎng)江存儲(chǔ)搶先推出了128層QLC 3D NAND閃存芯片X2-6070。目前長(zhǎng)江存儲(chǔ)的技術(shù)已經(jīng)處于全球一流的水準(zhǔn),下一步就是解決產(chǎn)能的問(wèn)題。

編輯:hfy

-

NAND

+關(guān)注

關(guān)注

16文章

1719瀏覽量

137821 -

三星電子

+關(guān)注

關(guān)注

4文章

570瀏覽量

40715 -

SK海力士

+關(guān)注

關(guān)注

0文章

991瀏覽量

39332 -

長(zhǎng)江存儲(chǔ)

+關(guān)注

關(guān)注

5文章

325瀏覽量

38259

發(fā)布評(píng)論請(qǐng)先 登錄

SK海力士UFS 4.1來(lái)了,基于321層1Tb TLC 4D NAND閃存

SK海力士已完成收購(gòu)英特爾NAND業(yè)務(wù)部門(mén)的第二(最終)階段交易

SK海力士完成業(yè)內(nèi)首款多堆棧176層4D閃存集成PUC技術(shù)研發(fā)

SK海力士完成業(yè)內(nèi)首款多堆棧176層4D閃存集成PUC技術(shù)研發(fā)

評(píng)論