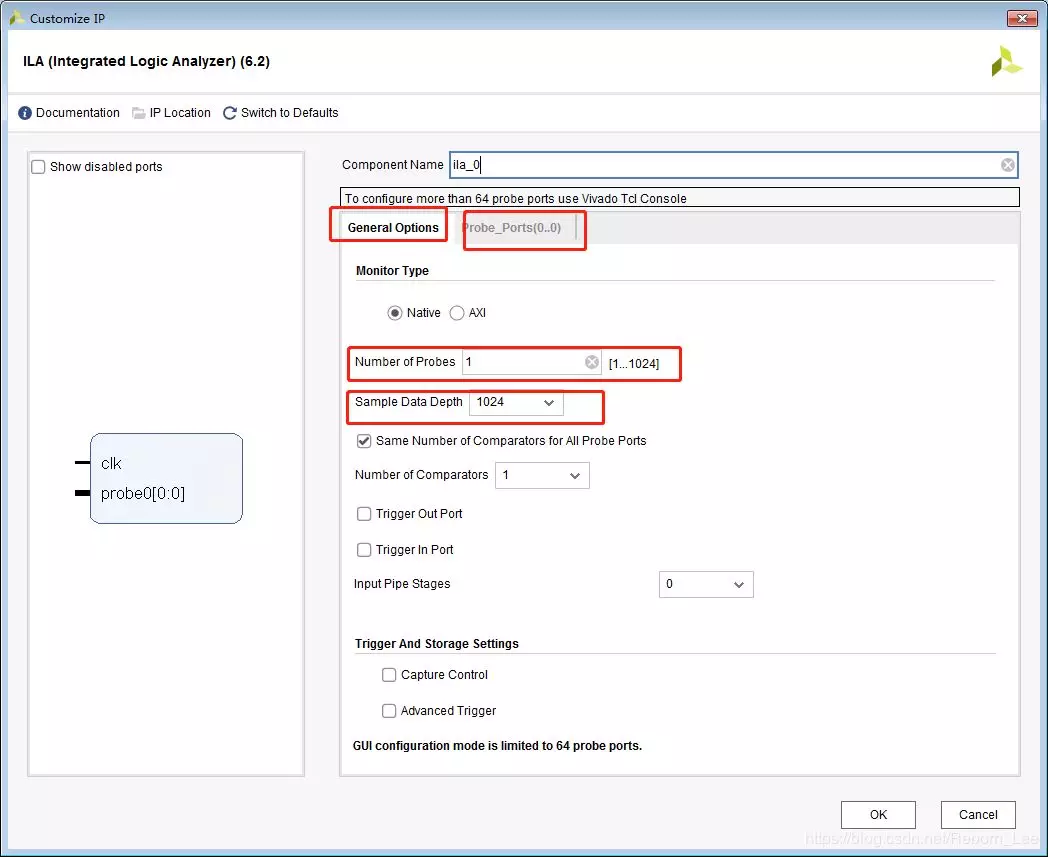

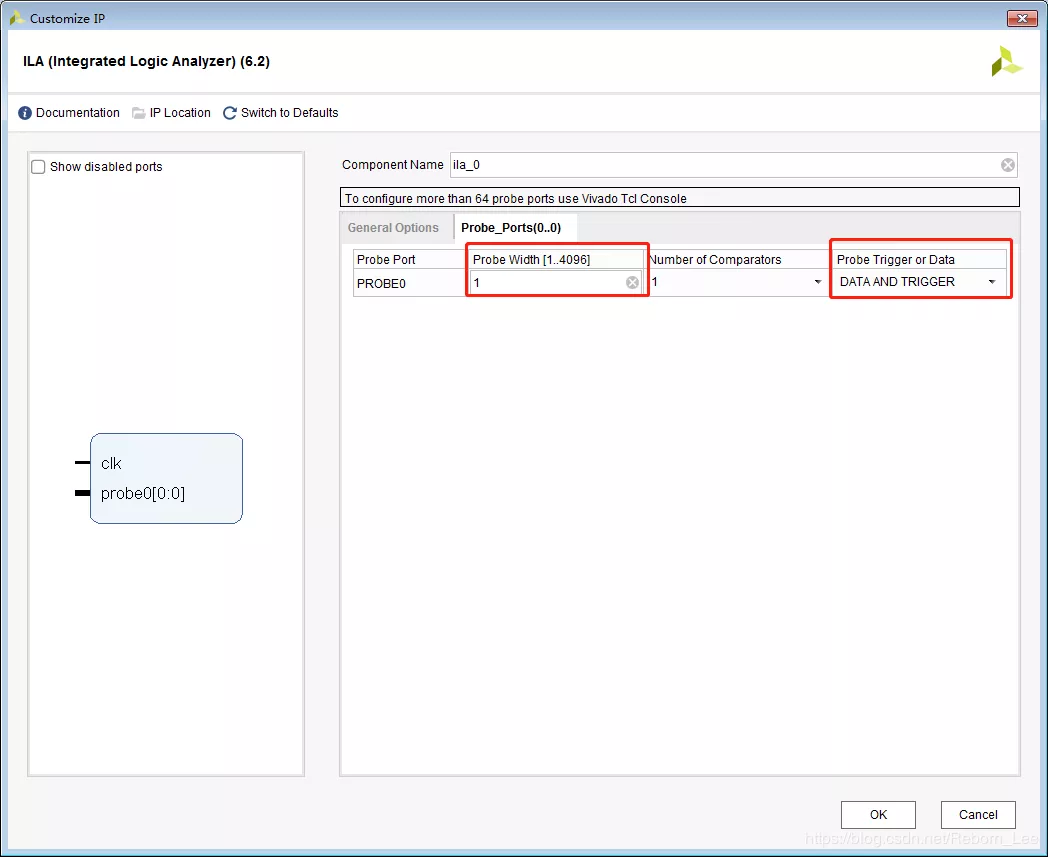

下面界面可以選擇探測信號寬度以及觸發方式:

可謂之簡單粗暴,如果沒人干預你,就這樣用也沒關系。之后直接在程序中例化即可。

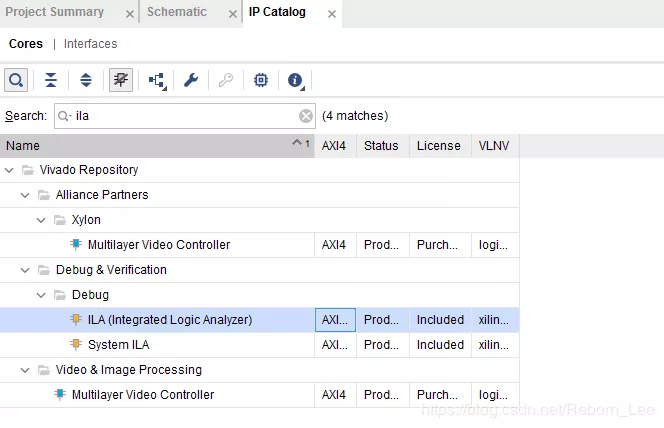

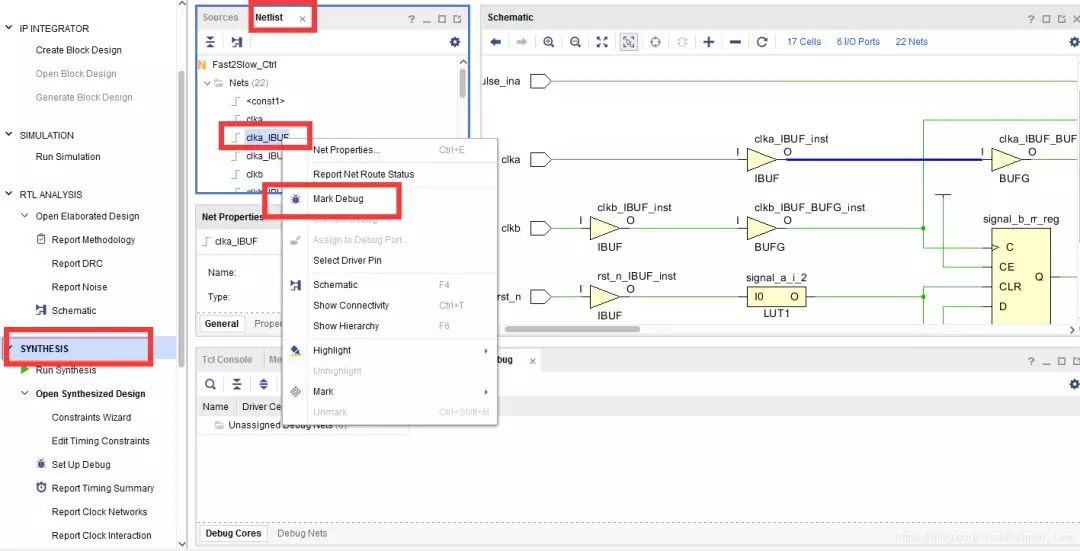

2. 通過網表標記

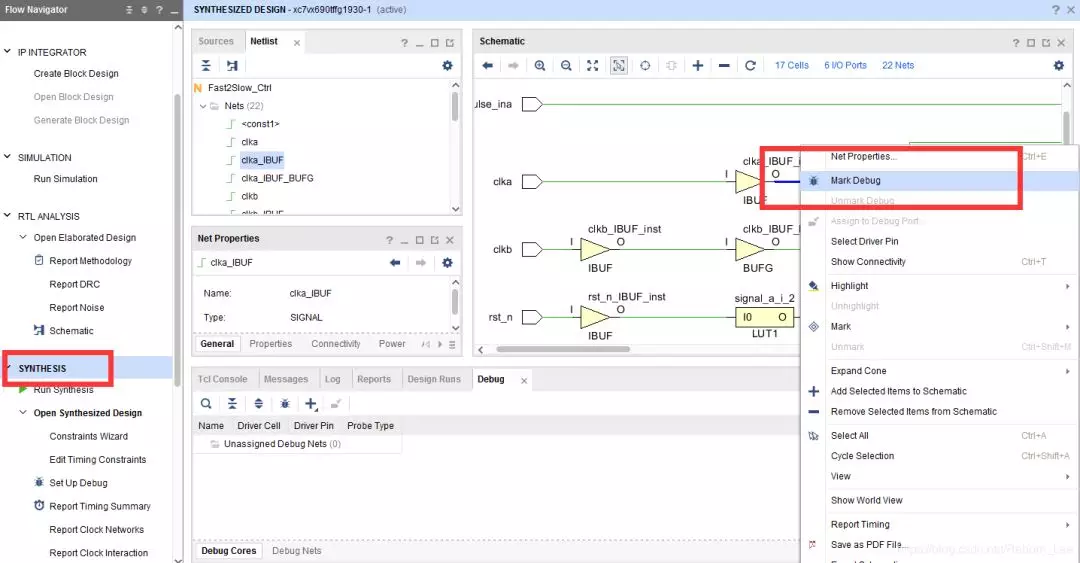

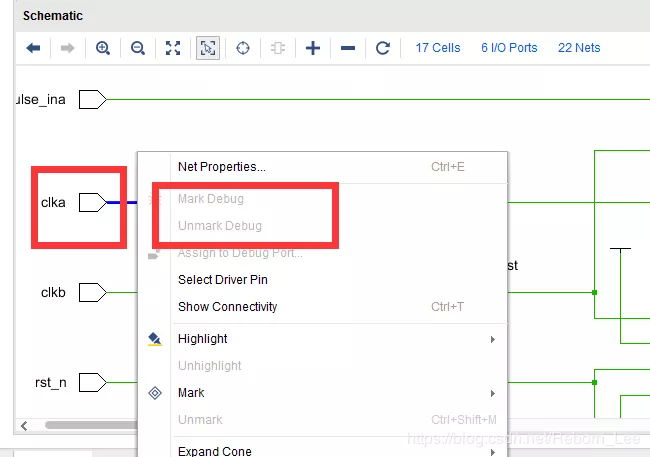

綜合后生成網表,在網表中設置Debug:Mark Debug。

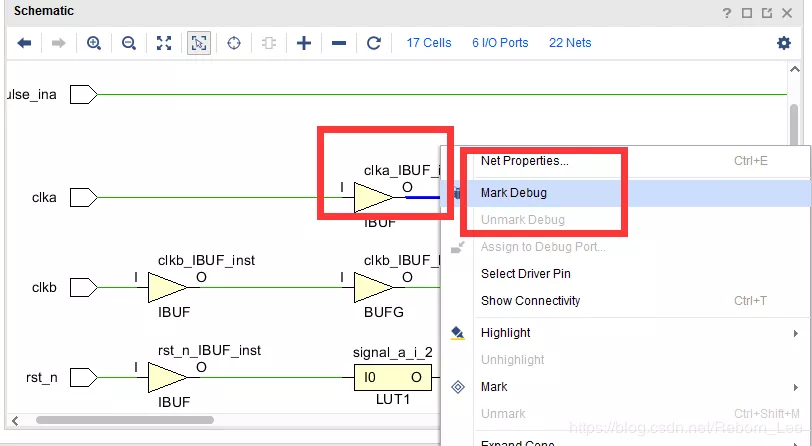

或者在綜合后的原理圖中Mark Debug,這和網表debug是一致的:

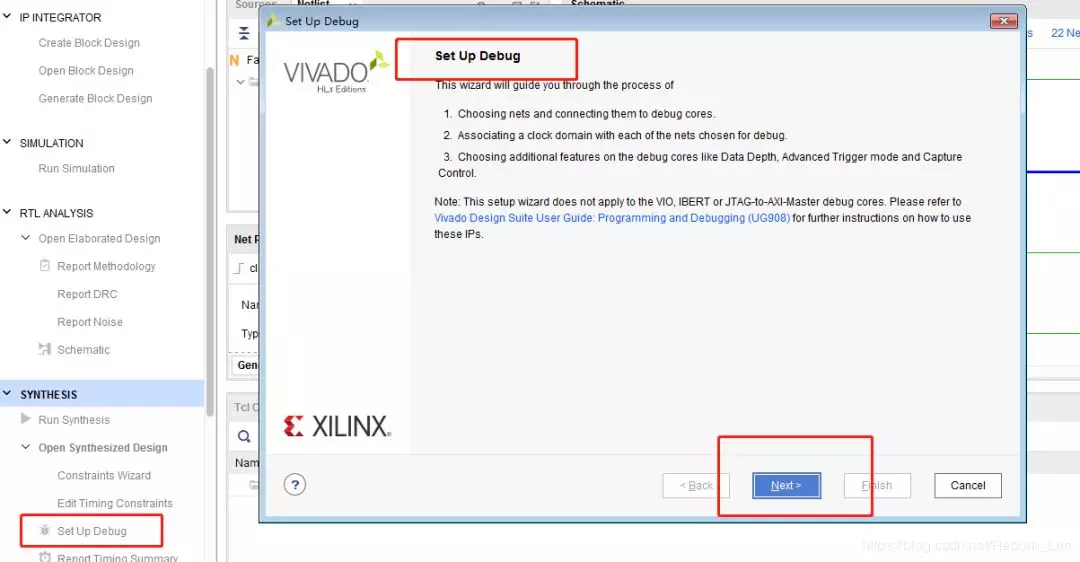

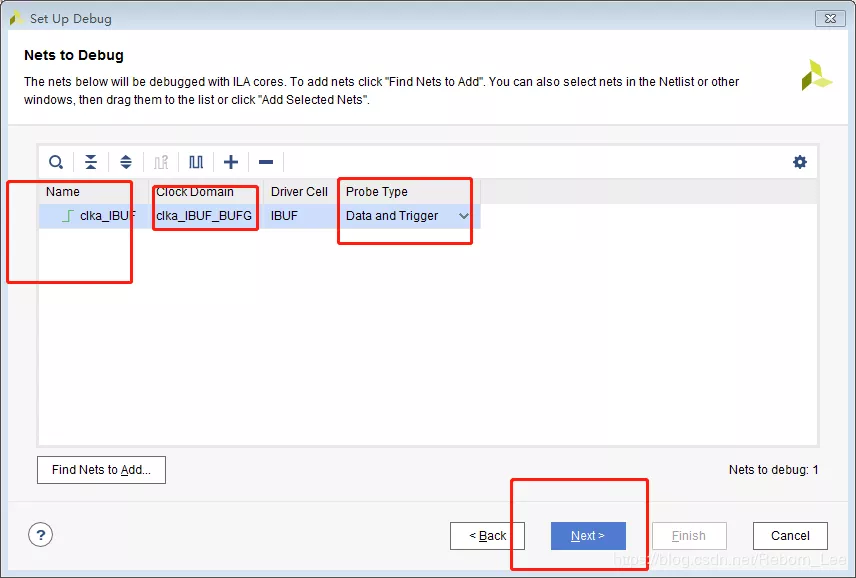

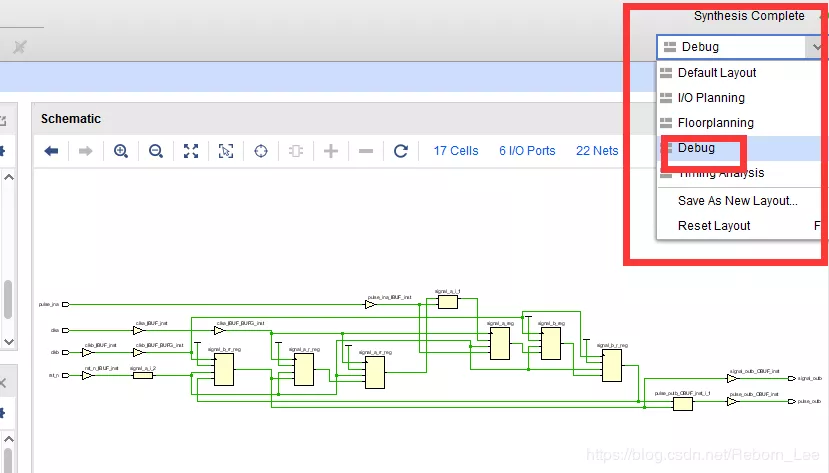

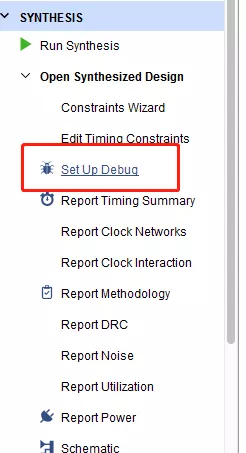

在標記Debug后,就等于選擇了需要debug的信號,之后在綜合設置里設置Debug參數即可:

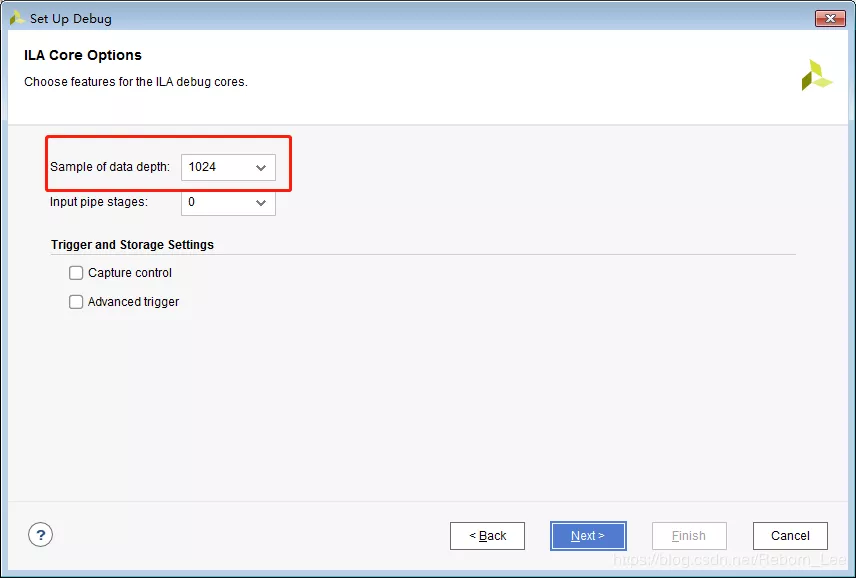

選擇采樣深度:

之后,重新綜合,實現生成bit流文件即可完成debug,準備上板子吧。

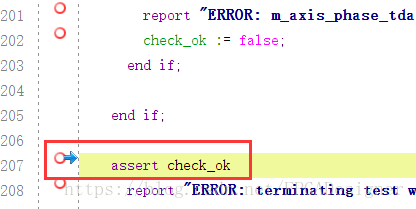

注意:有些信號能夠Mark Debug,有些則不能,例如模塊直接的輸入信號不能:

它經過一個Buf之后就可以:

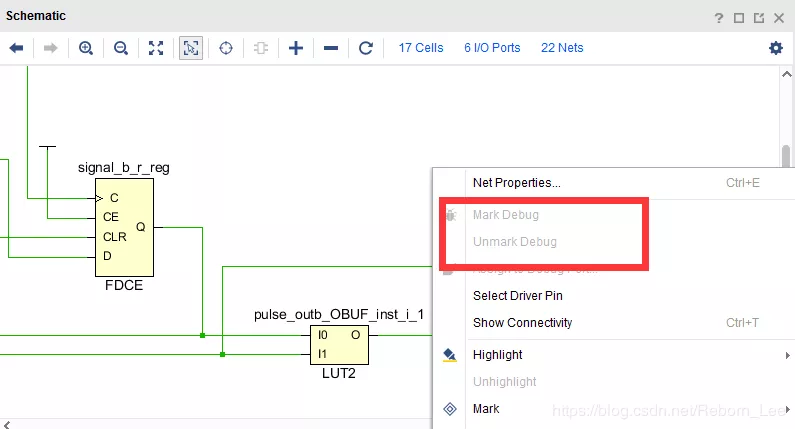

最后的輸出也不能?

哎呀, 具體什么個原則我也不知道了,不如就直接在網表中試試吧,如果不行,就找類似的代替唄。

綜合后,也許你說自己找不到原理圖在哪里,那就看這里:

方式二已經很實用了吧,不用修改代碼!

3. 代碼中Mark_debug

第三種還要在代碼中加入標記:

之后綜合,在set up debug,之后的操作同方式二。

編輯:hfy

-

DEBUG

+關注

關注

3文章

94瀏覽量

20371 -

Vivado

+關注

關注

19文章

828瀏覽量

68217

發布評論請先 登錄

FPGA中三種常用復位電路

詳細解讀Zynq的三種啟動方式(JTAG,SD,QSPI)

Vivado中使用debug工具步驟與調試技巧

Vivado使用技巧:debug仿真設計的三種調試方法

一文解析Vivado的三種封裝IP的方式

關于Vivado中三種操作Debug的方式

關于Vivado中三種操作Debug的方式

評論