源代碼級別調(diào)試

Vivado Simulator提供了在仿真過程中debug設(shè)計的特性,通過為源代碼添加一些可控制的執(zhí)行條件來檢查出問題的地方。總的來說有三種調(diào)試方法:

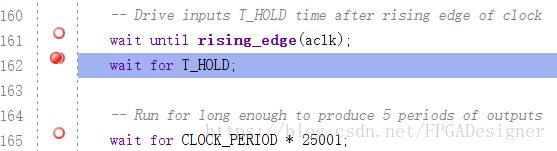

1.使用Step逐行調(diào)試

Step命令一次只執(zhí)行HDL代碼中的一行,從而驗證和調(diào)試設(shè)計。運行仿真后,點擊Run->Step或工具欄中的Step可執(zhí)行該命令。Restart可以將時間復(fù)位到TestBench的開始。當(dāng)前執(zhí)行的代碼會高亮顯示并且前方有箭頭指示:

運行Step后會打開與頂層設(shè)計單元相關(guān)的HDL文件窗口,在窗口名稱上右鍵->新建水平分組或新建垂直分組即可同時查看HDL和波形窗口。

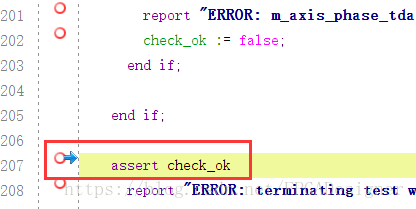

2.使用斷點(breakpoint)調(diào)試

Step調(diào)試的缺點是在大型設(shè)計中很繁瑣且花費大量時間。設(shè)計者可以在源代碼中自行指定運行停止的點,稱為斷點。運行仿真時,仿真器遇到斷點就會暫停。可設(shè)置斷點的行前有一個空心圈,點擊可設(shè)置斷點,轉(zhuǎn)變?yōu)閷嵭娜Α?/p>

對應(yīng)的Tcl命令為“add_bp file_name line_number”。仿真調(diào)試過程中,斷點和Step調(diào)試是可以一起使用的。在實心圈上右鍵,或Run菜單中點擊Delete All Breakpoints可以刪除所有斷點。

3.條件調(diào)試

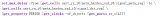

在設(shè)計中添加條件斷點,仿真器檢測到條件為真時就會暫停當(dāng)前仿真。條件必須用Tcl命令添加,示例如下:

add_condition #命令模板

add_condition {reset == 1 && clk == 1} {puts “Reset went to high”; stop}

#當(dāng)clk與reset同時為高暫停仿真,控制臺打印消息輸出

遇到條件斷點并暫停后,只有等到下一個仿真命令才會繼續(xù)運行仿真。

將對象強制到特定值

Vivado Simulator提供了Force功能將信號、wire或reg強制為某一值,該操作會重寫信號定義在HDL設(shè)計中的行為。考慮如下應(yīng)用情況:

- TestBench中沒有對某一信號進行驅(qū)動,可以使用Force功能給予激勵;

- Debug過程中使用Force糾正錯誤的值,以繼續(xù)進行仿真分析。

使用Force Constant、Force Clock、Remove Clock相關(guān)命令配置Force功能,而且仿真restart后仍然會保留已經(jīng)設(shè)置了的Force特性。

1.Force Constant功能

該命令會將信號固定為一個常數(shù)值,重寫了其HDL代碼中的賦值。在Objects窗口或波形窗口中選中某一對象,右鍵->Force Constant,打開如下窗口:

Force value按照value radix選擇的基數(shù)設(shè)置常數(shù)值;設(shè)置的值開始于Starting after time offset設(shè)置的時間,如果不帶單位則默認為ns;Cancel after time offset設(shè)置的時間后會取消應(yīng)用Force功能。

2.Force Clock功能

該命令會使信號以一定速率在兩個值之間來回轉(zhuǎn)換,類似于時鐘信號一樣(但不局限于生成時鐘信號,可以定義任意振蕩的值)。在Objects窗口或波形窗口中選中某一對象,右鍵->Force Constant,打開如下窗口:

Leading edge value和Trailing edge value分別指定兩個振蕩狀態(tài)的值;Duty cycle和Period設(shè)置占空比和周期。右鍵菜單中的Remove Force用來清除設(shè)置。靈活使用Force特性可以加快設(shè)計仿真的調(diào)試驗證,而不需要修改HDL代碼。

編輯:hfy

-

vhdl

+關(guān)注

關(guān)注

30文章

819瀏覽量

129461 -

DEBUG

+關(guān)注

關(guān)注

3文章

94瀏覽量

20342 -

Vivado

+關(guān)注

關(guān)注

19文章

828瀏覽量

68069

發(fā)布評論請先 登錄

ARM的三種中斷調(diào)試方法

【分享資料】ARM的三種中斷調(diào)試方法簡介

ARM的三種中斷調(diào)試方法介紹

三種電路仿真軟件比較及器件模型加入方法

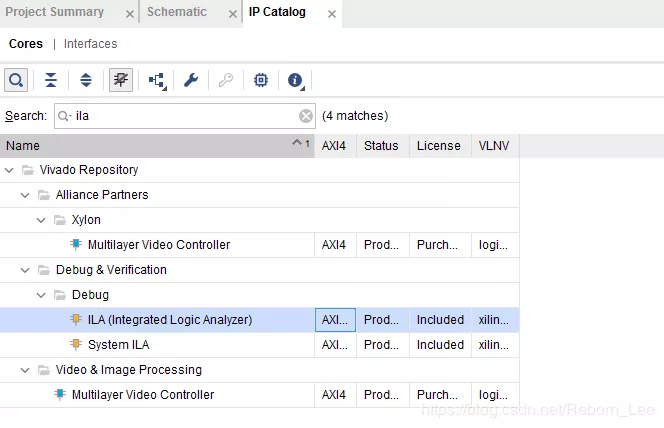

Vivado+FPGA:如何使用Debug Cores(ILA)在線調(diào)試

Vivado中使用debug工具步驟與調(diào)試技巧

基于Proteus嵌入式仿真平臺中三種源碼調(diào)試的方式分析

如何使用Vivado Logic Analyzer與邏輯調(diào)試IP進行交互

Vivado調(diào)試ILA debug結(jié)果也許不對

關(guān)于Vivado中三種操作Debug的方式

一文解析Vivado的三種封裝IP的方式

FPGA應(yīng)用之vivado三種常用IP核的調(diào)用

MCUXpresso IDE下在線聯(lián)合調(diào)試雙核MCU工程的三種方法

Vivado使用技巧:debug仿真設(shè)計的三種調(diào)試方法

Vivado使用技巧:debug仿真設(shè)計的三種調(diào)試方法

評論