在VLSI 2020上,IMEC發表了有關單片CFET的有趣論文,我有機會采訪了其中一位作者Airoura Hiroaki。在業界眾所周知,FinFET(FF)即將達到其定標壽命。

三星已經宣布,他們將在3nm的時候轉向水平納米片(Horizontal Nanosheets :HNS)。臺積電(TSMC)保持3nm的FF,但預計將轉移到2nm的新架構。

假設英特爾當時仍在追求自己的技術,則預計英特爾將保留7nm的FF,然后再遷移至5nm的HNS。

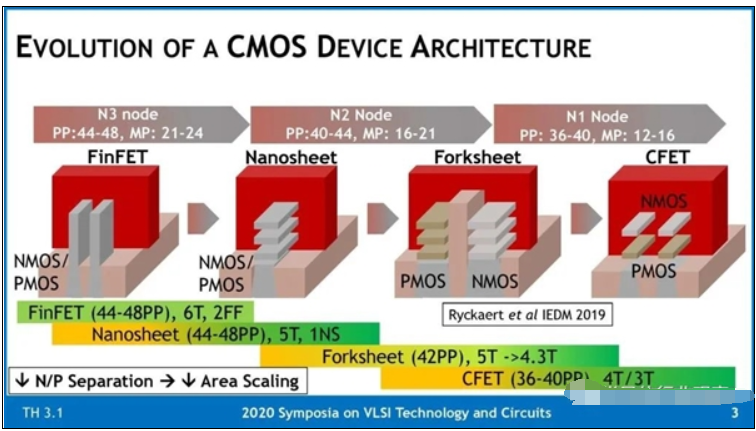

該行業最可能的路線圖是從FF到帶有或不帶有Forksheets的HNS,然后過渡到CFET(Complimentary FETs),請參見圖1。

Imec CMOS路線圖。

從以上技術藍圖來看,28納米使用了High-K/Metal Gate,16納米---14納米導入了FinFET,7納米---5納米采用了EUV曝光設備,此外,還將Co應用于Middle of Line(MOL)上。

MOL是一種將晶體管(FOEL)與多層配線(BEOL)連接在一起的孔(Via),雖然imec使用了Co,還有其他選擇項如Mo、Ru等。

此外,4納米---3納米中采用了具有Nanosheet結構的晶體管。

此次的VLSI座談會上,有關7納米、5納米、3納米的文章發布得比較多,然而,筆者卻發現將Gate All Around(GAA)的Nanosheet結構應用在這些節點上的情況是全球共通的認知。

同時從技術藍圖看,在2納米中,使用搭載了Buried Power Rail(BPR,在晶體管下埋入電源線的構造)的Forksheet晶體管;在1納米中,將會使用采用了BPR的Complementary FET(CFET)。

imec在其內部達成了以下共識:3納米之前采用Nanosheet、2納米采用Forksheet、1納米采用CFET。

也就是說,在此次VLSI座談會上,imec也是基于以上技術藍圖而做的發表。從上圖可以清晰地看出FinFET、Nanosheet、Forksheet、CFET的結構變化。

從FinFET到CFET,通過將Contact Poly Pitch(PP)做到最小、分離nMOS和pMOS,以達到縮小SRAM面積的效果。

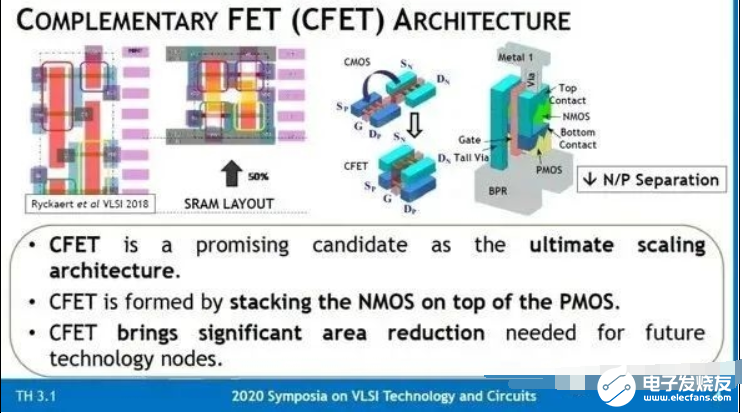

Forksheet 和CFET通過堆疊nFET和pFET器件的CFET改善n到p的間距來縮小尺寸,見圖2。

CFET結構在當前的工作中,已經開發了“單片”(monolithic) CFET,方法是將單獨的硅片用于nFET和pFET,然后將它們粘合在一起,而按照順序(sequential),CFET則會將兩種類型的FET都制造在同一硅片上。

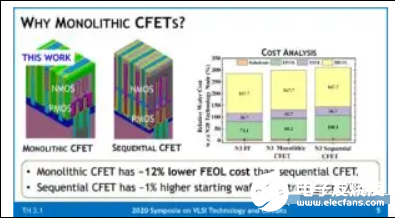

Imec聲稱單片技術比順序技術便宜,而順序技術要求SOI會增加襯底成本1%,見圖3。

單片CFET的成本優勢在1納米中,IMEC采用了將nMOS和pMOS縱向排列的CFET(如下圖8),雖然CFET的工藝流程非常復雜,但毫無疑問,極大地縮小了CMOS、SRAM的面積,達到了集成化。

問題是---是否做到了人們所期待的晶體管的特性,這是未來研發的關鍵。

我發現起始晶圓成本高出約1%,這有兩個原因,一是,我不相信順序CFET需要SOI,二是,SOI比標準晶圓貴了約1%。整體方法還將需要兩個起始晶圓,而不僅僅是一個。

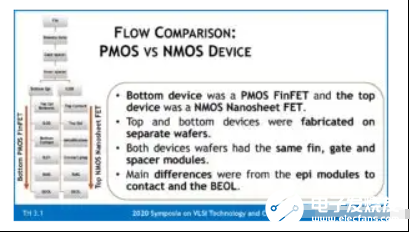

我認為這種成本分析需要更多的調查。在單片方法中,nFET和pFET在分離的晶圓上制造,從而可以針對該器件優化每個器件的制造流程。每個晶片的處理流程如圖4所示。

圖4.單片CFET的工藝流程。

隨著我們朝N3方向發展,n到p的分離減少了寄生效應并提高了性能。同樣,通過從FF移至GAA)可以在所有四個側面而不是三個側面上提供一個柵極,從而改善了靜電控制。

這項工作中制造的單片CFET為下一代器件提供了順序CFET的替代方案,需要進一步研究。

責編AJX

-

芯片

+關注

關注

459文章

52481瀏覽量

440558 -

半導體

+關注

關注

335文章

28886瀏覽量

237498 -

晶體管

+關注

關注

77文章

10018瀏覽量

141594

發布評論請先 登錄

下一代高速芯片晶體管解制造問題解決了!

跨越摩爾定律,新思科技掩膜方案憑何改寫3nm以下芯片游戲規則

芯片巨頭們已開始研發小于3nm CPU技術,或采用升級CFET晶體管

芯片巨頭們已開始研發小于3nm CPU技術,或采用升級CFET晶體管

評論