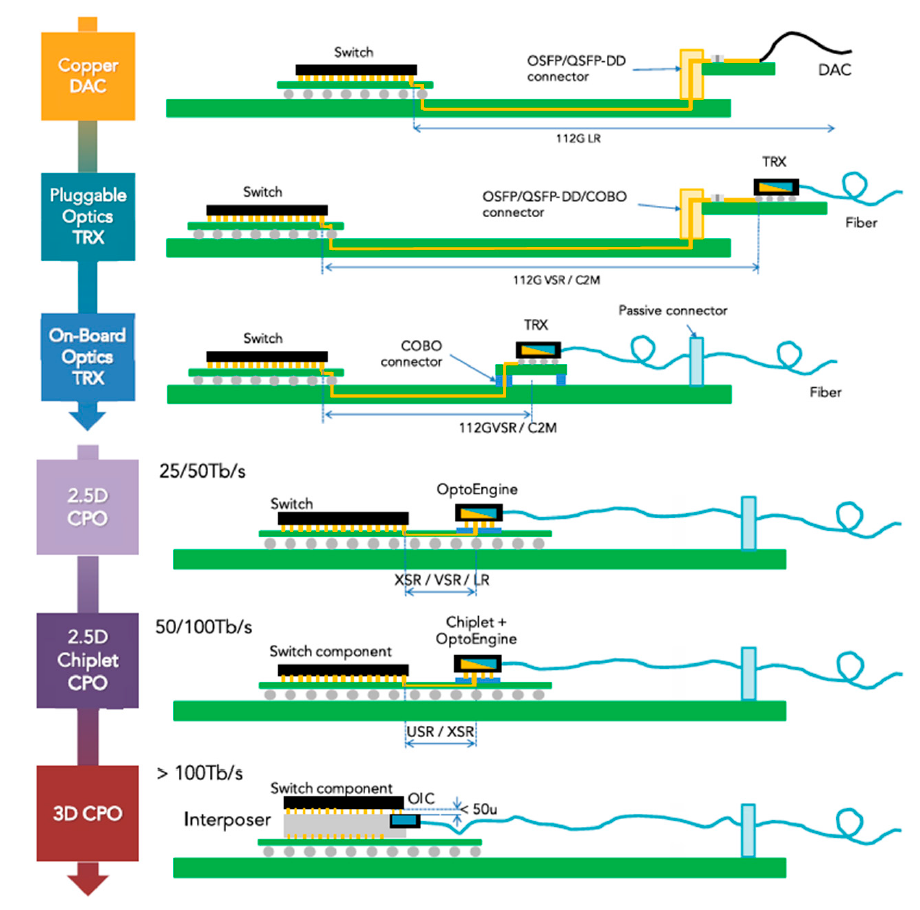

在三個關鍵系統(tǒng)模塊(處理器,內存和互連(I/ O))之間需要互相協(xié)調,每個要都在更好的提升性能。隨著按各種指標衡量的處理器和內存速度已得到了大幅提高,所以互連也需要跟上發(fā)展,以免整體性能被卡了脖子!但是銅纜鏈路正面臨著一些明顯的障礙。電光互連似乎是解決方案,但要使其發(fā)揮潛能并與硅一起工作一直是一個重大挑戰(zhàn)。 不過,最近有一次演示展示了英特爾與Ayar Labs(加利福尼亞州埃默里維爾)之間的合作所取得的巨大進步,該項目是由美國國防高級研究計劃局(DARPA)在其“光子學”中贊助的。該計劃希望使用先進的封裝內硅光子接口來實現每秒1T位(Tb / s)以上的數據速率,同時所需的能耗不到1皮焦耳/bit。并能實現千米級的傳輸距離(圖1)。

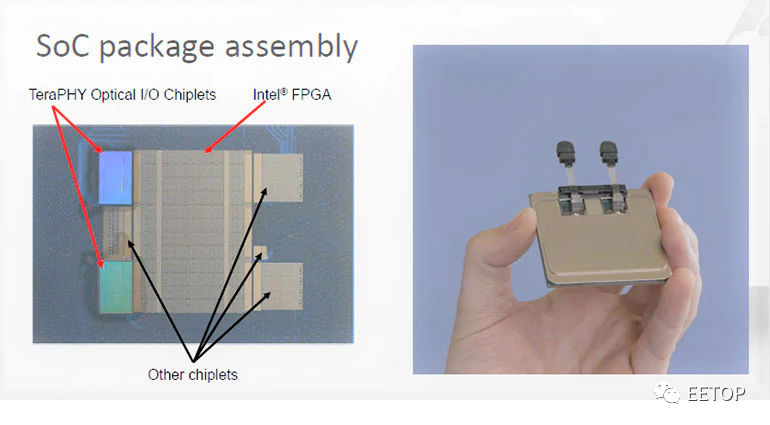

SoC器件顯示(左)各個小芯片的位置以及完整的封裝(右)。

英特爾/ Ayar項目尚未實現這些目標,但確實朝著這些目標邁出了重要一步。在2020年光纖會議(OFC)上的線上演示中,Ayar展示了其TeraPHY光學芯片技術,該技術已集成到通常使用銅互連的改進型商用IC(英特爾Stratix 10 FPGA)中(圖2)。

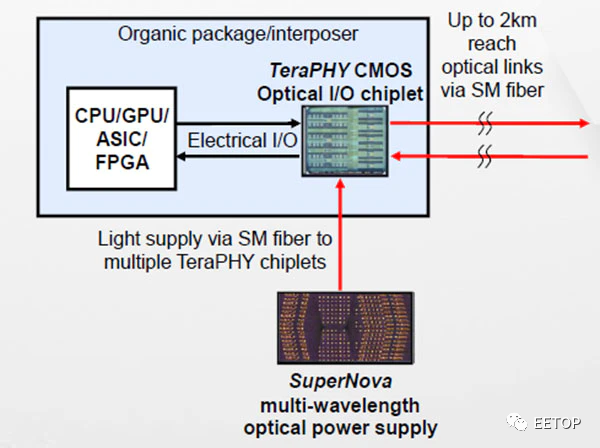

這是一種非常高級的光學I / O系統(tǒng)架構,圖片顯示了主要組件的互連

從硅電子中產生光數據流并不僅僅是先進的LED、激光二極管、增強摻雜或獨特的制造結構的問題,盡管這些結構都具有更高的性能和扭曲度。。相反,它需要一種新的思維方式,需要先進的深層電光物理學見解,其中涉及合適結構中電子、電場和光子之間的關系。

利用硅光子技術

基本設計是基于使用硅光子學作為構件,包括波導、定向耦合器和微環(huán)諧振器。與廣泛使用的馬赫-曾德爾干涉儀(MZI)相比,后者是耦合和能量傳輸的首選,因為它提供了大約縮小100倍的小尺寸,25-50倍的高帶寬密度和50倍的高能量效率。然而,它也需要更復雜的設計和精密制造。

Ayar公司的TeraPHY芯片片采用GlobalFoundries公司的45-nm SOI CMOS制造工藝制造,該芯片集成了微米級的光波導。TeraPHY芯片上的光波導被蝕刻在硅片中,提供的功能是基于銅的能量和信號路徑的光學模擬。將兩個波導靠近,就能將光子和功率從一個波導轉移到另一個波導,從而形成一個能量耦合器。在耦合器內,一個直徑為10微米的微環(huán)諧振器可以對相位進行電調制,并控制光的方向,要么通過芯片,要么直至芯片頂部,從而創(chuàng)建I/O端口。

TeraPHY平臺由單片集成的硅光子和CMOS組成(圖3),采用倒裝片系統(tǒng)封裝(SiP),可將一個SoC的綜合功能拆分在一個封裝的多個小芯片上。這些小芯片采用密集、節(jié)能、短距離的封裝內電氣互連方式互連在一起。

圖片展示了一個TeraPHY芯片的例子,顯示了16通道25G光子發(fā)射(Tx)和接收(Rx)宏以及相應的串行器/解串器(SerDes)(a)。多芯片模塊(b)的分解圖包括一個系統(tǒng)級芯片裸片和兩個TeraPHY芯片。(來源:Ayar Labs)

SiP技術的主要優(yōu)勢在于能夠使每個小芯片提供不同的專門功能,并使用最適合實現該功能的工藝技術進行制造,只要該小芯片仍可以符合標準的SiP集成和封裝約束。這類似于在SiP中使用高密度CMOS來制作處理器或FPGA,再加上專業(yè)的模擬處理來實現精密數據采集和調理。

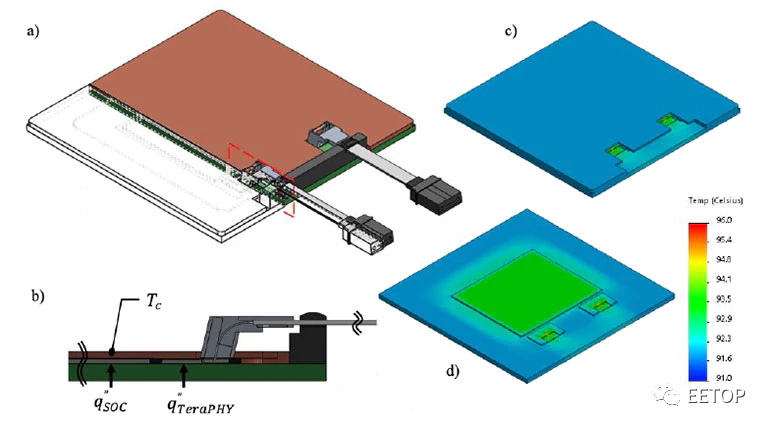

盡管目標為1pJ / bit,但在這種類型的設計中,散熱方面的考慮與電子和光學方面的考慮一樣重要,因為SoC耗散了300W,TeraPHY耗散4.7W。分析表明,解決TeraPHY耗散問題的實用解決方案將其分為TxRx,電氣I/O和GPIO區(qū)域。

當然,封裝也是分析的一部分,所得到的溫度曲線說明了高性能系統(tǒng)中預期的熱環(huán)境(圖4)。盡管CMOS器件可以承受這些工作溫度,但任何共封裝的激光器都將降低效率并降低可靠性,因此TeraPHY被設計為使用外部激光源。

圖4是多芯片模塊(MCM)的等距剖視圖

這里只是對一個非常復雜技術做一個簡單的描述。更多的可以參考這方面的相關論文:

https://ayarlabs.com/teraphy-a-high-density-electronic-photonic-chiplet-for-optical-i-o-from-a-multi-chip-module/#unlock

https://ayarlabs.com/teraphy-a-chiplet-technology-for-low-power-high-bandwidth-in-package-optical-i-o/

-

處理器

+關注

關注

68文章

19863瀏覽量

234401 -

CMOS

+關注

關注

58文章

6006瀏覽量

238594 -

英特爾

+關注

關注

61文章

10190瀏覽量

174378 -

電光

+關注

關注

0文章

10瀏覽量

8290

原文標題:解決芯片互連卡脖子問題:CMOS片上光電互連速度突破2Tb/s!

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

互連層RC延遲的降低方法

分享兩種前沿片上互連技術

SlaveFifo 2bit sync模式下最大速度只有320Mbyte/s左右,還能更快一點嗎?

光電共封裝技術CPO的演變與優(yōu)勢

突破存儲形態(tài)與邊界!佰維全新Mini SSD震撼發(fā)布,引領端側智能時代存儲新范式!

硅基波導集成的片上光譜儀綜述

利用東芝TB67S179FTG提升運動控制性能:工程師綜合指南

2TB內置機械硬盤的適用場景有哪些

蘋果計劃在2026年iPhone上啟用2TB存儲,QLC NAND閃存成關鍵

單顆256GB,單一封裝達4TB容量,鎧俠第八代BiCS FLASH 2Tb QLC開始送樣

中國信科實現國內首款2Tb/s三維集成硅光芯粒成功出樣

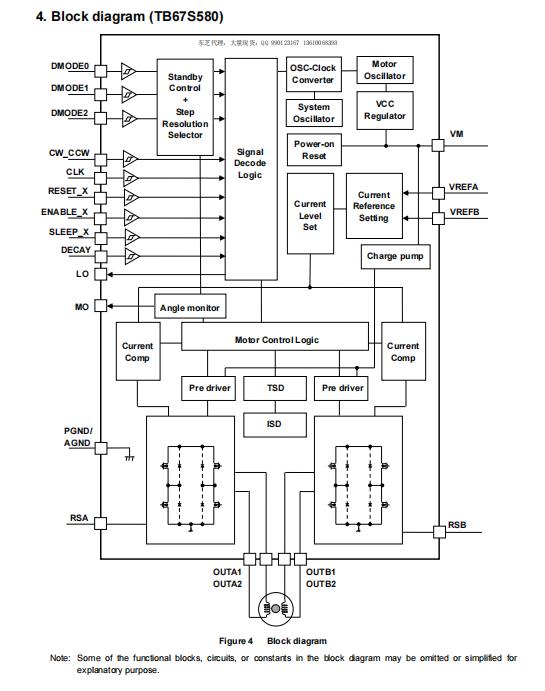

介紹東芝 TB67S580FNG:理想的雙極步進電機控制解決方案

鎧俠推出業(yè)界首款2Tb QLC存儲器,引領存儲技術新紀元

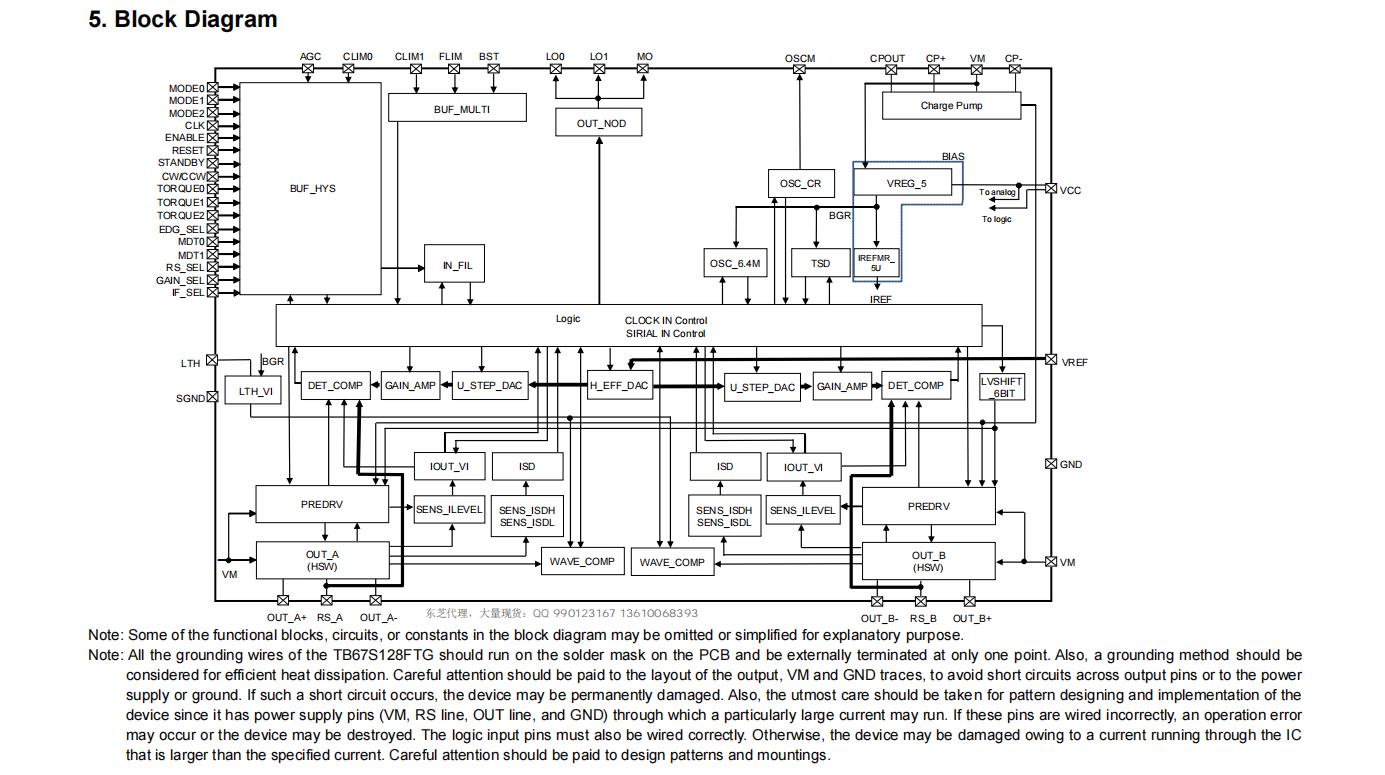

東芝 TB67S128FTG:釋放精密電機控制的力量

TB67S539FTG:先進的2相雙極步進電機驅動器

CMOS片上光電互連速度突破2Tb/s!

CMOS片上光電互連速度突破2Tb/s!

評論