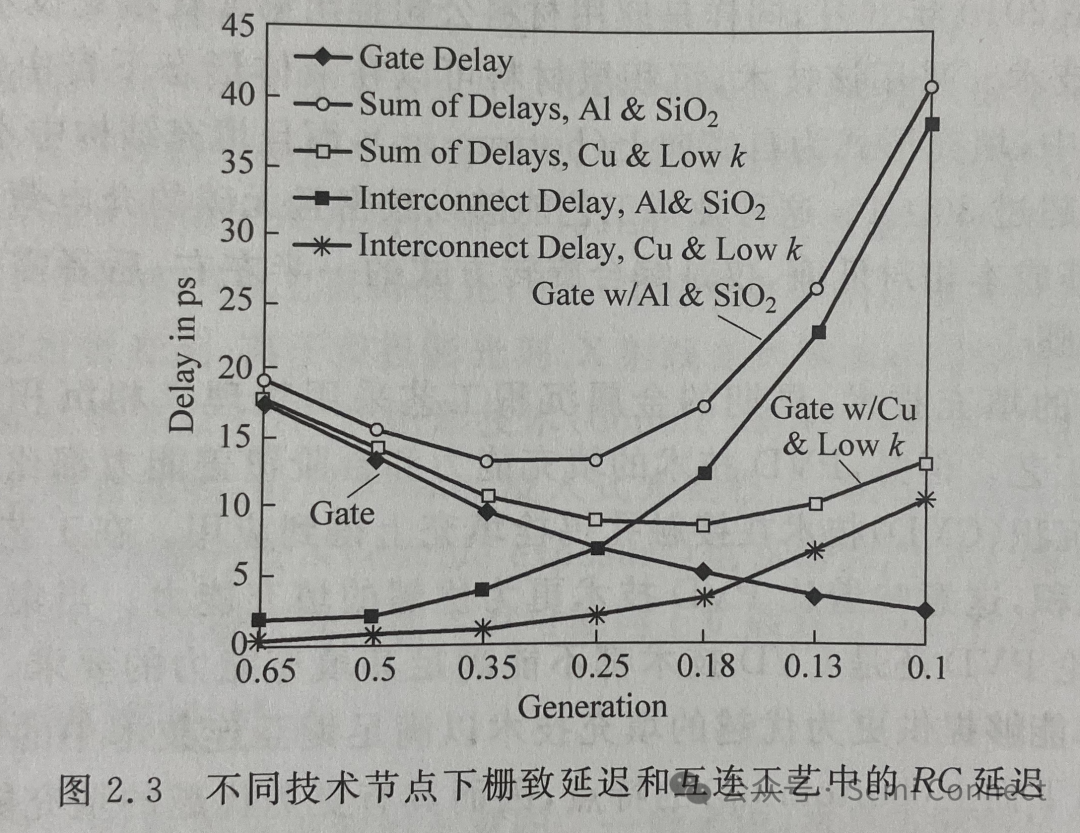

隨著集成電路技術節點的不斷減小以及互連布線密度的急劇增加,互連系統中電阻、電容帶來的 RC耦合寄生效應迅速增長,影響了器件的速度。圖2.3比較了不同技術節點下門信號延遲(gate delay)和互連層RC延遲(RC delay)。在早期,柵致延遲占主導地位,互連工藝中的RC延遲的影響很小。隨著 CMOS 技術的發展,柵致延遲逐步變小;但是,RC延遲卻變得更加嚴重。到 0.25μm 技術節點,RC延遲不再能夠被忽略。

降低 RC 延遲可以分別通過降低阻抗和容抗以達到目的。首先來考察與阻抗相關的相關參數

式中,p是導線材料的電阻率,A和L 分別是與電流方向垂直的導線截面積和電流方向的導線長度。由于A和L是幾何微縮過程中已經確定了的重要參數,降低阻抗R的最好的方法就是降低電阻率p值。在0.18μm 和0.13μm技術節點,工業界引入了低電阻值的銅互連線來代替鋁互連技術,銅互連將至少沿用到 22nm技術節點。

接著,來看容抗相關的物理參數

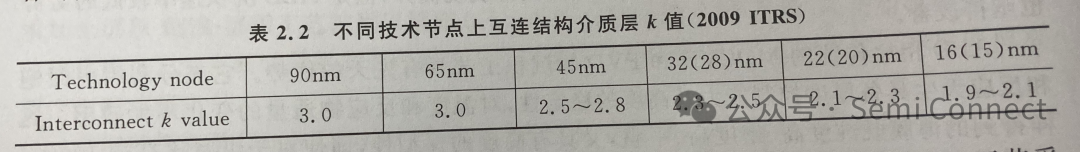

在上述等式中,k是介電材料的介電常數,A和d分別是導線之間的正對面積和導線之間的距離。同樣,由于A和L是幾何微縮過程中已經確定了的重要參數,工業界采用低電容的低介電常數(低k)絕緣材料,其發展趨勢就是介電常數不斷降低(見表2.2)。

二氧化硅的k值在4.2左右,通常通過摻雜其他元素以降低k值,比如 0.18

μm 工藝采用摻氟的二氧化硅,氟是具有強負電性的元素,當其摻雜到二氧化硅中后,可以降低材料中的電子與離子極化,從而使材料的介電常數從4.2 降低到3.6左右。

更進一步地,通過引入碳原子在介電材料也可以降低k值,即利用形成Si-C及C-C鍵所聯成的低極性網絡來降低材料的介電常數。針對降低材料密度的方法,其一是采用化學氣相沉積(CVD)的方法在生長二氧化硅的過程中引入甲基(一CH3),從而形成松散的SiOC:H薄膜,也稱CDO(碳摻雜的氧化硅),其介電常數在3.0左右。其二是采用旋壓方法(spin-on)將有機聚合物作為絕緣材料用于集成電路工藝。這種方法兼顧了形成低極性網絡和高空隙密度兩大特點,因而其介電常數可以降到2.6以下。但致命缺點是機械強度差,熱穩定性也有待提高。

當低k材料中的一部分原子被孔隙所替代時,很自然的,其k值繼續下降。通常來說,介電材料的孔隙率越高,k值越低。介電材料中增加的孔隙率對材料的熱-機械性能會帶來不利的影響。此外,隨著孔隙率的增加,材料的彈性模量和導熱系數的退化速度(冪指數規律)比其材料密度和 k值的降低速度要快,后兩者是以線性規律下降的。這種不利影響能被隨后的修復(cure)技術所補償,包括熱處理、紫外線照射和電子束照射等方法,去除致孔劑,并同時破壞低k膜材料中 Si-OH及Si-H鍵,形成Si-O鍵網絡,大角度的Si-O-Si鍵向更加穩定的小角或者“網絡”結構轉變,同時交聯程度也得到提高,從而能使機械強度得到提高。

到65nm 技術節點以下則采用低k 材料(k≤3.2),到超低介電常數材料(ULK,k≤2.5),乃至到空氣隙(air gap)架構(k≤2.0)。同傳統的氧化硅薄膜相比,低k薄膜在機械強度、熱穩定性和與其他工藝銜接等方面有很多問題,給工藝技術帶來了很大挑戰。

-

集成電路

+關注

關注

5416文章

11923瀏覽量

366823 -

CMOS

+關注

關注

58文章

5976瀏覽量

237950 -

工藝

+關注

關注

4文章

664瀏覽量

29220

原文標題:互連層 RC延遲的降低

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

[原創]PCB互連設計過程中最大程度降低RF效應的基本方法

[原創]PCB互連設計過程中最大程度降低RF效應的基本方法

降低RF效應的重要方法

降低PCB互連設計RF效應的技巧和方法

怎么降低延遲?

PCB互連設計過程中最大程度降低RF效應的基本方法

如何降低PCB互連設計RF效應?

互連線RC模型應用條件的仿真研究

集成電路互連延遲問題的研究及對策

降低PCB互連設計RF效應小技巧分享

互連層RC延遲的降低方法

互連層RC延遲的降低方法

評論