隨著新一代網絡被部署用來支持日益多樣化的高帶寬應用組合,網絡供應商和數據中心運營商需要快速擴展數據包處理能力,同時最大限度地降低資本支出/運營成本,并保持靈活性,從而適應未來的連接標準。為滿足未來的不同需求,賽靈思推出了Kintex UltraScale+ KU19P FPGA。

Xilinx KintexUltraScale+ KU19P FPGA

產品描述

Xilinx KintexUltraScale+ KU19P FPGA 是 Kintex UltraScale + FPGA 產品組合的最新成員。與其它中端器件相比,可提供更多的邏輯結構和嵌入式存儲器,并且還包含 PCIe Gen4 和其它高端功能。這款產品提供了高效加速網絡處理所需的優化資源組合和高吞吐量連接,同時延續了整個 Kintex FPGA 產品組合的固有特性,在性能、價格和功耗之間實現了最佳平衡。KU19P FPGA 可實現數據包處理和網絡加速,因此非常適合有線/無線通信、數據中心等快速發展的應用。

主要性能與優勢

優化的資源,用于數據包處理和網絡加速

PCIe Gen4 ,可實現低延遲和最大 I/O 帶寬

33Gb/s 收發器,支持高性能網絡系統

在 16nm FinFET 節點實現最佳每瓦價格/性能比

借助 KU19P FPGA 成功實現加速功能的眾多應用

PON接入:無源光網絡 (PON) 是網絡運營商部署的主要寬帶接入技術之一。依托可編程邏輯和硬件加速塊,KU19P FPGA 非常適合執行第 2 層至第 4 層數據包處理功能,其中包括分類、過濾、查找和數據包轉發。

移動回程:對更高數據容量的需求激增推進了無線電接入網 (RAN) 和移動回程技術的創新。傳統微波頻段支持 112MHz 的信號帶寬,這通常需要多個 FPGA 進行信號處理。通過在單個器件中實現更高吞吐量的數據包處理,KU19P FPGA 是開發點對點微波調制解調器的理想平臺。

數據中心網絡加速:傳統服務器節點的發展速度已經很難趕上網絡端口速度的增長水平。KU19P FPGA提供了高性能的數據包處理和數據路徑卸載、先進的 SerDes 技術以及 100G 以太網 IP,為實現快速的數據移動提供了無與倫比的可擴展性與連接性。

-

賽靈思

+關注

關注

33文章

1795瀏覽量

132116 -

Xilinx

+關注

關注

73文章

2182瀏覽量

124331 -

數據中心

+關注

關注

16文章

5135瀏覽量

73190

原文標題:性能、價格、功耗的“三體問題”新解:Xilinx KU19P

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

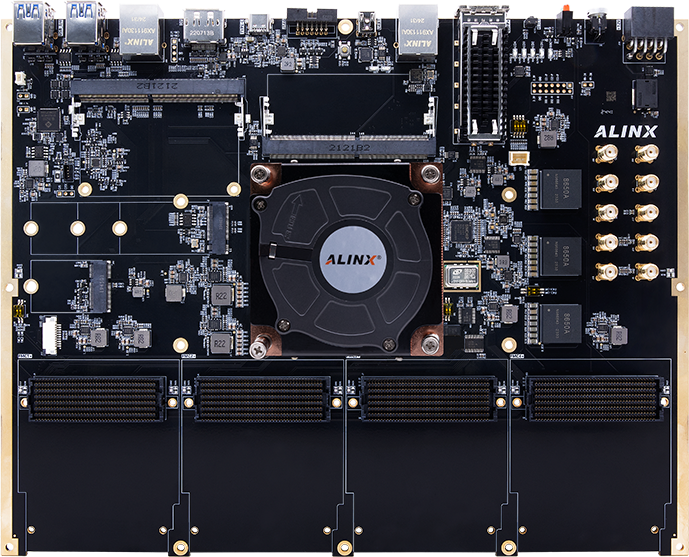

AI 應用場景全覆蓋!解碼超高端 VU+ FPGA 開發平臺 AXVU13F

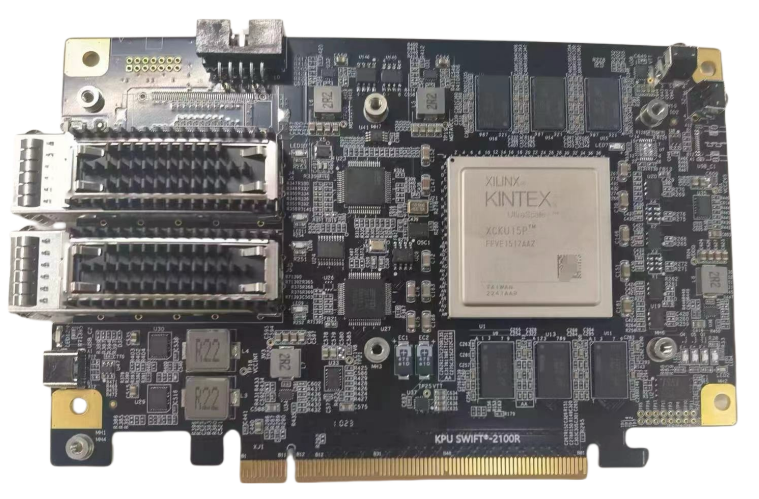

南京芯麒電子-基于KU15P的雙路100G光纖加速卡

賽靈思低溫失效的原因,有沒有別的方法或者一些見解?

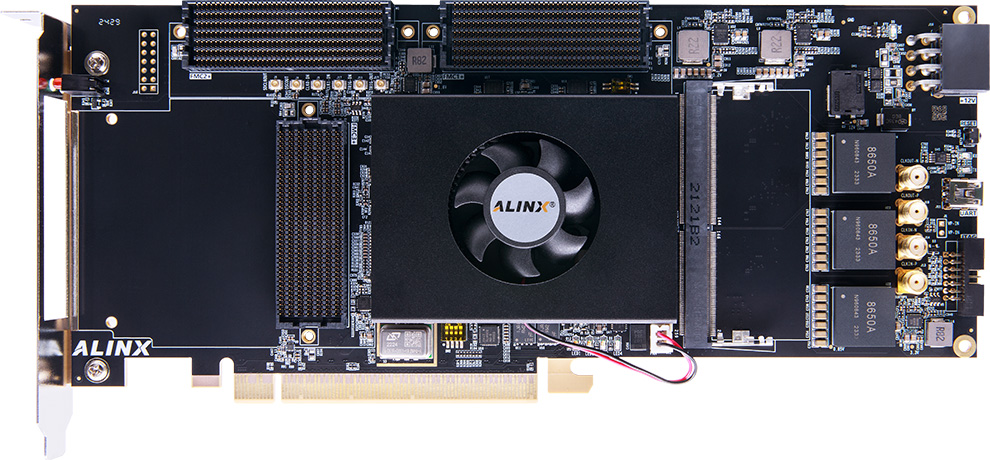

ALINX 發布 AXVU13P:AMD Virtex UltraScale+ 高端 FPGA PCle 3.0 綜合開發平臺

易靈思FPGA產品的主要特點

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 評估套件

AMD發布超小車規級FPGA,賦能ADAS與數字座艙

AMD 面向 ADAS 和數字座艙推出尺寸更小、成本優化的車規級 FPGA 系列

ALINX FPGA+GPU異架構視頻圖像處理開發平臺介紹

賽思快訊 | 發展新質生產力問道賽思?賽思如何下好“創新棋”?

賽靈思推出了Kintex UltraScale+ KU19P FPGA

賽靈思推出了Kintex UltraScale+ KU19P FPGA

評論