Verilog HDL簡稱Verilog,它是使用最廣泛的硬件描述語言。

誕生時間:1983年。

可以分為5個層次:(自頂向下)

第一層,系統級(system):用高級語言設計模塊的外部性能的模型

第二層,算法級(Algorithmic):用高級語言實現設計算法的模型

第三層,寄存器傳輸級(RTL):描述數據在寄存器之間的流動以及如何處理這些數據的模型。這是其他高級語言不具備的能力

第四層,門級(gate-level):描述邏輯門以及邏輯門之間的連接的模型

第五層,開關級(switch-level):描述器件中三極管和存儲節點以及它們之間連接的模型

注:前三層屬于行為級,第四層屬于邏輯級,第五層屬于開關級

Verilog的特點:

1. 它與C語言相似,語法靈活

2. 能夠抽象出電路行為和結構

3. 支持邏輯設計中層次與范圍的描述

4. 具有電路仿真和驗證機制

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

Verilog

+關注

關注

29文章

1366瀏覽量

111828

發布評論請先 登錄

相關推薦

熱點推薦

一文詳解Verilog HDL

Verilog HDL(Hardware Description Language)是一種硬件描述語言,用于從算法級、門級到開關級的多種抽象設計層次的數字系統建模。現實生活中多用于專用集成電路

淺談Verilog和VHDL的區別

Verilog和VHDL是兩種廣泛使用的硬件描述語言(HDL),它們用于描述和模擬數字電路系統的行為和結構。這兩種語言的主要作用是幫助工程師設計、仿真和驗證集成電路(IC)和系統級芯片(SoC)中的硬件模塊。

如何理解芯片設計中的IP

描述語言(如Verilog、VHDL)編寫的電路設計,也可以是完成的電路板或者甚至是一些特定算法和技術。IP的使用大大提高了芯片設計的效率,避免了從頭開始設計所有功能模塊。下面詳細解釋芯片IP的幾個關鍵點: 1. 芯片IP的定義與作用: 芯片IP類似于建筑中的標準化模塊或

Verilog 電路仿真常見問題 Verilog 在芯片設計中的應用

在現代電子設計自動化(EDA)領域,Verilog作為一種硬件描述語言,已經成為數字電路設計和驗證的標準工具。它允許設計師以高級抽象的方式定義電路的行為和結構,從而簡化了從概念到硅片的整個設計流程

Verilog 與 ASIC 設計的關系 Verilog 代碼優化技巧

Verilog與ASIC設計的關系 Verilog作為一種硬件描述語言(HDL),在ASIC設計中扮演著至關重要的角色。ASIC(Application Specific Integrated

Verilog 測試平臺設計方法 Verilog FPGA開發指南

Verilog測試平臺設計方法是Verilog FPGA開發中的重要環節,它用于驗證Verilog設計的正確性和性能。以下是一個詳細的Verilog測試平臺設計方法及

Verilog與VHDL的比較 Verilog HDL編程技巧

理解。 VHDL :VHDL 的語法更接近于 Ada 語言,它是一種更正式的語言,具有豐富的數據類型和結構。VHDL 支持數據流、行為和結構化三種描述方式。 2. 可讀性和可維護性 Veril

深入理解C語言:循環語句的應用與優化技巧

能讓你的代碼更加簡潔明了,還能顯著提升程序執行效率。本文將詳細介紹C語言中的三種常見循環結構——while循環、for循環和do...while循環,帶你深入理解它

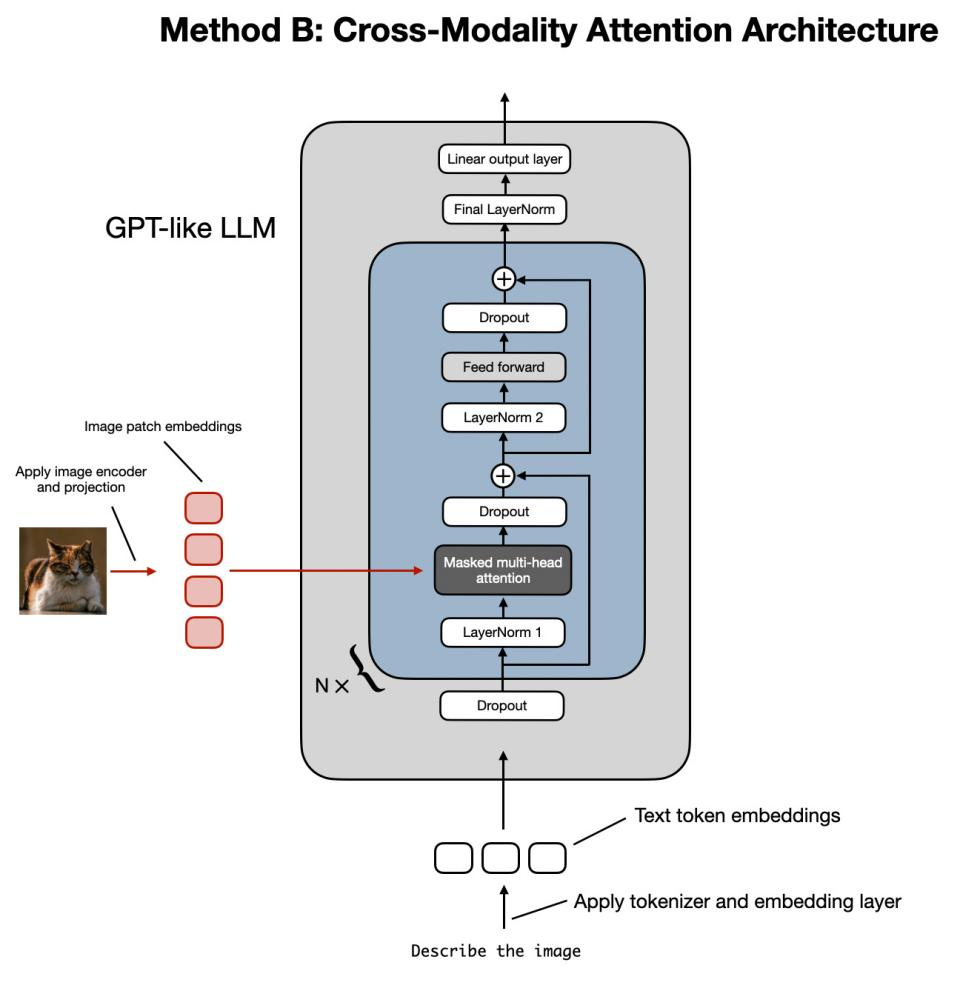

一文理解多模態大語言模型——下

/understanding-multimodal-llms ? 《一文理解多模態大語言模型 - 上》介紹了什么是多模態大語言模型,以及構建多模態 LLM 有兩種主要方式之一:統一嵌入解碼器架構(Unified Embeddin

Verilog vhdl fpga

相關專業,具有良好的專業基礎知識。 感興趣可滴滴 JYHXDX534

2.工作年限不限,有工作經驗或優秀應屆畢業生亦可。

3.對FPGA芯片架構和資源有深入的理解,精通Verilog HDL、VHDL

發表于 11-12 16:40

Verilog硬件描述語言參考手冊

一. 關于 IEEE 1364 標準二. Verilog簡介三. 語法總結四. 編寫Verilog HDL源代碼的標準五. 設計流程

發表于 11-04 10:12

?4次下載

FPGA編程語言的入門教程

FPGA(現場可編程邏輯門陣列)的編程涉及特定的硬件描述語言(HDL),其中Verilog和VHDL是最常用的兩種。以下是一個FPGA編程語言(以Verilog為例)的入門教程: 一、

FPGA芯片架構和資源有深入的理解,精通Verilog HDL、VHDL

、計算機相關專業,具有良好的專業基礎知識。

2.工作年限不限,有工作經驗或優秀應屆畢業生亦可。

3.對FPGA芯片架構和資源有深入的理解,精通Verilog HDL、VHDL編程語言,熟悉時序約束、時序分析

發表于 09-15 15:23

快速理解Verilog語言

快速理解Verilog語言

評論