1、概述

隨著FPGA容量的增大,FPGA的設計日益復雜,設計調試成為一個很繁重的任務。為了使得設計盡快投入市場,設計人員需要一種簡易有效的測試工具,以盡可能的縮短測試時間。傳統的邏輯分析儀在測試復雜的FPGA設計時,將會面臨以下幾點問題:1)缺少空余I/O引腳。設計中器件的選擇依據設計規模而定,通常所選器件的I/O引腳數目和設計的需求是恰好匹配的。2)I/O引腳難以引出。設計者為減小電路板的面積,大都采用細間距工藝技術,在不改變PCB板布線的情況下引出I/O引腳非常困難。3)外接邏輯分析儀有改變FPGA設計中信號原來狀態的可能,因此難以保證信號的正確性。4)傳統的邏輯分析儀價格昂貴,將會加重設計方的經濟負擔。

伴隨著EDA工具的快速發展,一種新的調試工具Quartus II 中的SignalTap II 滿足了FPGA開發中硬件調試的要求,它具有無干擾、便于升級、使用簡單、價格低廉等特點。本文將介紹SignalTap II邏輯分析儀的主要特點和使用流程,并以一個實例介紹該分析儀具體的操作方法和步驟。

2、 SignalTap II的特點及使用

SignalTap II嵌入邏輯分析儀集成到Quartus II設計軟件中,能夠捕獲和顯示可編程單芯片系統(SOPC)設計中實時信號的狀態,這樣開發者就可以在整個設計過程中以系統級的速度觀察硬件和軟件的交互作用。它支持多達1024個通道,采樣深度高達128Kb,每個分析儀均有10級觸發輸入/輸出,從而增加了采樣的精度。SignalTap II為設計者提供了業界領先的SOPC設計的實時可視性,能夠大大減少驗證過程中所花費的時間。目前SignalTap II邏輯分析儀支持的器件系列包括:APEXT II, APEX20KE, APEX20KC, APEX20K, Cyclone, Excalibur, Mercury, StraTIx GX, StraTIx。

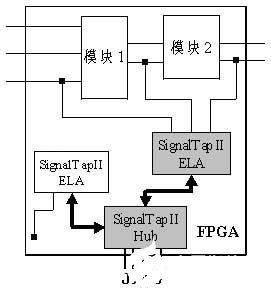

SignalTap II將邏輯分析模塊嵌入到FPGA中,如圖1所示。邏輯分析模塊對待測節點的數據進行捕獲,數據通過JTAG接口從FPGA傳送到Quartus II軟件中顯示。使用SignalTap II無需額外的邏輯分析設備,只需將一根JTAG接口的下載電纜連接到要調試的FPGA器件。SignalTap II對FPGA的引腳和內部的連線信號進行捕獲后,將數據存儲在一定的RAM塊中。因此,需要用于捕獲的采樣時鐘信號和保存被測信號的一定點數的RAM塊。

使用SignalTap II的一般流程是:設計人員在完成設計并編譯工程后,建立SignalTap II (.stp)文件并加入工程、配置STP文件、編譯并下載設計到FPGA、在Quartus II軟件中顯示被測信號的波形、在測試完畢后將該邏輯分析儀從項目中刪除。以下描述設置 SignalTap II 文件的基本流程:

1.設置采樣時鐘。采樣時鐘決定了顯示信號波形的分辨率,它的頻率要大于被測信號的最高頻率,否則無法正確反映被測信號波形的變化。SignalTap II在時鐘上升沿將被測信號存儲到緩存。

2.設置被測信號。可以使用Node Finder 中的 SignalTap II 濾波器查找所有預綜合和布局布線后的SignalTap II 節點,添加要觀察的信號。邏輯分析器不可測試的信號包括:邏輯單元的進位信號、PLL的時鐘輸出、JTAG引腳信號、LVDS(低壓差分)信號。

3.配置采樣深度、確定RAM的大小。SignalTap II所能顯示的被測信號波形的時間長度為Tx,計算公式如下:

Tx=N×Ts

N為緩存中存儲的采樣點數,Ts為采樣時鐘的周期。

4.設置buffer acquisiTIon mode。buffer acquisiTIon mode包括循環采樣存儲、連續存儲兩種模式。循環采樣存儲也就是分段存儲,將整個緩存分成多個片段(segment),每當觸發條件滿足時就捕獲一段數據。該功能可以去掉無關的數據,使采樣緩存的使用更加靈活。

5.觸發級別。SignalTap II支持多觸發級的觸發方式,最多可支持10級觸發。

6.觸發條件。可以設定復雜的觸發條件用來捕獲相應的數據,以協助調試設計。當觸發條件滿足時,在signalTap時鐘的上升沿采樣被測信號。

完成STP設置后,將STP文件同原有的設計下載到FPGA中,在Quartus II中SignalTap II窗口下查看邏輯分析儀捕獲結果。SignalTap II可將數據通過多余的I/O引腳輸出,以供外設的邏輯分析器使用;或輸出為csv、tbl、vcd、vwf文件格式以供第三方仿真工具使用。

3 、實例分析

本文以一個ADC0809器件的采樣控制器作為實例,具體說明如何用SignalTap II 來進行FPGA設計的驗證。使用Altera公司的器件Cyclone系列FPGA- EP1C12Q240C8,該器件支持SignalTap II 嵌入式邏輯分析儀的使用。

FPGA的設計結構如圖2所示。數字倍頻器的倍頻輸出提供ADC控制器的采樣觸發脈沖。A/D轉換器ADC0809的操作時序見數據手冊,根據其操作時序,ADC控制器來實現ADC0809的數據采集操作,采樣的時機由倍頻器來控制。控制器每控制完成一次采樣操作,則停止等待下一個觸發脈沖的到來。倍頻器每輸出一個低電平脈沖,ADC采樣控制器的狀態機進行一次采樣操作。在倍頻器的觸發控制下,完成被測信號一個基波周期N個點的等間隔采樣,同時數字倍頻器跟蹤輸入信號的頻率的變化,盡可能地保持N個點的采樣寬度正好為被測信號一個周波的寬度。

測試項目是基于FPGA的AD采樣控制器,它是用狀態機控制的周期性的重復事件,一次采樣操作完成后等待采樣脈沖、開始下一次的采樣。針對待測項目的周期性,

在STP文件中將buffer acquisition mode分別設為連續存儲和循環采樣存儲兩種模式進行驗證。連續存儲方式記錄采樣操作的連續過程,而在循環采樣存儲方式下SignalTap II記錄多次采樣時刻數據。

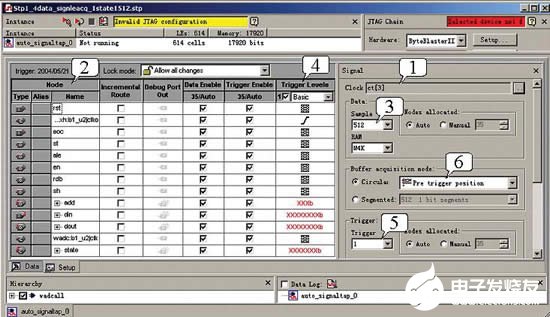

按照上述SignalTap II的使用步驟,在編譯后的工程中添加STP文件,并對文件進行設置,如圖3所示。如1處設置采樣時鐘ct[3],系統時鐘的16分頻。2處添加測試信號,包括待測模塊輸出的AD采樣控制信號和狀態機的狀態等。3處是采樣深度的設置,設為512。在4處的設置確定了在clko時鐘的上升沿觸發邏輯分析儀。在連續存儲模式下設置buffer acquisition mode為Circular前觸發位置。在分段存儲模式下設置為Sigmented 512 1 bit segments,表示將存儲區劃分成512個段,每段1個位的存儲深度。存儲模式的設置如圖中6所示。另外,使用Mnemonic Table將狀態機的7個狀態標示為直觀名稱。

首先將STP文件設置成連續存儲模式,并將該文件連同工程一起下載到FPGA中。在連續存儲模式下,SignalTap II在clko時鐘的上升沿連續采樣直到采樣點數達到512個。這樣,SignalTap II記錄了一次采樣過程的所有數據,捕獲結果如圖4所示,從中可以看到FPGA控制ADC0809轉換的時序波形。

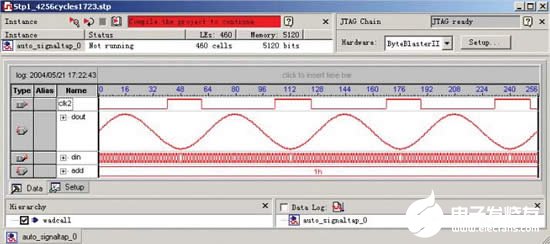

將圖3所示步驟6中的Buffer acquisition node改為Segmented方式,設其值為256 1 bit segments,并將修改后的STP文件連同工程重新下載到FPGA中。和單次觸發相同的是邏輯分析儀在ADC0809采樣時鐘上升沿時觸發邏輯分析儀,不同的是因為每一段只有1bit的存儲深度,因此捕獲1位數據后邏輯分析儀停止,等待下一次滿足觸發信號再次啟動,一共啟動256次。在波形顯示窗口,設顯示格式為Line Chart,這樣結果就直觀的顯示為連續的波形。分片采樣,可觀察同步采樣的結果,圖5是連續采樣256個點的結果波形。

4 、結論

SignalTap II 嵌入式邏輯分析器,提供了芯片測試的一個很好的途徑。通過SignalTap II 測試芯片無需外接專用儀器,它在器件內部捕獲節點進行分析和判斷系統故障。本文通過對Cyclone EP1C12器件的實驗證實該測試手段大大提高系統的調試能力,具有很好的效果。

責任編輯:gt

-

FPGA

+關注

關注

1645文章

22049瀏覽量

618346 -

芯片

+關注

關注

459文章

52504瀏覽量

440744 -

eda

+關注

關注

71文章

2925瀏覽量

177935

發布評論請先 登錄

usb微型實時頻譜分析儀功能特點

頻譜分析儀與信號分析儀的區別

4457示波器-H01邏輯分析儀選件

淺談邏輯分析儀的技術原理和應用領域

Keysight 頻譜分析儀(信號分析儀)

SignalTap II的特點、設置流程及邏輯分析儀的設計

SignalTap II的特點、設置流程及邏輯分析儀的設計

評論