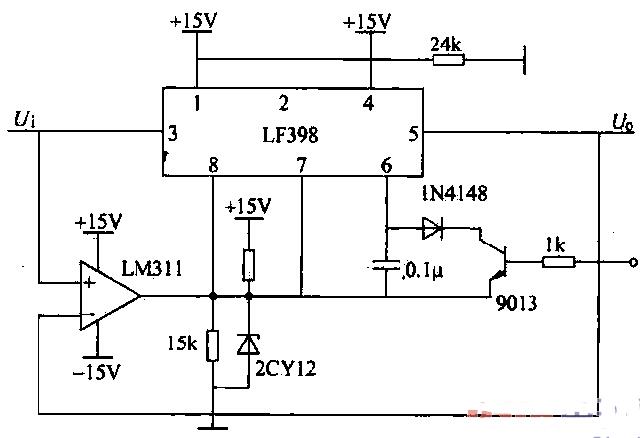

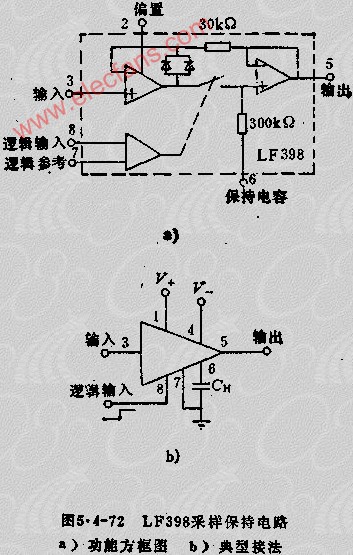

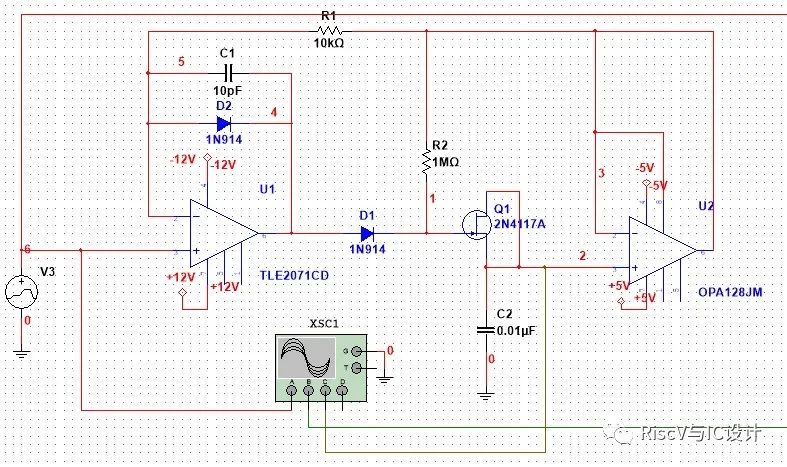

峰值電壓采樣保持電路:峰值電壓采樣保持電路如圖12-50所示。峰值電壓采樣保持電路南一片采樣保持器芯片LF398和一塊電壓比較器LM311構(gòu)成。LF398的輸出電壓和輸入電壓通過LM3J1進行比較t當U.》Uo時.LM311輸出高電平,送到LF398的邏輯控制端8腳,使LF398處于采樣狀態(tài)}當Ul達到峰值而下降時,U,《U。,電壓比較器LM311輸出低電平,LF398的:邏輯控制端置低電平,使LF398處于保持狀態(tài)。由于LM311采用集電極開路輸出,故需接上拉電阻.由過電壓檢測電路輸出端送來的脈沖控制電路開關(guān)的導(dǎo)通,沒有過電時采樣電容放電,否則采樣電路一直跟蹤峰值的變化。

-

電壓

+關(guān)注

關(guān)注

45文章

5708瀏覽量

117894 -

LF398

+關(guān)注

關(guān)注

1文章

7瀏覽量

19357 -

LM311

+關(guān)注

關(guān)注

5文章

22瀏覽量

36726

發(fā)布評論請先 登錄

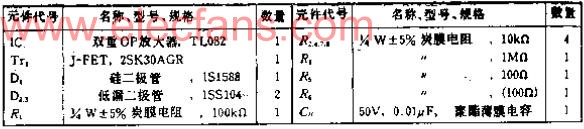

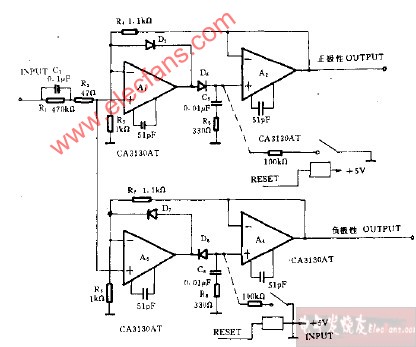

峰值保持電路設(shè)計

高速脈沖峰值保持電路的設(shè)計

峰值電壓采樣保持電路

峰值電壓采樣保持電路

評論