什么是反射噪音?它對定制PCB的功能有什么影響?如何通過更好的設(shè)計實踐來緩解它?

這篇文章是受到“信號完整性院長”啟發(fā)的系列文章之一,Eric Bogatin博士在Altium Live 2018上的主題演講。

該系列的其他文章包括:

什么是電感以及它如何應(yīng)用于接地反彈?

如何減少接地反彈:使用PCB設(shè)計降低噪聲最佳實踐。

最小阻抗路徑:如何使用返回路徑實現(xiàn)更好的PCB設(shè)計

本文重點(diǎn)介紹反射噪聲以及如何通過智能布局減少噪聲選擇。

什么是反射噪聲?

每當(dāng)我們從PCB上的一個數(shù)字集成電路向另一個數(shù)字集成電路發(fā)送信號時,我們就會改變狀態(tài)。信號線。狀態(tài)的變化以及電磁場中伴隨的變化可以描述為當(dāng)波在電路中移動時的波。波浪是將能量從一個位置傳遞到另一個位置的現(xiàn)象,導(dǎo)體引導(dǎo)傳播路徑。

當(dāng)電線的電位發(fā)生變化時,這是對電線周圍磁能的一種藝術(shù)印象。

當(dāng)反射噪聲產(chǎn)生時電磁波遇到從一個介質(zhì)到下一個介質(zhì)的邊界。當(dāng)波遇到邊界時,部分能量作為信號傳播,部分能量被反射。

這個動畫說明,當(dāng)波浪從一種介質(zhì)傳播到另一種介質(zhì)時,并非所有能量都被傳輸 - 一部分能量被反射回其源頭。

對于電氣工程師來說,發(fā)生這種邊界的介質(zhì)通常用其電阻來描述;也就是說,邊界是阻抗變化的地方。

阻抗由電阻和電抗元件組成。電阻器將電路的能量作為熱量耗散。電路中的可恢復(fù)能量存在于滲透并圍繞導(dǎo)體,電感器和電容器的電磁場中。

每當(dāng)電路中的阻抗發(fā)生變化時,一定量的反射將會發(fā)生。反射波將返回下一個邊界(阻抗發(fā)生變化的位置)并再次反射。

此1D波形圖顯示了兩點(diǎn)之間反射的波脈沖。能量隨時間/距離衰減。

該過程將無限期地持續(xù),直到能量被電路吸收或消散到環(huán)境中。

為什么反射噪聲成問題?

對于信號線,驅(qū)動器和接收器上會有反射點(diǎn)。工程師的工作是盡量減少反射信號的數(shù)量,并通過阻抗匹配最大化傳輸信號的數(shù)量。

如果不可能,額外的能量需要在積累和淹沒之前消散。輸出帶有噪聲的信號。

如果反射脈沖的能量在下一個脈沖產(chǎn)生之前沒有消散,那么能量將累積并增加一種稱為疊加的現(xiàn)象。幸運(yùn)的是,信號在通過電阻元件時會衰減。所以一個簡單的串聯(lián)電阻將消除大多數(shù)振鈴。

評估數(shù)字信號中的噪聲

傅里葉定理教導(dǎo)任何波或波脈沖都可以分解成一系列正弦和/或余弦波。如果你想更深入地了解這個概念,我推薦這個視頻在伊利諾伊大學(xué)的Bill Hammack的諧波分析儀上。

如果你有一個足夠小的上升/下降時間,一個脈沖可以保持?jǐn)?shù)十個小振幅波。

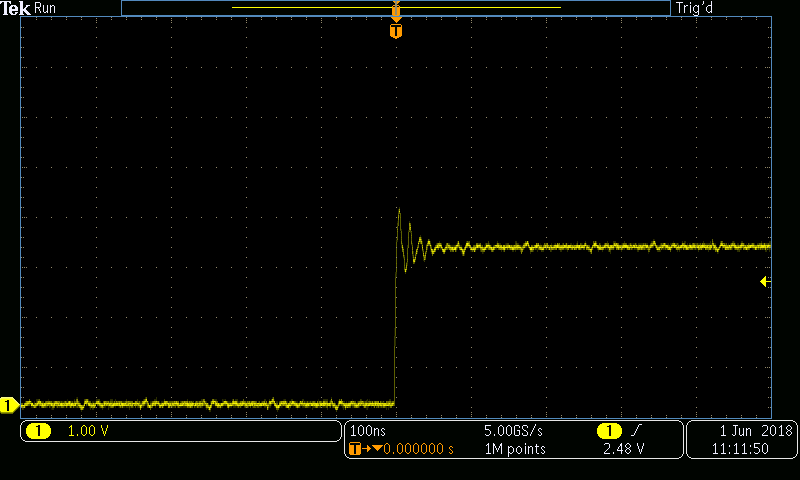

在下圖中,您可以看到無阻尼數(shù)字信號切換邏輯狀態(tài)從低到高。

在TI Lightcrafter上捕獲的無阻尼數(shù)字信號(黃色,通道1),因為它將邏輯狀態(tài)從低切換為現(xiàn)在看看下面的圖像,其中左圖顯示了復(fù)合波脈沖通過逐漸疊加的減小幅度的奇次諧波而產(chǎn)生的復(fù)合波脈沖,現(xiàn)在看看下面的圖像。原始波。對于實際感興趣的信號,我們可以將波形分解為一系列正弦波。

如上圖所示,真正的數(shù)字信號具有較大的帶寬,并且該能量的任何部分都可能在電路中產(chǎn)生共振。這與具有非常窄的帶寬且易于計算共振的RF信號形成對比。

如果你設(shè)法產(chǎn)生駐波,你將產(chǎn)生巨大的噪聲源,可以壓倒附近的任何信號線

這個gif表明在特定波長反射的波(橙色)可以與其反射相結(jié)合(藍(lán)色)創(chuàng)建一個高振幅駐波(綠色)。這種現(xiàn)象將發(fā)生在1/2波長的奇整數(shù)倍處,其中波長是跡線長度的兩倍。

如何降低反射噪聲

您可以使用幾種方法來管理設(shè)計中的反射噪聲。以下是您可以使用的一些技術(shù)的概述。

保持恒定阻抗

您應(yīng)該考慮的第一件事是如何保持跟蹤的恒定阻抗只要有可能。請記住:當(dāng)阻抗發(fā)生變化時會發(fā)生反射。

計算跡線的阻抗

為了保持恒定的阻抗,你要'我需要能夠計算出跡線的阻抗。您的PCB程序應(yīng)該允許您這樣做,但也有在線工具可供使用。

一旦確定了跟蹤和空間寬度,請沿著路線維護(hù)它們。

跡線的一致性

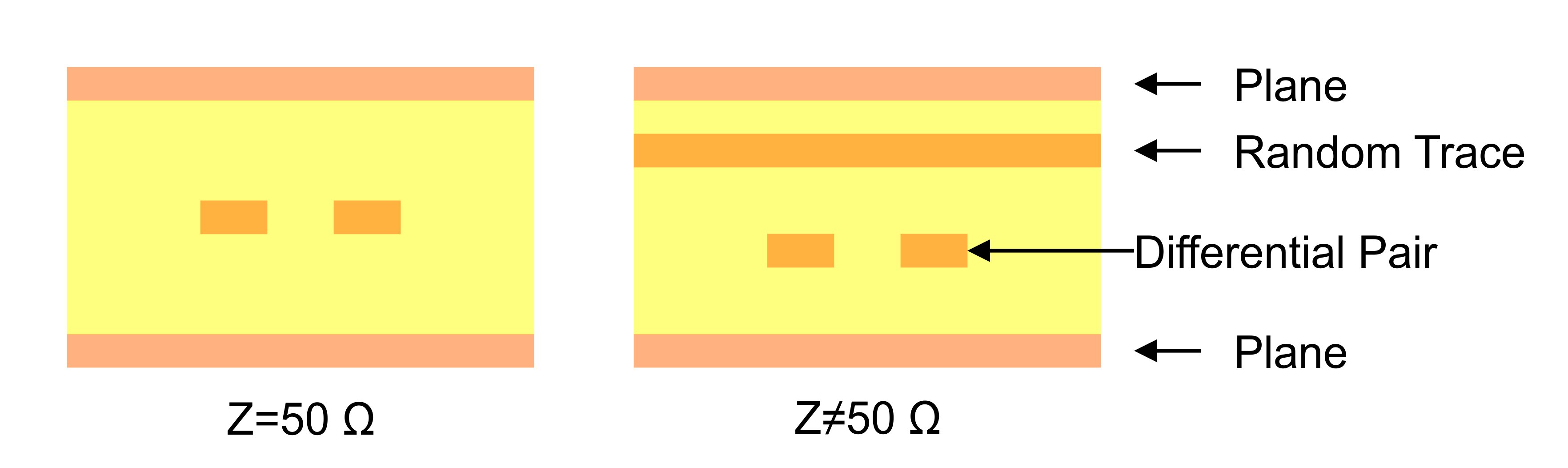

要保持差分對或單端跡線的恒定阻抗,必須保持恒定的跡線寬度,恒定間距和常數(shù)與所有其他導(dǎo)體分離。如果使用隨機(jī)軌跡在阻抗控制對上進(jìn)行路由,則會改變阻抗并創(chuàng)建反射點(diǎn)。

使用阻抗變化的阻抗匹配電路

當(dāng)你必須改變時阻抗(例如從線性放大器到天線),使用阻抗匹配電路(使用史密斯圖表,在線工具等計算......)。

減少反射點(diǎn)

您還可以考慮如何首先減少反射點(diǎn)的出現(xiàn)。

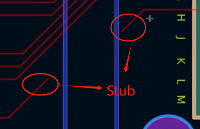

在電路板邊緣觀察過孔

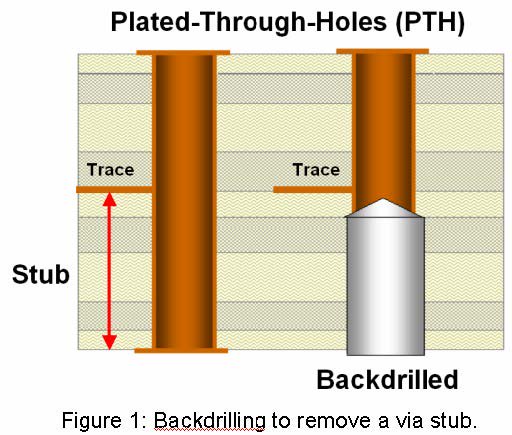

對于高速電路設(shè)計人員來說,Vias可能是個問題。如果通孔超出信號走線延伸到未使用的層,則電路的阻抗會突然改變。在電路板邊緣的過渡處,存在阻抗不匹配,因為跡線離開通孔(~50-150歐姆)并進(jìn)入空氣(~377歐姆)。這會在該位置產(chǎn)生反射點(diǎn),嚴(yán)重降低信號。

反鉆您的過濾器

解決方案是讓您的PCB制造商“反鉆”您的過孔在未使用的外層上從板上移除通孔。反鉆通過顯著改善邏輯轉(zhuǎn)換。

來自Sanmina-SCI的反鉆過孔

緩解現(xiàn)有反射噪聲

使用阻尼電阻

另一項重要技術(shù)是在所有驅(qū)動信號源附近串聯(lián)使用阻尼電阻,并具有快速上升/下降時間。這有時被稱為緩沖電阻。

任何發(fā)生的信號反射都將每次通過電阻器都會快速衰減。這些通常是靠近驅(qū)動信號源(例如,時鐘源,GPIO等)放置的<100Ω電阻。

一般的想法是創(chuàng)建一個阻尼電路 - 信號上升到適當(dāng)?shù)倪壿嬰娖揭淮危瑳]有過多的過沖和振鈴。

摘要

對于高速信號線,保持恒定阻抗對于設(shè)計工作電路至關(guān)重要。將信號從一個IC移動到另一個IC時,請使用阻尼電阻以防止振鈴。

如果您有其他意見或問題,請在下面分享!

-

pcb

+關(guān)注

關(guān)注

4356文章

23438瀏覽量

407153 -

華強(qiáng)pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

43767

發(fā)布評論請先 登錄

原理圖和PCB設(shè)計中的常見錯誤

DDR模塊的PCB設(shè)計要點(diǎn)

PCB設(shè)計中容易遇到的問題

SMT貼片前必知!PCB設(shè)計審查全攻

PCB設(shè)計中的Stub天線對信號傳輸?shù)挠绊?/a>

PCB設(shè)計中的Stub對信號傳輸?shù)挠绊?/a>

怎樣在PCB設(shè)計中消除反射噪聲

怎樣在PCB設(shè)計中消除反射噪聲

評論