無矢量測(cè)試:高速I/O的最佳選擇

大批量制造商必須解決如何經(jīng)濟(jì)高效地測(cè)試多個(gè)多線高速I的難題/O接口 - 例如PCI Express,HyperTransport和Infiniband - 嵌入到巨大的數(shù)字系統(tǒng)級(jí)芯片設(shè)計(jì)中。雖然片上內(nèi)置自測(cè)(BIST)與環(huán)回操作相結(jié)合是昂貴的自動(dòng)測(cè)試設(shè)備(ATE)的廣泛采用的替代方案,但其高速模擬部分的故障覆蓋率較差,嚴(yán)重影響整體產(chǎn)品現(xiàn)在,一種稱為無矢量測(cè)試的方法正在出現(xiàn),它提供了兩種方法中的最佳方法:片上I/O BIST的成本效益與基于ATE的信號(hào)完整性測(cè)量相結(jié)合。具體而言,該概念將ATE參數(shù)測(cè)試與片上測(cè)試內(nèi)容生成和比較結(jié)合在一起,形成了硅與ATE之間的協(xié)同作用。結(jié)果是使用成熟的電子設(shè)計(jì)自動(dòng)化技術(shù)為硅設(shè)計(jì)的大批量制造測(cè)試的經(jīng)濟(jì)優(yōu)化解決方案。

傳統(tǒng)的ATE架構(gòu)使ATE提供源向量和速度矢量處理任務(wù)模式測(cè)試。隨著頻率持續(xù)增加超過千兆位/秒的閾值,特別是對(duì)于高速I/O接口,在大批量制造環(huán)境中,在ATE上提供此功能的成本變得非常具有挑戰(zhàn)性。

為了最大限度地減少對(duì)ATE測(cè)試的依賴,許多設(shè)備制造商正在使用片上BIST結(jié)構(gòu)和環(huán)回模式的組合。由于當(dāng)今硅工藝中可能的高集成度,IC上硅面積的額外成本是非常合理的。

不幸的是,BIST方法因無法執(zhí)行任務(wù)模式參數(shù)測(cè)試而受到影響,隨著高速I/O接口的集成,這一點(diǎn)變得越來越重要。頻率在每秒千兆位的范圍內(nèi),信號(hào)不再被視為純數(shù)字信號(hào)。需要考慮信號(hào)完整性問題,例如時(shí)序抖動(dòng)和電平噪聲,以保持足夠的故障覆蓋率并滿足所需的質(zhì)量水平。

兩種方法中的最佳方法

進(jìn)入無矢量測(cè)試,這是一種更加協(xié)同的方法,可以充分利用ATE和BIST的優(yōu)勢(shì)。有了它,ATE有效地作為BIST/loopback中循環(huán)的擴(kuò)展。因此,測(cè)試儀不提供任務(wù)模式向量和速度比較;相反,它完全負(fù)責(zé)信號(hào)完整性驗(yàn)證。

由于矢量生成和速度比較功能傳統(tǒng)上增加了ATE信道的成本,這種雙重方法允許更經(jīng)濟(jì)的解決方案大批量制造。

以下是它的工作原理。片上BIST電路以所需的數(shù)據(jù)速率提供測(cè)試內(nèi)容,然后可以在環(huán)回模式下根據(jù)標(biāo)準(zhǔn)協(xié)議進(jìn)行測(cè)試。 ATE將通過執(zhí)行無法通過片上電路實(shí)現(xiàn)的信號(hào)完整性測(cè)量來做出貢獻(xiàn)。

參數(shù)測(cè)量的設(shè)置不需要矢量,因此全稱:無矢量參數(shù)測(cè)試。測(cè)試的參數(shù)取決于應(yīng)用,范圍從簡(jiǎn)單的抖動(dòng)生成,容差和接收器靈敏度到更復(fù)雜的參數(shù),如數(shù)據(jù)到時(shí)鐘的偏斜。

這對(duì)設(shè)計(jì)人員有何影響?設(shè)計(jì)人員現(xiàn)在負(fù)責(zé)在IC上創(chuàng)建機(jī)制,以便為設(shè)備的功能驗(yàn)證以及要在ATE上執(zhí)行的參數(shù)測(cè)試提供測(cè)試內(nèi)容。設(shè)計(jì)人員必須通過針對(duì)鎖相環(huán)的最大應(yīng)力調(diào)整的殺手模式生成最壞情況的信號(hào)完整性條件。這種方法的一個(gè)明顯優(yōu)勢(shì)是,設(shè)計(jì)人員可以利用與設(shè)計(jì)SoC相同的技術(shù)來測(cè)試這些電路,而不是等待開發(fā)更新的ATE技術(shù)。

環(huán)回信道

在ATE側(cè),環(huán)回路徑通過ATE中更具成本效益的環(huán)回信道卡進(jìn)行擴(kuò)展,允許模式獨(dú)立測(cè)量所需的信號(hào)完整性參數(shù),并可選擇允許訪問直流測(cè)量資源。該環(huán)回通道卡可以配置為測(cè)量信號(hào)完整性參數(shù),例如抖動(dòng),還允許測(cè)試工程師調(diào)整參數(shù)以便反饋給接收器。這允許使用相同的卡測(cè)試發(fā)射機(jī)信號(hào)完整性和接收機(jī)容差。

對(duì)于成本最敏感的應(yīng)用,可以提供通過/失敗測(cè)量,進(jìn)一步降低成本ATE卡。

有多種方法可以實(shí)現(xiàn)低成本的參數(shù)環(huán)回測(cè)試解決方案。一些解決方案使用抖動(dòng)注入模塊作為被測(cè)設(shè)計(jì)(DUT)板的附件,但這些方法可能會(huì)受到注入的抖動(dòng)隨數(shù)據(jù)速率變化的影響。

更多靈活的方法涉及一個(gè)可調(diào)數(shù)據(jù)眼圖調(diào)節(jié)器,它允許獨(dú)立的抖動(dòng)和電平調(diào)整(見圖,第62頁)。

因?yàn)镈UT板上的無源元件無法做到這一點(diǎn),ATE中的專用環(huán)回卡是一種合適的替代方案。這允許用戶使用ATE軟件對(duì)數(shù)據(jù)眼圖開放進(jìn)行編程。

將片上BIST與ATE輔助環(huán)回相結(jié)合的協(xié)同方法可以更有效地解決高速I/O問題。接口測(cè)試問題要比單獨(dú)提供。雖然它確實(shí)需要設(shè)計(jì)人員開發(fā)支持參數(shù)和邏輯測(cè)試的機(jī)制,但現(xiàn)有的EDA功能可以輕松支持這些機(jī)制的創(chuàng)建。

BIST和ATE的結(jié)合可實(shí)現(xiàn)經(jīng)濟(jì)高效的大批量生產(chǎn)新的SoC器件所需的模擬測(cè)量保持高故障覆蓋率和質(zhì)量水平的解決方案。

審核編輯 黃宇

-

測(cè)試

+關(guān)注

關(guān)注

8文章

5626瀏覽量

128290 -

矢量

+關(guān)注

關(guān)注

0文章

97瀏覽量

24017 -

ATE

+關(guān)注

關(guān)注

5文章

151瀏覽量

27106

發(fā)布評(píng)論請(qǐng)先 登錄

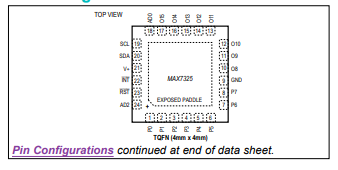

MAX7325 I2C端口擴(kuò)展器,提供8路推挽式I/O和8個(gè)漏極開路I/O技術(shù)手冊(cè)

光纖VS 同軸互連:如何選擇正確的高速測(cè)試方案?

怎樣使用無線 I/O 網(wǎng)關(guān)搭建物聯(lián)網(wǎng)系統(tǒng)

I/O接口與I/O端口的區(qū)別

為什么BLDC電機(jī)驅(qū)動(dòng)方案是高速鼓風(fēng)機(jī)的最佳選擇?

物聯(lián)網(wǎng)中常見的I/O擴(kuò)展電路設(shè)計(jì)方案_IIC I/O擴(kuò)展芯片

保護(hù)I/O模塊免受浪涌事件的影響

I/O模塊的主要作用有哪些

區(qū)域架構(gòu)和 MCU I/O 擴(kuò)展

無矢量測(cè)試:高速I/O的最佳選擇

無矢量測(cè)試:高速I/O的最佳選擇

評(píng)論