管理高速PCB中的損耗

到目前為止,大多數數字系統工程師都知道,當信號達到足夠高的頻率時,他們需要擔心PCB走線和其他導線的損耗。信號。在20世紀90年代大多數設計中典型的較低頻率(高達約200 MHz),損失是無關緊要的,或者是很少需要很少注意的微小影響。其他信號完整性問題,如反射,總延遲和串擾,則更為重要。分析工具可以通過假設“無損”傳輸線給出準確的答案,這些傳輸線可以快速模擬并且易于表征。

但是隨著設計頻率增加到300-400 MHz范圍,特別是引入了超高速千兆位-per-secondserial信號,丟失突然變得不可忽視。接收器IC上的示波器波形顯示出嚴重的信號衰減,振幅顯著衰減,邊緣明顯變圓和延遲。模擬器被迫通過添加有損傳輸線算法來響應。

盡管如此,許多設計師仍然不確定何時損失非常重要,原因是什么,如何衡量,以及如何最大限度地減少損失。本文將探討所有這些問題。

信號丟失的根源

首先,“損失”究竟是什么意思?

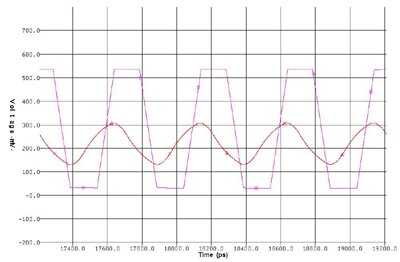

圖1使答案非常圖形化。它顯示了一個時鐘信號驅動36英寸帶狀線PCB走線,埋在典型的FR-4介電材料中。注意信號在遠端(紅色波形)看起來與在跟蹤的驅動端(紫色)有多么截然不同?它的振幅嚴重衰減,其上升/下降時間嚴重延長。實際上,當信號通過跡線時,信號看起來幾乎像正弦波。

為什么信號在跟蹤端看起來很差?顯然,它在傳播時失去了很多能量;單獨的幅度減小表明了這一點。但請注意,其高頻成分似乎特別受到重創。輸入信號的尖銳邊緣(由高頻內容產生)幾乎完全消失在輸出中。但為什么呢?

圖1 ??在典型的FR-4電介質中,TDR信號驅動36英寸帶狀線PCB跡線。注意當驅動器信號(紫色)到達跡線的遠端(紅色)時嚴重的幅度和邊沿時間退化。

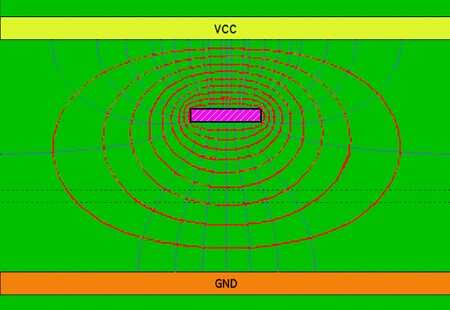

我們的信號經歷的一些損失是由于導體中的能量進食機制,以及電介質中的另一種效應。導體的罪魁禍首就是阻力;在FR-4中,責任落在“介電損耗”上,它直接從信號場中竊取能量。介電材料中的電場分布如圖2所示。

圖2 - 圖1 PCB的橫截面圖,顯示了信號傳輸時導體,兩個平面,電介質和電磁場線指揮。電場線為藍色;紅色磁性。

任何電氣設計人員都希望PCB走線具有一定的電阻。可能令人驚訝的是,高頻電阻遠大于直流電阻。原因是“趨膚效應”,即高頻電流聚集到導體邊緣的趨勢,而不是流過整個可用的橫截面。高頻信號看到的電阻遠大于預期的電阻,并且它與頻率的平方根成比例地增加。

介電損耗與所有電介質都含有極化分子的事實有關在EM場的存在下移動。高頻場非常快速地振蕩,當極性分子與場同步移動時,它們開始加熱介電材料。熱量只有一個可能的來源 - 信號本身的能量。事實證明,介電損耗隨著頻率的增加而無情地增加,并且與信號頻率成正比。

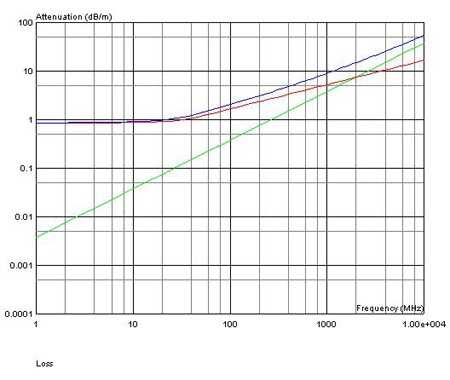

在前面的段落中埋藏是一個不祥的事實。皮膚電阻隨頻率的平方根而變化,但介電損耗直接縮放 - 這意味著在足夠高的頻率下,介電損耗的衰減應該超過皮膚損耗的衰減。

圖3說明了這正是發生的事情。該圖顯示,對于我們一直在討論的同一導體,電阻損耗(紅色)和介電損耗(綠色)。注意介電損耗如何在高頻下超過電阻損耗。這意味著對于超高速信號傳輸,總衰減越來越多地由所使用的介電材料決定。

圖3 - 對于圖1的導體,電阻(紅色)和介電損耗(綠色)與頻率(對數刻度)的關系圖。請注意,在低頻時,電阻損耗占主導地位,但在高頻時,介電損耗會超過電阻。

這就是舊的FR-4成為一個大問題的地方。 FR-4基本上是一種低成本,歷史悠久,混合玻璃纖維和膠水的混合物;除了其損耗特性和嚴格的過程控制外,所選擇的材料。然而(主要是出于成本原因),數字設計師仍在頑固地試圖通過它推動高頻信號。如前面的數字所示,隨著數據率越來越高,這將變得非常困難 - 并且最終是不可能的。

在旁觀者的眼中

與圖1中的信號看起來一樣糟糕,它在現代高速系統中的行為甚至比人們預期的還要糟糕。只有當我們以特殊的方式觀察信號時才會變得明顯 - 眼圖 - 這些日子在非常高速的信號傳輸中是必不可少的。

多年來,數字設計依賴于穩定的飲食習慣。眾所周知的技術;寬并行總線,同步時鐘,簡單的建立和保持型定時和軌到軌切換。但隨著對更快系統的追求推進,最終舊策略變得緊張;信號之間的串擾變得越來越難以避免,偏差控制變得困難,時間裕度變得不可能緊張。

最后,大約五六年前推出了一種新的信號傳遞方式,這些信號提供了一些緩解,首先是形式的LVDS(低壓差動擺動)。這些器件引入了兩個關鍵變化:較低的信號擺幅電壓(即使降低了噪聲容限)允許較慢的擺率;和差分信號,大大減少了串擾和輻射發射,并允許更窄,更快的數據路徑。

過去兩年看到LVDS型信號的爆炸性杠桿化進入了一場全面的革命 - 引言高速串行總線,可將數百MHz范圍內的數據速率(和信號頻率)推至1 GHz以上。突然間,廣泛的并行總線和全球時鐘(在某些情況下,任何類型的顯式時鐘)已成為通過; “in”是超快速,非常窄,全差分,低電壓擺動標準,如PCI Express,RapidIO和XAUI。

這將我們帶回眼圖。在新的高速串行世界中,數據速率如此之高(為了補償較窄的數據路徑,每個“通道”必須承載更多流量),各個位之間的時間通常幾乎不比上升/下降時間長得多攜帶比特的信號。丟失突然成為一個大問題,因為信號上升/下降時間的任何增加都會導致整個比特流失敗。更糟糕的是,誤差幅度很小,稱為符號間干擾(ISI)的現象占主導地位。

ISI基本上意味著數據速率相對于信號的上升時間而言是如此之高,以至于給定位的確切形狀和時間取決于先前的位歷史。這可能是因為驅動器IC本身不能保證位之間的完全規則定時(“抖動”的形式),或者因為反射和其他效應比位間隔更慢地消失,或者由于電壓的微小變化由于位歷史而產生的級別。例如,1的長序列會導致平均電壓電平向上漂移。通常,所有這些影響同時適用。

在信號完整性分析的“經典”時代,有可能專注于信號的單個上升沿或下降沿來判斷其“良好” - 是否響起,打撈,需要終止等等。但是在高速串行信令中,在進行任何綁定判斷之前,必須按順序分析多個比特。更糟糕的是,從來都不清楚什么位歷史(什么序列,多長時間)會產生最壞情況的行為。唯一的辦法是用一個長的隨機比特序列來驅動一個被測試的數據路徑,并希望任何病理行為都變得明顯。

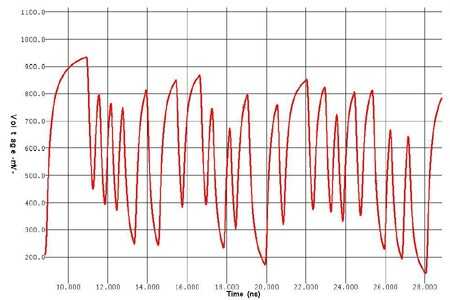

圖4顯示了這種模擬的一部分。跡線有意長,以包含健康劑量的高頻損耗,其表現為信號衰減和降低的邊緣時間,其長度與位間隔相似。符號間干擾很容易看出;特別是電壓電平明顯取決于先前位的歷史。然而,分析具有這種形式結果的數據路徑充其量是乏味的。想象一下,滾動數百甚至數千位,試圖想象何時會發生某種情況會混淆接收器IC。

圖4 - 高速串行數據路徑仿真的一部分,用PRBS(偽隨機比特序列)驅動,以便運用盡可能多的內部 - 符號干擾盡可能。請注意每個位的形狀和位置與先前位歷史記錄的明確依賴關系。

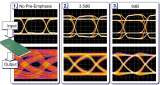

輸入眼圖,這是一種將長模擬結果壓縮成如圖4所示的簡單技術單一,易于理解和解讀的圖片。從概念上講,眼圖很容易創建;只需按照與位時間相關的規則間隔對圖4的波形進行切割,將每個切碎的段放在前一段的頂部,然后查看一個重疊堆中的所有數據。圖5顯示了此過程的結果,與圖4中顯示的數據完全相同。

圖5 - 與以下相同的模擬圖4,但數據覆蓋在眼圖中。請注意數據中間的小開口 - 一個近乎閉合的眼睛,這對這條信號路徑造成了災難。解釋眼圖比在標準模擬輸出中滾動長序列更快更確定。一目了然,眼睛的“開放性”告訴我們數據流是否可以接受。

圖5中的眼睛基本上是一場災難。在不知道特定信令技術的細節的情況下,接收器IC很難恢復由驅動器發送的所有(或可能是任何)數據。接收到的位在時間和電壓方面明顯漂移。

如果他們沒有,這張照片看起來很像“眼睛”;由高低信號狀態形成的上部和下部“蓋子”中間的寬開口。不幸的是,這里的眼睛幾乎是閉著的。這是一個嚴重麻煩的數據路徑 - 眼圖使其一目了然。

睜大眼睛?

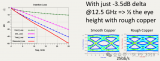

信號在圖5中,在以下條件下產生:40英寸跡線,4密耳跡線寬度,標準FR-4電介質,具有“損耗角正切”(廣泛使用的介電損耗測量)0.02。在本節中,讓我們看看減少損耗如何改善信號質量以及眼圖如何使我們獲得的改進立即明顯變得明顯。

之前,我們注意到丟失的一個組成部分是由于導體本身,以皮膚抵抗的形式。因此,如果我們能夠誘導高頻信號的電流流過更大的金屬橫截面,那么對信號的阻抗就會減小,損失就會減少。

我們知道,高頻電流往往會擠在導體的邊緣,靠近周邊。因此,如果我們增加導體的周長,我們應該減少損失。增加軌跡橫截面周長的最簡單方法是擴大軌跡。從布線密度的角度來看,4密耳的走線寬度是很好的,但不是最小化損耗的理想選擇。讓我們嘗試將跡線寬度從4密耳增加到8密耳。當然,我們也會增加電介質厚度,以保持50歐姆的特性阻抗。

圖6顯示了兩個產生的眼圖,一個在另一個之上(紅色表示4密耳的跡線,黃色為8密耳)。有趣的是,這個簡單的改變?更寬的走線寬度??確實減少了損耗并提高了信號質量,正如8密耳寬的跡線更開闊的眼睛所示。

圖6 ??與圖5中的模擬相同,使用4密耳寬的跡線(紅眼圖)運行一次,使用8密耳(黃色)運行一次。更寬的跡線具有更少的皮膚效應損失,因此更好的信號質量,如更開放的眼睛所示。

讓我們進行另一項改變,我們知道這將進一步減少信號損失。我們已經攻擊了皮膚抵抗力;現在讓我們去介電損耗。降低介電損耗的最簡單方法是將材料從圖4-6中使用的相對有損的FR-4改變為具有更好性能的材料。事實證明,這種電介質存在,盡管它們的成本并不像FR-4那么低或廣泛使用。在這些更好的材料中,損耗角正切可低至FR-4的十分之一;讓我們嘗試一個名為GML3000的損耗角正切為0.004。

圖7顯示了前后效果。果然,信號質量再次提高;低損耗的眼睛(紫色)比其伴侶打開得更寬。不幸的是,用這種外來電介質制造的PCB比用FR-4制造的PCB更昂貴?正如我們不得不降低布線密度以降低皮膚電阻(更寬的走線),現在我們面臨更高的制造成本,因為我們試圖降低介電損耗。

圖7 ??與圖6中更好的眼睛相同的模擬,使用典型的FR-4電介質(損耗角正切= 0.02;黃眼圖)運行一次,使用低損耗電介質運行一次(損耗角正切= 0.004;紫色)。低損耗材料對眼圖開度有了實質性的改善,但會導致PCB成本更高。

結論

<我們已經探索了信號丟失的概念,描述了導致它的原因,展示了它對高速信號的影響是如何測量的,并且看到了一些如何最小化它的例子。顯然,在高速系統中,損耗是一個日益嚴重的問題,特別是在高速串行信號的新世界中。

隨著數據速率增加到信號上升/下降時間與位間隔相同的程度,眼圖是判斷數據流是否受損失嚴重影響的重要工具,接收器IC不再能夠可靠地恢復數據。眼圖也可以立即明確是否最大限度地減少損失的嘗試實際上提高了信號質量,以及增加了多少。

Steve Kaufer是MentorGraphics高速工具工程總監。他在Innoveda和PADS Software擔任過類似的職位,而加入PADS的priorto是HyperLynx的聯合創始人,HyperLynx是信號完整性軟件的早期供應商。他擁有硬件和軟件工程方面的經驗,并擁有西雅圖大學的電子工程和物理學位。可以通過[email protected]與他聯系。

Eric Bogatin在麻省理工學院獲得物理學學士學位,在亞利桑那大學獲得物理學碩士和博士學位。 1980年在圖森工作。20多年來,他一直積極參與信號完整性和互連設計領域。他曾在AT&amp; T貝爾實驗室,Raychem公司,Sun Microsystems和Ansoft工作多年。最近,他將他的咨詢公司Bogatin Enterprises與GigaTest Labs合并,擔任首席技術官,并教授信號完整性短期課程。他已就此主題撰寫了3本書和100多篇論文。可以通過[email protected]與他聯系.www.gigatest.com

-

pcb

+關注

關注

4357文章

23438瀏覽量

407181 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

43775

發布評論請先 登錄

5G時代下的PCB材料趨勢:低損耗與高導熱如何平衡?

高速PCB板的電源布線設計

PCB問這個問題好怕你們笑我:為啥我的損耗曲線是“彎”的啊?

PCB的介質損耗角是什么“∠”?

如何選擇高品質PCB?捷多邦助力提升電氣性能

高速PCB設計EMI防控手冊:九大關鍵步驟詳解

明明我說的是25G信號,你卻讓我看12.5G的損耗?

高速PCB設計指南

高速信號傳輸鏈路的損耗和均衡

管理高速PCB的損耗有多大

管理高速PCB的損耗有多大

評論