模擬的有效使用為產(chǎn)品開發(fā)團(tuán)隊提供了多種優(yōu)勢。有效模擬的主要好處是更快的上市時間,更高的質(zhì)量和更低的風(fēng)險。通過提供增強(qiáng)的可控性和可觀察性,精心設(shè)計的仿真可以測試在原型調(diào)試環(huán)境中難以生成的情況。完全控制環(huán)境后,您可以輕松檢查邊界條件。最壞情況可能包括同時發(fā)生在實(shí)際系統(tǒng)中難以實(shí)現(xiàn)的獨(dú)立功能。您可以在可控模擬中設(shè)置這些條件。

模擬還可以對您的設(shè)計進(jìn)行更廣泛的觀察。無論設(shè)備上是否有備用I/O引腳,都可以使用內(nèi)部信號。您可以在模擬過程中更輕松地探測外部信號。通過幾次擊鍵或鼠標(biāo)點(diǎn)擊,您可以使用一個好的邏輯模擬器在幾秒鐘內(nèi)探測64位數(shù)據(jù)總線;嘗試使用邏輯分析儀。可能需要在實(shí)驗(yàn)室中花費(fèi)大量時間來設(shè)置復(fù)雜的監(jiān)控設(shè)計。

可控性和可觀察性的這些優(yōu)勢使您可以更快速,更輕松地捕獲模擬錯誤而不是硬件調(diào)試。此外,您可以在模擬中比在硬件原型上更快地更改設(shè)計。此功能縮短了調(diào)試周期并簡化了集成,尤其是在集成之前模擬不同模塊的情況下。仿真不僅減少了調(diào)試周期,而且還需要更少的原型硬件設(shè)計更改。對于那些不得不建造第二塊原型板的人來說,這個功能是個好消息,因?yàn)樵O(shè)計需要做出很多改動。設(shè)計一個新的印刷電路板很容易增加幾個星期的時間表。使用更高級別的技術(shù),您可以使用仿真來測試基本設(shè)計方法的可行性。

常見的模擬錯誤

一個關(guān)鍵問題是,“什么能阻止模擬效率?”基本問題通常是使用低級方法,例如波形矢量輸入,用于大型和復(fù)雜的設(shè)計。反過來,這種技術(shù)會導(dǎo)致系統(tǒng)仿真中的許多典型故障,包括故障覆蓋不足和電路響應(yīng)特性不足。在大型設(shè)計中,很難通過低級方法獲得適當(dāng)?shù)墓收细采w,這迫使您手動生成每個向量和測試用例。當(dāng)矢量生成繁瑣且耗時時,可能難以指定所有感興趣的測試場景。即使您指定了測試用例,也可能難以完成它們。由于大多數(shù)使用簡單技術(shù)的項(xiàng)目使用視覺檢查來鑒定電路響應(yīng),因此您可能會錯過許多可見電路故障。更強(qiáng)大的仿真技術(shù)實(shí)際上簡化了設(shè)計驗(yàn)證的任務(wù)。有些人認(rèn)為處理復(fù)雜性的唯一方法是層次結(jié)構(gòu)和抽象。建模利用層次結(jié)構(gòu)和抽象,使復(fù)雜系統(tǒng)的仿真既可管理又有效。

良好測試平臺的目標(biāo)

良好測試平臺的關(guān)鍵要求是完整性,易用性,靈活性,可重用性和運(yùn)行時效率。這些功能是相互關(guān)聯(lián)的:靈活的設(shè)計更易于使用,更易于完成,并且更易于重復(fù)使用。

高故障覆蓋率對于有效的仿真項(xiàng)目至關(guān)重要。良好的模擬策略有助于開發(fā)涵蓋所有相關(guān)操作方案的測試平臺。您可以通過使用允許模擬設(shè)計人員在相當(dāng)高的抽象級別工作的技術(shù)來最好地實(shí)現(xiàn)此目標(biāo)。如果您可以在宏級別而不是在原子級別指定測試方案,則更容易遵循模擬流程。一個好的模擬技術(shù)應(yīng)該支持高水平的抽象。 VHDL具有許多支持高級行為建模的功能,可輕松滿足此要求。基于系統(tǒng)級組件建模的仿真方法自然可以在高級抽象中工作。例如,擁有CPU模型允許您指定總線循環(huán)的類型。圍繞CPU模型構(gòu)建測試平臺允許您以類似于編寫診斷程序的程序員的方式設(shè)置測試模式。在高級別,模擬通過設(shè)置DMA傳輸,編程I/O和各種總線操作自然流動。這種方法允許工程師專注于測試的功能需求,將位操作留給硬件模型。

雖然模擬方法應(yīng)該易于使用,但這種策略涉及陷阱:方法是易于使用的小型設(shè)計無法很好地擴(kuò)展到更復(fù)雜的設(shè)計。使用預(yù)驗(yàn)證功能模型庫,您可以輕松構(gòu)建具有全面時序和數(shù)據(jù)檢查的測試平臺。一個好的庫在模型本身中具有這些功能。編寫測試用例也很容易,因?yàn)闇y試平臺的“虛擬系統(tǒng)”模仿了實(shí)際硬件的操作。任何了解硬件系統(tǒng)操作的人都可以理解完成測試設(shè)計所需的步驟。

良好的模擬方法必須足夠靈活,以便在測試系統(tǒng)獲得知識或測試要求變化時允許更改模擬。如果測試臺等同于一堆“意大利面條代碼”,則修改測試臺很困難。面向?qū)ο蟮能浖夹g(shù)可用于為計算機(jī)程序員提供這種靈活性。將功能嵌入到功能模型組件中為工程師設(shè)計復(fù)雜的芯片或系統(tǒng)仿真提供了類似的好處。為了易于修改,硬件設(shè)計應(yīng)具有強(qiáng)大的內(nèi)聚力和松散耦合。設(shè)計中的控制路徑應(yīng)該很簡單。通過在測試平臺中模仿系統(tǒng)設(shè)計的結(jié)構(gòu),您可以輕松復(fù)制系統(tǒng)的行為。如果系統(tǒng)設(shè)計發(fā)生更改,您可以直接修改測試平臺模型以確保它與系統(tǒng)匹配。建模還有助于其他方面的靈活性。定義與組件模型關(guān)聯(lián)的功能允許您在一個地方進(jìn)行更改,這些更改可以在您使用組件的任何位置產(chǎn)生效果。將其與簡單測試平臺上常見的全局搜索和替換或剪切和粘貼操作進(jìn)行對比。正確的建模應(yīng)該產(chǎn)生靈活的仿真架構(gòu)。

設(shè)計重用正在成為縮小深亞微米VLSI設(shè)計方法中生產(chǎn)力差距的主要因素。承諾快速上市的高密度FPGA和CPLD需要類似的技術(shù)。因?yàn)樾酒举|(zhì)上是可重復(fù)使用的,所以模擬其行為的仿真模型也是如此。正如設(shè)計師習(xí)慣性地在許多設(shè)計中使用許多相同的組件一樣,您也可以重用良好的仿真模型。

一個好的測試平臺必須快速執(zhí)行。與低級方法相比,建模沒有固有的優(yōu)勢。正如一個好的匯編語言程序通常比用高級語言編寫的程序更快,低級別的測試平臺可能比相應(yīng)的建模仿真更快。對于復(fù)雜的仿真,建模的優(yōu)勢遠(yuǎn)遠(yuǎn)超過仿真速度的降低。典型FPGA的執(zhí)行時間小于開發(fā)仿真套件所花費(fèi)的時間。此外,當(dāng)您根據(jù)功能實(shí)體或模型正確劃分模擬時,可能更容易隔離模擬的耗時部分并優(yōu)化這些部分。通常,精心設(shè)計的建模測試平臺不必比低級測試平臺慢得多。此外,盡管低級建模中的各個仿真周期可以更快地執(zhí)行,但是使用更高級別的技術(shù)提供完全仿真設(shè)計的總體目標(biāo)更快,因?yàn)楣收细采w更有效并且更不容易出錯。換句話說,使用較低級別的技術(shù)需要更長的時間來獲得更高級別技術(shù)提供的故障覆蓋率。

圖1a顯示了典型的簡單測試平臺的框圖。在清單1的代碼示例中,代碼結(jié)構(gòu)簡單而扁平。被測單元被實(shí)例化為一個組件,一個進(jìn)程控制主測試序列。內(nèi)聯(lián)代碼生成電路激勵,多個等待語句控制主序列時序。或者,您可以在傳輸語句中的條件之后使用多個來控制時序。 VHDL仿真的大多數(shù)新手用戶通過檢查結(jié)果波形來驗(yàn)證電路響應(yīng)。這樣的測試平臺通常很少或沒有電路性能的限定。

此測試平臺缺乏功能劃分使得實(shí)現(xiàn)復(fù)雜控制變得困難。例如,您可能希望改變控制信號時序,以驗(yàn)證被測單元是否能夠容忍其輸入上允許的所有變化。對testbench代碼的檢查表明,單個等待語句等待clk_period 會影響所有后續(xù)信號分配的時序。當(dāng)它們的定時是交互式時,可能難以管理各種刺激信號的定時。當(dāng)有人將這些等待語句多次復(fù)制并粘貼到大型進(jìn)程中時,這種情況會變得更糟。設(shè)計越復(fù)雜,這些方法就越不合適。靜態(tài)時序方案通常無法處理交互式芯片接口。實(shí)現(xiàn)這種握手的需要通常是驅(qū)動工程師考慮建模的首要原因。進(jìn)程可以使用條件順序語句, if-then-else 或 case 語句,積極與被測單位互動。雖然您可以在不構(gòu)建模型的情況下執(zhí)行此握手,但您不會統(tǒng)一結(jié)構(gòu)和功能。模型構(gòu)建的規(guī)則是有用的,因?yàn)樗⒓幢砻鳒y試平臺的功能應(yīng)該模仿被測系統(tǒng)的交互性。

等待與傳輸語句

使用HDL模擬器最具挑戰(zhàn)性的方面之一是時間概念。在VHDL中,程序員將代碼廣泛地分類為并發(fā)或順序。多個順序代碼塊同時執(zhí)行,并使用敏感列表或等待語句來調(diào)整其執(zhí)行速度。在一個過程中,軟件會調(diào)度事件,但在程序遇到wait語句之前,模擬速度不會更快。您可以使用多個等待語句來控制各種信號的排序,但這種方法會導(dǎo)致各個信號的時序相互作用,從而使其控制變得復(fù)雜。類似地,您可以使用傳輸延遲規(guī)范來計時信號轉(zhuǎn)換,但這些規(guī)范控制單個信號上的一系列轉(zhuǎn)換的時序,與所有其他信號無關(guān)。您仍然需要等待語句來加速模擬,但是由于一個或多個等待語句,時間推進(jìn)時,傳輸語句中的時序順序會滾動模擬事件輪。這些等待語句可能位于代碼的任何部分。使用傳輸語句單獨(dú)指定信號轉(zhuǎn)換更容易,但在調(diào)試期間逐步調(diào)試代碼通常更難解開時間。

您可以使用控制信號排序和定時的兩種方法試驗(yàn)臺。當(dāng)一組信號重復(fù)并同時改變時,等待語句最容易使用。這種情況通常是在每個時鐘周期內(nèi)同時改變的同步信號。在建模異步接口時,例如使用Intel風(fēng)格的微處理器,您可能需要單獨(dú)調(diào)整信號。使用等待語句延遲下游所有信號的應(yīng)用,這種方法涉及一個復(fù)雜的問題。單獨(dú)的傳輸語句允許您為每個信號指定一系列轉(zhuǎn)換延遲,為每個信號定義波形。雖然這種技術(shù)可以解耦信號時序,但它也使得更加難以可視化各個時序的排序。例如,如果關(guān)鍵要求是保證寫入選通結(jié)束時的地址保持時間,則可能更容易使用等待語句將模擬定時輪向前移動寫入選通的無斷言時間和地址巴士。您可能希望嘗試找出適合您的偏好和設(shè)計要求的內(nèi)容。在調(diào)試期間,多個等待語句比傳輸語句更容易一步,但傳輸語句對于描述相同的行為更為緊湊。通過建模的模塊化,可以很容易地使用最適合的每種機(jī)制。

您可以通過添加檢查被測單元響應(yīng)的語句來略微改進(jìn)這個簡單模型(圖1b)。在這樣一個簡單的方案中,自動檢查數(shù)據(jù)是一種喜憂參半的祝福。使用簡單的測試平臺,很難有足夠的控制來完成驗(yàn)證電路響應(yīng)所需的所有檢查。只是在正確的時間對數(shù)據(jù)進(jìn)行采樣可能很困難。當(dāng)程序強(qiáng)制模擬的所有代碼駐留在平面模型中的一個進(jìn)程中時,檢查建立 - 保持時間和所有其他重要參數(shù)是一項(xiàng)艱巨的任務(wù)。通過設(shè)置多個進(jìn)程來檢查信號,參數(shù)或接口,您可以在某種程度上解決這種情況,但是這個臨時進(jìn)程很難控制,管理和維護(hù)。由于混合了結(jié)構(gòu)和功能,因此很難在新應(yīng)用中重復(fù)使用這些設(shè)計。

關(guān)鍵建模特性

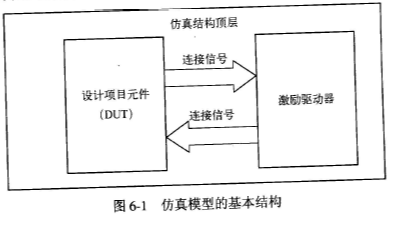

基于建模的測試平臺背后的基本思想是創(chuàng)建圍繞被測單元的所有板級組件的功能模型(圖2)。頂級文件通常包含結(jié)構(gòu)化VHDL代碼,它將各種模型連接在一起作為實(shí)例化組件。至少一個組件是被測單元。其他組件是板上其他設(shè)備的功能等同物。在此示例中,您需要模擬萊迪思CPLD。該設(shè)計是33 MHz i960RP微處理器和雙組SRAM之間的接口。它允許系統(tǒng)通過交替訪問兩組SRAM來以半個總線速度訪問存儲器。 CPLD是被測單元,但您必須為CPU,時鐘,收發(fā)器和SRAM建模。 SRAM模型可以在每個訪問周期檢查來自被測單元的所有信號。您可以輕松地將所有必需的設(shè)置,保持和脈沖寬度檢查放入SRAM模型中。將這些檢查放入一個簡單的結(jié)構(gòu)中是很困難的,特別是當(dāng)您需要將所有其他檢查包含在測試中時。設(shè)計人員的任務(wù)更容易,功能模型中嵌入了信號檢查。

功能系統(tǒng)建模的一個有趣方面涉及定義整體控制機(jī)制。在一個簡單的測試平臺中,測試設(shè)計者最自然地將主要測試過程置于層次結(jié)構(gòu)的頂層,通常是在包含一個文件的測試平臺中。在基于模型的測試平臺中,設(shè)計中的數(shù)據(jù)流控制器與實(shí)際系統(tǒng)中的控制器平行。對于智能卡,該控制器是CPU或微控制器。您可能會通過系統(tǒng)總線控制從屬適配器卡。在此示例中,i960處理器是系統(tǒng)控制器,模擬自然地流經(jīng)CPU模型。主要控制過程甚至不在測試平臺的頂層;它嵌入在CPU模型中。對于那些僅使用簡單測試平臺的人來說,這種情況可能看起來很奇怪,但這是建模的自然結(jié)果。

在這個例子中,內(nèi)存和SRAM控制器都是從設(shè)備。由于CPU模型驅(qū)動模擬,因此設(shè)計人員只需要使用一種方法來指定總線周期序列,以便將數(shù)據(jù)路由到設(shè)計中。 CPU模型生成所有單獨(dú)的總線信號。通過在更高級別處理模擬,設(shè)計人員可以處理系統(tǒng)級功能并讓模型處理細(xì)節(jié)。生成模型后,您可以比使用低級方法更快地開發(fā)復(fù)雜的功能模擬。

建模通常將控制路徑功能的驗(yàn)證與數(shù)據(jù)路徑功能的驗(yàn)證分開。簡單方法合并這些功能,再次使模擬控制問題復(fù)雜化。該模型通常驗(yàn)證控制路徑功能。使用SRAM模型,您可以輕松確定需要進(jìn)入模型的代碼,以驗(yàn)證控制信號是否正常運(yùn)行。將時序檢查放入SRAM模型允許您在模型訪問SRAM時將檢查放在一個活動的位置。您可以在行為模型中實(shí)現(xiàn)其他控制路徑計時和功能驗(yàn)證。您有時可以在模型中內(nèi)部測試數(shù)據(jù)路徑功能,如CRC生成器/檢查器的情況。通常,在更高的抽象級別檢查數(shù)據(jù)路徑更合理。在這種情況下,讓CPU模型執(zhí)行寫回讀周期以驗(yàn)證存儲器子系統(tǒng)的操作更方便。 CPU模型驗(yàn)證數(shù)據(jù)完整性。您執(zhí)行驗(yàn)證的方式與為微處理器編寫自檢代碼的方式大致相同。對于功能齊全的CPU模型,您可以使用為系統(tǒng)自檢而開發(fā)的相同代碼,并進(jìn)行有限的修改以運(yùn)行模擬;反之亦然。

幸運(yùn)的是,您無需使用神秘的方法來開始設(shè)計建模測試平臺。與面向?qū)ο缶幊滩煌瑴y試平臺建模不需要工程師考慮系統(tǒng)設(shè)計的方式進(jìn)行批發(fā)范式轉(zhuǎn)換。由于測試臺模擬的結(jié)構(gòu)是硬件設(shè)計,因此構(gòu)建具有功能模型的測試平臺需要工程師通過多年使用原理圖和實(shí)驗(yàn)室設(shè)備開發(fā)的相同分析方法。您只需使用VHDL設(shè)計中的功能組件替換電路板上的組件,然后找出如何為每個組件建模。當(dāng)硬件工程師通常編寫診斷代碼時,計劃模擬就像計劃原型調(diào)試的早期階段一樣。

當(dāng)您在全公司范圍內(nèi)采用建模時,建模是最有利的。您必須設(shè)計,實(shí)施和驗(yàn)證您不購買的任何型號。您必須在低抽象級別驗(yàn)證模型,明確地查看詳細(xì)的功能和時序。使用模型測試設(shè)計的工程師可以是驗(yàn)證模型的同一工程師。因?yàn)榻I婕昂瘮?shù)的封裝,所以這種情況有助于防止自我實(shí)現(xiàn)的預(yù)言,其中測試平臺設(shè)計者使系統(tǒng)設(shè)計者做出的假設(shè)假設(shè)持續(xù)存在。您可以組織模型構(gòu)建,將其計劃到設(shè)計計劃中,并將其劃分為設(shè)計團(tuán)隊工程師。您應(yīng)該建立標(biāo)準(zhǔn)以確保生成的模型的一致性和質(zhì)量。這種方法確保了預(yù)驗(yàn)證模型庫的存在,這些模型是提高設(shè)計團(tuán)隊的仿真能力和效率的寶貴資源。

如果開發(fā)復(fù)雜模型的努力超出了工程組的能力范圍,應(yīng)該考慮從外部來源獲取模型。標(biāo)準(zhǔn)合規(guī)性通常要求完全驗(yàn)證和合規(guī)的模型。所有標(biāo)準(zhǔn)總線型號,包括PCI,SCSI,VME和ISA,以及知識產(chǎn)權(quán)(IP)供應(yīng)商經(jīng)常提供的型號都可用。 Synopsys的邏輯建模部門提供各種總線接口模型,有助于驗(yàn)證標(biāo)準(zhǔn)總線設(shè)計的合規(guī)性和互操作性。許多其他第三方供應(yīng)商也提供各種核心供應(yīng)。您可以在Web上找到令人印象深刻的非商業(yè)模型源列表(參考文獻(xiàn)1,2和3)。

建模和抽象

VHDL的發(fā)明者將該語言設(shè)想為純粹的建模語言。用于邏輯綜合的VHDL的早期采用者存在問題,因?yàn)樵S多有用的建模構(gòu)造不適合于合成。其次,VHDL規(guī)定您實(shí)現(xiàn)Verilog的許多必要功能,例如類型轉(zhuǎn)換,作為庫函數(shù)。相比之下,您可以使用全范圍的VHDL建模功能來生成行為仿真模型。您可以指定復(fù)雜行為,而不遵守綜合支持的RTL約定。您甚至可以使用VHDL的數(shù)學(xué)函數(shù)對模擬和機(jī)械系統(tǒng)進(jìn)行建模。 (VHDL目前正在考慮的模擬擴(kuò)展主要是語言當(dāng)前可用數(shù)學(xué)函數(shù)的擴(kuò)展。)因?yàn)槟恍枰铣煞抡婺P停钥梢允褂迷S多高級行為結(jié)構(gòu)來簡化函數(shù)模型生成。根據(jù)執(zhí)行它們的組件定義函數(shù)會產(chǎn)生功能分解,從而鼓勵更高級別的抽象。該技術(shù)將功能規(guī)范與低級操作細(xì)節(jié)分離,并簡化了編寫測試程序的過程。表1和表2匯總了VHDL的許多特性和屬性,這些特性和屬性對于生成建模仿真很有用。

雖然VHDL本身不是VHDL的一個特性,但大多數(shù)VHDL和Verilog仿真包允許用戶接口可執(zhí)行程序到模擬。這些程序通常用C或C ++編寫,允許用戶在沒有使用VHDL模型的速度或空間開銷的情況下實(shí)現(xiàn)復(fù)雜的行為。例如,在C中建模大型SRAM模型允許操作系統(tǒng)資源實(shí)現(xiàn)數(shù)據(jù)存儲。如果操作系統(tǒng)可以緩存數(shù)據(jù)并在必要時將其交換到磁盤,則可以建模超過PC或工作站上可用RAM大小的內(nèi)存。或者,您可以使用C對系統(tǒng)進(jìn)行建模,并使用模擬器允許C程序訪問模擬器中的組件模型。對于大型模擬,這種方法可能比VHDL更快,但需要包括VHDL和C開發(fā)工具的環(huán)境。這種方法可能有助于工程師在分區(qū)之前使用C語言模擬系統(tǒng)并將其交給電路設(shè)計人員進(jìn)行實(shí)施。

什么是配置?

VHDL定義了一個配置設(shè)計單元,它大致類似于印刷電路板組件的部件列表。您需要配置,因?yàn)榻o定實(shí)體可能涉及多個體系結(jié)構(gòu)。 VHDL關(guān)鍵字配置指定的配置聲明標(biāo)識體系結(jié)構(gòu)與每個實(shí)體的配對或綁定。除非指定多個體系結(jié)構(gòu),否則不需要顯式配置。配置對模擬最有用;綜合工具通常不支持它們。

1987 VHDL標(biāo)準(zhǔn)的文件I/O功能有限。 1993版增加了語法增強(qiáng)功能和新功能,以擴(kuò)展語言的文件I/O功能。您可以通過各種方式使用VHDL文件I/O功能。主要用途是檢索和應(yīng)用刺激向量;存儲響應(yīng)向量和預(yù)期響應(yīng)以進(jìn)行比較;格式化報告;然后讀取自定義的測試語言文件,然后程序解析。

您可以使用具有更高抽象級別的測試語言文件讀取來控制模擬。因?yàn)槟诠δ芗墑e指定命令,所以根據(jù)其編程響應(yīng)每個命令的功能模型執(zhí)行詳細(xì)實(shí)現(xiàn)。這種強(qiáng)大的技術(shù)可以在很高的層次上推動模擬。您可以最大程度地利用系統(tǒng)級知識,因?yàn)槟梢栽谧罘奖銠z查系統(tǒng)功能的級別上進(jìn)行控制。當(dāng)文本文件確定控制流時,自定義測試語言將變?yōu)樘囟ㄓ谀M。 VHDL模擬解釋代碼。您可以快速生成和檢查新的測試用例,因?yàn)槟恍枰幾g新代碼,因?yàn)樗皇荲HDL測試平臺的一部分。表3顯示了最常見的基本文件I/O命令。表4顯示了標(biāo)準(zhǔn)文本I/O包中添加的常用命令。

使用模型設(shè)計測試平臺

IEEE提供的資源,包括在線筆記,是編寫行為模型的優(yōu)秀指南(參考文獻(xiàn)4,5和6)。關(guān)鍵點(diǎn)是在多個抽象層次上建模系統(tǒng),隱藏系統(tǒng)結(jié)構(gòu),關(guān)注行為和功能,忽略頂層抽象時序,遵循軟件工程的標(biāo)準(zhǔn)實(shí)踐,簡化維護(hù)和重用,構(gòu)造設(shè)計,定義每個組件以具有強(qiáng)大的內(nèi)聚力,定義松散耦合的組件集,使用自上而下的迭代細(xì)化,以及使用抽象數(shù)據(jù)類型來隱藏和封裝數(shù)據(jù)。

使用VHDL,系統(tǒng)設(shè)計人員可以在多個抽象級別對電路建模。在VHDL中進(jìn)行建模時,遵循軟件工程的標(biāo)準(zhǔn)實(shí)踐非常重要。否則,即使對于編寫模型的人來說,模型也難以維護(hù)。此外,為了幫助重用模型,您應(yīng)該仔細(xì)考慮并重新使用,甚至創(chuàng)建一次性模型。典型的模型設(shè)計和編碼實(shí)踐包括結(jié)構(gòu)設(shè)計;迭代地將模型的高級視圖細(xì)化到最終形式;使用抽象數(shù)據(jù)類型來隱藏和封裝數(shù)據(jù);并組織各個模型組件,使它們與極少的接口信號松散耦合,并具有強(qiáng)大的內(nèi)聚力,在同一架構(gòu)體中保持強(qiáng)相關(guān)的功能。

在圖3中,原理圖鏈接了CPLD的設(shè)計基于SRAM的控制器,用于設(shè)計中所有其他主要組件的模型。該Ramix Corp CPLD設(shè)計針對的是萊迪思M4A5-192/96-7VC器件。 Ramix選擇此部件是因?yàn)閮?nèi)部延遲的速度鎖定使器件能夠以132 MHz的有效內(nèi)部頻率工作。該設(shè)計需要在66 MHz時鐘的兩個邊沿上進(jìn)行狀態(tài)更改。使用最高速度會將可用頻率推至180 MHz左右。

CPU模型生成總線周期來控制仿真。表5列出了指定測試序列的特殊指令。指令很簡單,并在所需的總線操作之后建模。對所有匯編語言操作代碼進(jìn)行建模可能過于復(fù)雜,而且不太有用。該模型僅需要10條指令,這些指令包括設(shè)置給定操作的地址和數(shù)據(jù)。通過這些指令,您可以檢查所有各種讀取和寫入SRAM的模式。測試平臺使用簡單的命令組合來實(shí)現(xiàn)所有必需的測試方案。該模型有兩個實(shí)現(xiàn)。更簡單的模型將測試序列嵌入到模型本身中,實(shí)現(xiàn)為每次更改測試時必須編譯的VHDL代碼。此過程違反了將高級任務(wù)與低級任務(wù)分離的愿望。在第二個過程中,測試語言解析引擎驅(qū)動模擬。文本解析引擎似乎增加了額外的復(fù)雜性,但它在靈活性和易用性方面具有優(yōu)勢。由于外部文本文件包含測試序列,因此程序無需在運(yùn)行之前編譯序列。此功能可讓您快速輕松地添加測試方案。實(shí)際上,該方法提供了一種獨(dú)立于應(yīng)用程序的仿真語言,您可以在i960 CPU上需要此功能的任何系統(tǒng)中使用該語言。

存在幾種實(shí)現(xiàn)SRAM模型的選項(xiàng)。您可以將模型實(shí)現(xiàn)為數(shù)組,只需根據(jù)位置地址將數(shù)據(jù)存儲在數(shù)組位置即可。另一種選擇是構(gòu)建一個可以將地址和內(nèi)存數(shù)據(jù)傳輸?shù)酱疟P文件以便以后驗(yàn)證的模型。此示例不要求內(nèi)存通過設(shè)計傳遞大量數(shù)據(jù)。工程師使用兩個16字深的數(shù)組設(shè)計存儲器來存儲數(shù)據(jù) - 一個存儲在模型的較低地址空間,另一個存儲在頂端。設(shè)計人員實(shí)現(xiàn)了第二個陣列,允許RAM訪問從一個頁面滾動到另一個頁面。該設(shè)計使用SRAM地址索引到數(shù)組中。該模型響應(yīng)標(biāo)準(zhǔn)寫使能,輸出使能,片選,地址和數(shù)據(jù)RAM控制信號。該設(shè)計在執(zhí)行合法寫周期時將數(shù)據(jù)存儲在陣列中,并在執(zhí)行合法讀周期后檢索數(shù)據(jù)。除了存儲和檢索數(shù)據(jù)外,該模型還可以檢查SRAM時序要求。您可以選擇時間參數(shù)為none,minimum,typical或maximum。最小訪問時間無關(guān)緊要,因此設(shè)計人員將其設(shè)置為零延遲。

芯片選擇解碼模型是一種簡單的組合解碼器功能,無需參數(shù)檢查。該模型復(fù)制了電路的功能和傳播延遲時序。您可以選擇延遲為無,最小,典型或最大。鎖存收發(fā)器模型是一種簡單的順序模型,具有有限的參數(shù)檢查功能,可用于數(shù)據(jù)設(shè)置和保持。

該電路的簡單功能需要簡單的測試用例。您可以通過寫入SRAM并讀取數(shù)據(jù)來完成i960型號的每種總線周期類型。測試用例包括單次寫入然后讀取,存儲區(qū)0或1啟動,突發(fā)寫入然后讀取,存儲區(qū)0或1啟動,有或沒有CPU等待狀態(tài),有或沒有SRAM分頁符,以及與頁面中斷重疊CPU等待狀態(tài)。這些相對簡單的情況足以測試存儲器控制CPLD的功能。 CPU模型通過在回讀時驗(yàn)證寫入的數(shù)據(jù)是否相同來檢查數(shù)據(jù)路徑。 SRAM模型需要適當(dāng)?shù)目刂菩盘杹泶鎯蜋z索數(shù)據(jù),檢查控制信號。這些模型的定時檢查分布在整個身上。 CPU,SRAM和鎖存收發(fā)器模型都包含代碼以驗(yàn)證正確的信號時序。如果測試不符合所需的設(shè)置,保持或脈沖時序,則檢測到錯誤的模型會報告每個錯誤。您可以使用CPU模型中的基本指令在模型中構(gòu)建新場景。

您可以從行為模型測試平臺輕松檢查列表。最后一行告訴是否存在任何錯誤。如果沒有錯誤,您的工作就完成了。如果發(fā)生故障,快速檢查會顯示位置,以及有關(guān)故障位置和原因的線索。每次運(yùn)行模擬時,測試平臺都會自動運(yùn)行所有檢查。

-

模擬

+關(guān)注

關(guān)注

7文章

1436瀏覽量

84338 -

建模

+關(guān)注

關(guān)注

1文章

315瀏覽量

61428 -

PCB打樣

+關(guān)注

關(guān)注

17文章

2971瀏覽量

22349 -

華強(qiáng)PCB

+關(guān)注

關(guān)注

8文章

1831瀏覽量

28435 -

華強(qiáng)pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

43734

發(fā)布評論請先 登錄

基于VHDL-AMS的巴特沃斯二階濾波器行為建模與仿真(smash5.51)

TINA讓電路設(shè)計更輕松

是否可以在EMpro仿真中對BJT/MOSFET等器件進(jìn)行建模?

可以在硬件(Verilog)中更輕松地完成此任務(wù)嗎?

在使用IAR過程中,使用MSP430uif仿真中出現(xiàn)“could not find device(or device not suported)”

怎么實(shí)現(xiàn)PID控制器的VHDL-AMS行為級建模

TEXTIO及其在VHDL仿真中的應(yīng)用

混合信號系統(tǒng)的VHDL-AMS建模與仿真分析

電荷泵鎖相環(huán)的VHDL-AMS行為建模與仿真

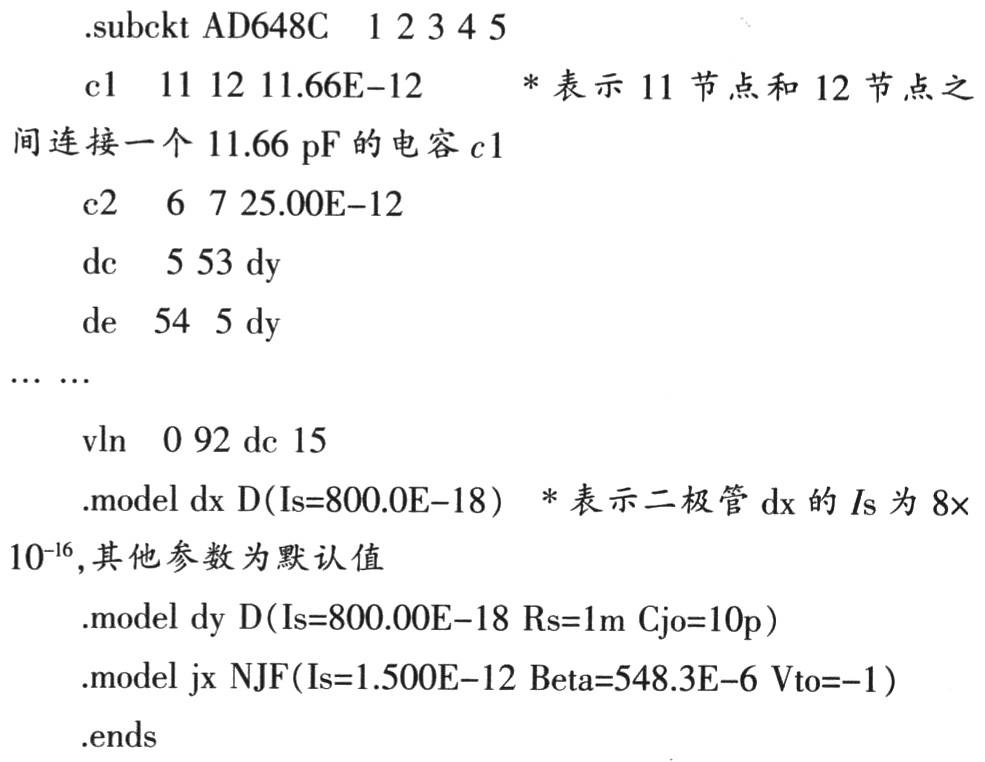

電子元器件在電路仿真中如何建模

基于Multisim的VHDL建模與仿真

如何建立VHDL程序的仿真模型和平臺及仿真過程詳細(xì)說明

VHDL仿真中的行為建模,讓您可以在模擬過程中更輕松

VHDL仿真中的行為建模,讓您可以在模擬過程中更輕松

評論