DDR驗證是任何SoC中最關(guān)鍵和最復(fù)雜的任務(wù)之一,因為它涉及位于DUT內(nèi)部的控制器和位于DUT外部的外部DDR存儲器。 DDR系統(tǒng)由控制器,I/O,封裝,插座,電源,時鐘和外部存儲器組成,它們共同工作。在數(shù)字驗證中,并非所有這些組件都進入圖像,而主要是控制器,PHY,I/O和存儲器。驗證變得更加復(fù)雜,因為所有組件的影響都無法在數(shù)字仿真中模仿,但門級仿真(GLS)為我們提供了良好的基礎(chǔ)設(shè)施來報告可能困擾控制器-PHY-I/O路徑的設(shè)計問題從時間的角度來看。

在GLS中驗證DDR時會遇到許多與時序相關(guān)的問題,導(dǎo)致驗證和STA(靜態(tài)時序分析)團隊之間的大量迭代。擁有干凈的調(diào)試GLS環(huán)境可以讓您對RTL(寄存器傳輸級別)運行的DDR協(xié)議的STA視角充滿信心,并且可以提供關(guān)注數(shù)字和時序方面的良好信心。由于RTL的時序可見性,本文整理了DDR的GLS(門級仿真)驗證中通常報告的廣泛問題,并通過大量示例強調(diào)了在GLS環(huán)境中快速有效地關(guān)閉DDR的重要調(diào)試標準。

RTL環(huán)境沒有任何時序感知,因此設(shè)計中沒有慣性/傳播延遲,但是當(dāng)我們移動時進入GLS設(shè)置后,這些進入了畫面并且必須得到有效處理,以便模仿實際的硅行為,同時不會使事情過于悲觀。在邏輯單元的輸入處,持續(xù)時間小于慣性延遲的脈沖將不能在該邏輯單元的輸出處引起任何轉(zhuǎn)變,邏輯門表現(xiàn)出的這種現(xiàn)象稱為慣性延遲傳播。工業(yè)標準GLS仿真工具通常將傳播延遲視為該邏輯門的慣性延遲。仿真工具采用的這種建模是對實際硅行為的相當(dāng)好的抽象,事實上,它很好地模擬了通過單級邏輯門的信號傳播。但是在IO等復(fù)雜門的情況下,這種行為是不可取的,其本質(zhì)上是多級的,并且一旦信號使其經(jīng)過第一級,就保證它將成功地傳播通過IO單元。由于仿真工具不了解邏輯單元的這種內(nèi)部結(jié)構(gòu),因此即使對于多級IO,它也會抑制脈沖,如圖1所示。

圖1:默認的GLS仿真行為是抑制所有小于門延遲的轉(zhuǎn)換

現(xiàn)在要解決這個問題,有兩種解決方案可能。

第一種解決方案是手動更新SDF并將延遲更新為更小的值。這種方法適用于正確傳播信號,但這種方法不正確,因為新的延遲不代表實際的延遲,可能會抑制其他潛在的功能問題。

行業(yè)標準的GLS模擬器確實有能力/開關(guān)可以允許/禁止通過細胞的一定寬度的脈沖。例如“拒絕&錯誤設(shè)置“使用時將傳播寬度大于'錯誤設(shè)置'的所有信號。雖然它會傳播信號的未知值,寬度介于'reject&錯誤設(shè)置'它將完全消除寬度小于'拒絕設(shè)置'的信號。一個例子如下表所示。

| Pulse_e& ; pulse_r | 行為 |

| pulse_e/100& pulse_r/100 | 拒絕所有小于傳播延遲100%的脈沖 |

| pulse_/0& pulse_r/0 | 傳遞大于0%傳播延遲的所有脈沖 |

| pulse_e/50& pulse_r/50 | 傳遞大于傳播延遲50%的所有脈沖。 |

表1:Pulse_e/Pulse_r行為

基于時序小組完成的平衡的時鐘選擇

在RTL設(shè)置中,由給定源驅(qū)動的時鐘到達同一節(jié)點的所有節(jié)點瞬間但是當(dāng)我們轉(zhuǎn)向GLS設(shè)置時,時鐘偏移進入圖像并因此可能產(chǎn)生定時問題,其中從相同源導(dǎo)出的兩個時鐘路徑可能具有偏斜,使得DDR數(shù)據(jù)/時鐘路徑不能平衡所有可能的組合。輸入時鐘是DDR設(shè)計中最重要的參數(shù),因為所有其他信號都是根據(jù)輸入時鐘周期和占空比得出的。可能存在多個時鐘源可用作控制器輸入時鐘的情況。通常,來自任何一個時鐘源的路徑是平衡的,建議用于DDR輸入時鐘。 DDR_CLK,DDR_DQS等信號有嚴格的要求傳播到外部DDR存儲器的占空比,高時間,低時間等,這些都需要滿足DDR的正確操作。寫入側(cè)的大多數(shù)與占空比要求相關(guān)的故障可能是由于DDR控制器輸入上的時鐘占空比不正確。必須正確地確保我們使用滿足時序的正確時鐘源,以避免不必要的調(diào)試。下面提到了相同的例子,其中存儲器輸入端的DQS占空比數(shù)據(jù)已經(jīng)被選為DDR控制器時鐘的2個不同時鐘源捕獲。

DDR_CLK頻率:400MHz(~2.5ns)

| 55%的2.524 ns = 1.388200ns |

| 2.524 ns的45%= 1.13580ns |

| 路徑不同層次結(jié)構(gòu)的脈沖寬度(Clk源1) | 高脈沖 | 低脈沖 |

| PLL輸出 | H:1291ps | L:1233ps |

| 在Cross-Bar輸入 | H:1270ps | L:1254ps |

| 在交叉條輸出 | H:1241ps | L:1283ps |

| 在控制器輸入 | H:1227ps | L:1297ps |

| 在DQS pad輸入 | H:1334ps | L:1190ps |

| 在DQS墊 | H:1377ps | L:1147ps |

| 路徑不同層次的脈沖寬度(Clk源2) | 高脈沖 | 低脈沖 |

| PLL輸出 | H:1294ps | L:1230ps |

| 在Cross-Bar輸入 | H:1210ps | L:1314ps |

| 在橫桿輸出 | H:1181ps | L:1343ps |

| 在控制器輸入 | H:1167ps | L:1357ps |

| 在DQS pad輸入 | H:1394ps | L:1130ps |

| 在DQS墊 | H:1437ps | L:1087ps |

表2:不同層次結(jié)構(gòu)的時鐘占空比在系統(tǒng)中

在焊盤上用于轉(zhuǎn)儲SDF的負載

I/O在定時感知GLS DDR驗證方面發(fā)揮著至關(guān)重要的作用。滿足焊盤輸入的時序,并且從焊盤的自由文件中提供的信息中轉(zhuǎn)儲I/O延遲。有時,從控制器到焊盤輸入的路徑被正確地滿足并平衡,但仍然可以看到故障。這可能是由于I/O引入的錯誤延遲,這些延遲位于主機控制器和外部DDR存儲器之間的路徑中。延遲實際上取決于施加到襯墊的負載。因此,在生成SDF時,需要注意必須應(yīng)用將在船上使用的正確和實際負載。如果不這樣做,將導(dǎo)致在SDF中產(chǎn)生非常悲觀的定時電弧,當(dāng)在GLS仿真中反標注時會產(chǎn)生虛假故障。這些問題很難調(diào)試,需要付出很多努力。

| 加載(以pf為單位) | 轉(zhuǎn)換時間(ns) | 計時弧(ns) | |

| 悲觀負載 | 35 | 2 | 2.8 |

| 實際負載 | 12 | 0.6 | 1.2 |

表3:悲觀負載v/s實際負載

輸出緩沖器使能(OBE)時序要求

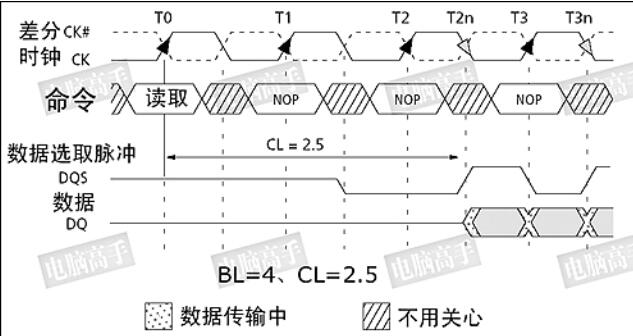

大多數(shù)DDR控制器設(shè)計都是為了驅(qū)動OBE(輸出緩沖器使能) DQ(數(shù)據(jù))和DQS(Strobe)焊盤本身可以用于寫入/讀取相同的焊盤。由于各種原因,OBE時序通常在路徑計時時被忽略,但在DDR的情況下這樣做會導(dǎo)致災(zāi)難性的結(jié)果。例如,在DDR協(xié)議的讀/寫期間,在READ/WRITE命令之后和DQS的第一個上升沿之前的DQS上的LOW狀態(tài)被稱為讀/寫前同步碼;同樣在最后一個數(shù)據(jù)輸入之后DQS上的LOW狀態(tài)元素稱為讀/寫后同步碼。前導(dǎo)碼部分為接收設(shè)備提供定時窗口,以便在選通信號上存在已知/有效電平時啟用其數(shù)據(jù)捕獲電路,從而避免對捕獲電路的錯誤觸發(fā)。 UIT。在前同步碼之后,選通脈沖將在數(shù)據(jù)突發(fā)的持續(xù)時間內(nèi)以與時鐘信號相同的頻率切換。在寫入期間對于該最小前導(dǎo)碼寬度存在一定的時序要求,例如DDR2為0.35Ck,DDR3為0.9Ck,應(yīng)該滿足。類似地,對寫后同步時序有要求。對于DDR2,這是0.4Ck-0.6Ck,對于DDR3,最小為0.3CK。如果DDR GLS遇到最常見的問題,則違反這些參數(shù)。

圖2:DDR前導(dǎo)碼和后同步碼

DDR焊盤的壓擺率設(shè)置:

焊盤的特點是不同的壓擺率決定了每單位時間輸出電壓的變化率。這些設(shè)置對RTL仿真沒有任何影響,因為沒有延遲,但在GLS仿真中,延遲進入畫面,進行適當(dāng)?shù)脑O(shè)置以避免任何不必要的調(diào)試變得至關(guān)重要。系統(tǒng)中不同焊盤的時序通常以最大轉(zhuǎn)換速率滿足,但可以根據(jù)各種參數(shù)而不同。一個這樣的例子是,對于像DDR這樣的協(xié)議的最大壓擺率,可以看到反射和干擾的問題。對于此參數(shù)的不同設(shè)置,打擊墊延遲變化太大。這些是根據(jù)最終將在驗證板和測試儀上使用的負載和電阻值決定的。我們必須確保使用正確的打擊墊設(shè)置運行我們的模擬,以便在預(yù)期結(jié)果和觀察結(jié)果之間沒有間隙。

下表包含推薦的SRE設(shè)置的數(shù)據(jù),用于不同的接口之一SoC的。

| Interface | SRE設(shè)置 |

| DDR | 10 |

| SDR | 10 |

| QuadSPI | 11 |

| ENET | 11 |

| MLB50 | 11 |

| SPI | 00 |

表4:SoC不同接口的推薦壓擺率設(shè)置

字符I/O中的問題:

這方面只是在GLS中而不是在RTL中可見的,如果從開始確保可以確保我們可以最小化迭代調(diào)試和反饋驗證和STA。為了給出背景,每個單元都有上升弧和下降弧所提到的延遲。任何單元的延遲都直接來自自由文件,其中包含PVT延遲的信息。電池的這些上升和下降時間可以彼此不同。但是像DDR這樣的協(xié)議對占空比,高時間,低時間等有嚴格的要求,這些都需要滿足協(xié)議的正確操作。在設(shè)計中,通常使用對稱緩沖器和單元,其具有幾乎相同的上升和下降時間,使得諸如CLK,DQS等的關(guān)鍵信號的路徑是平衡的。但有可能I/O的上升和下降時間之間存在巨大差異,因為表征問題會導(dǎo)致占空比失真,從而導(dǎo)致內(nèi)存端的違規(guī)。

圖3:上升 - 下降延遲弧的差異導(dǎo)致違反占空比要求

SDF延遲舍入是高速GLS驗證的殺手

測試平臺具有定義事件粒度的時間表模擬設(shè)計。在時間刻度語句中,第一個值是時間單位,第二個值是模擬的精度。對于高速電路,應(yīng)該非常仔細地定義時標精度。通常,時間刻度在測試平臺中定義為1ns/10ps,這意味著所有延遲將四舍五入到最接近的10ps。但是在DDR這樣的高速協(xié)議中,時序非常關(guān)鍵,邊距可以非常小(以皮秒為單位)。例如,如果數(shù)據(jù)路徑中有10個緩沖區(qū),每個緩沖區(qū)的延遲為26ps,如果時間刻度為1ns/10ps,則所有這些延遲將四舍五入為30ps,因此將在GLS中引入40ps的不準確度。這將導(dǎo)致GLS中的錯誤時序違規(guī)。必須更新模擬環(huán)境以具有適當(dāng)?shù)臅r間尺度以迎合這些問題。

應(yīng)解決內(nèi)存錯誤

通常,不同供應(yīng)商提供的模型可用于模擬。這些模型可以是Verilog模型或Denali模型。這些模型由Micron,Spansion,Macronix等內(nèi)存供應(yīng)商提供。出于模擬目的,Denali模型應(yīng)該是首選,因為這些模型對所有時序參數(shù)和協(xié)議進行了非常嚴格的檢查,并且還包括CK/DQS/DQ之間的抖動和偏斜因此非常接近將在板上使用的實際存儲器。如果在存儲器接口違反任何時序規(guī)范,則模型會標記錯誤。在RTL仿真中,沒有延遲,如果正確配置了時序參數(shù),則通常不會遇到這些錯誤。但是在圖像延遲的GLS模擬中,可能會發(fā)生一些參數(shù)被違反并且會拋出錯誤。應(yīng)仔細審查這些錯誤,并且必須予以解決。通常在寫入周期期間遇到問題,此時信號由控制器發(fā)出并到達存儲器。在讀取周期期間,信號由模型本身生成并到達控制器。為Denali存儲器提供了許多開關(guān),它們控制各種參數(shù),例如允許的差分偏移,將存儲器初始化為某個值,禁止從存儲器發(fā)送錯誤消息。應(yīng)該注意不要傳遞這樣的開關(guān),這可能會掩蓋任何錯誤。

-

DDR

+關(guān)注

關(guān)注

11文章

731瀏覽量

66371 -

PCB打樣

+關(guān)注

關(guān)注

17文章

2971瀏覽量

22349 -

華強PCB

+關(guān)注

關(guān)注

8文章

1831瀏覽量

28435 -

華強pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

43734

發(fā)布評論請先 登錄

Altera DDR2仿真

在同步電路中影響性能都有哪些方面呢?傳輸延遲,慣性延遲怎么形成的呢?映射到硬件上怎么形成這種現(xiàn)象呢?

DDR仿真的頻率提取

基于Cadence的DDRⅡ仿真設(shè)計

計算機仿真在多級放大電路設(shè)計中的應(yīng)用

DDR工作原理_DDR DQS信號的處理

DDR4技術(shù)有什么特點?如何采用ANSYS進行DDR4仿真?

如何利用ADS仿真軟件輔助進行DDR的電路仿真?

DDR仿真處理多級IO的慣性延遲問題

DDR仿真處理多級IO的慣性延遲問題

評論