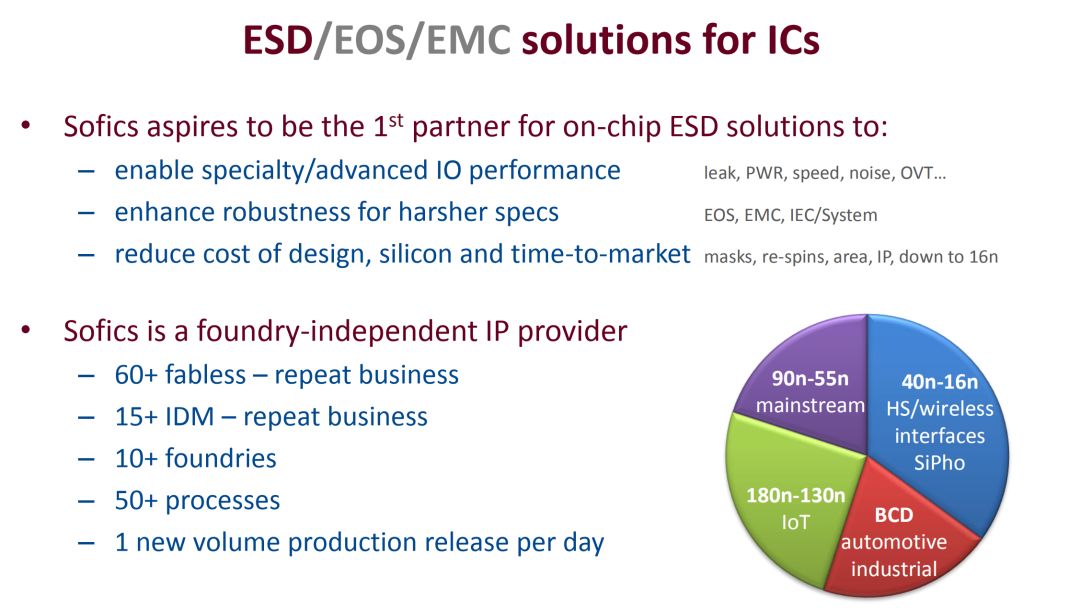

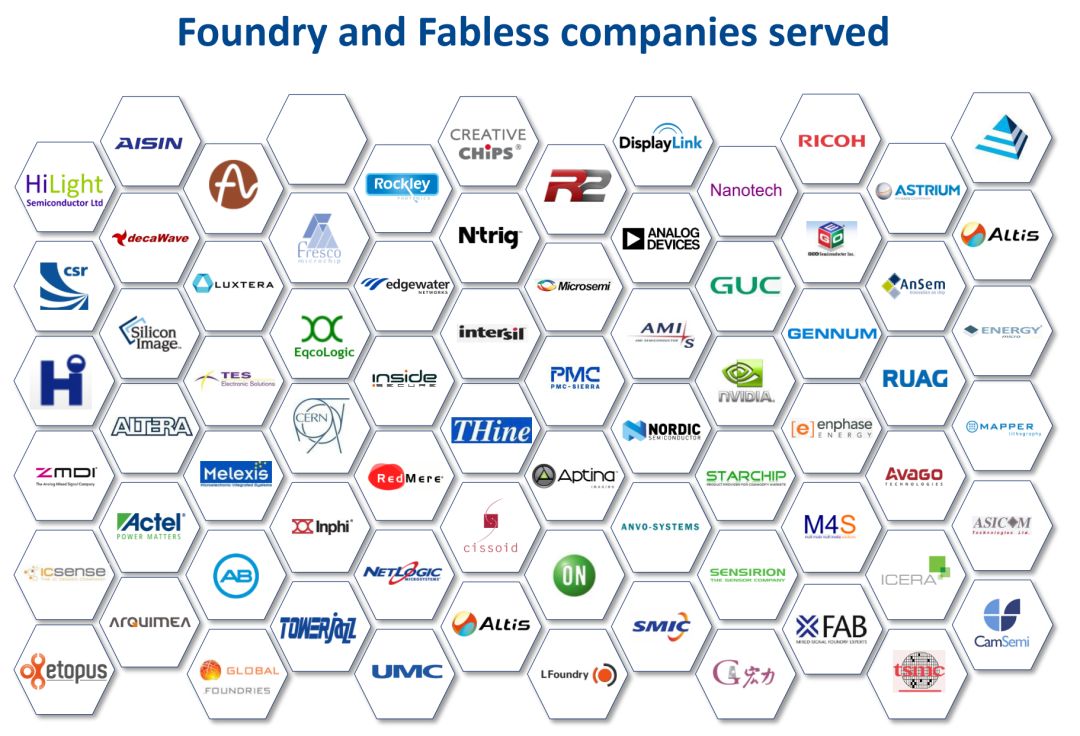

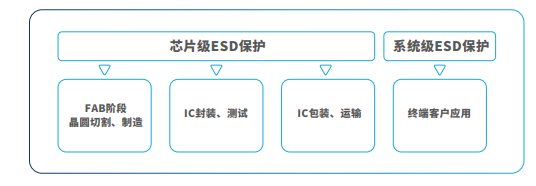

靜電防護(hù)是IC設(shè)計(jì)中不可缺失的一部分,一般來(lái)說(shuō),ESD在比較大的設(shè)計(jì)公司或者半導(dǎo)體廠(chǎng)都有自己的專(zhuān)屬部門(mén)。然而,隨著技術(shù)節(jié)點(diǎn)的推進(jìn),廣泛的應(yīng)用,ESD的問(wèn)題越來(lái)越變得防不勝防。為了和國(guó)內(nèi)設(shè)計(jì)公司和半導(dǎo)體廠(chǎng)實(shí)現(xiàn)雙贏,本篇文章介紹一家專(zhuān)注于on-chip ESD資源的比利時(shí)公司Sofics,希望能夠給大家參考,并且有機(jī)會(huì)合作,實(shí)現(xiàn)雙贏。 公司的On-chip ESD IP覆蓋了很多領(lǐng)域,比如 IOT, 硅光電,汽車(chē)電子,醫(yī)療器械,高速電路SERDES,防輻射, SOI,F(xiàn)INFET, 超低功耗, 3DIC等等。 我們服務(wù)過(guò)的合作伙伴也是超過(guò)了80多家,平均每天有一個(gè)量產(chǎn)的產(chǎn)品公布。從下面的圖中,大家可以看到,我們服務(wù)的客戶(hù)主要集中在歐美,日本等等,中國(guó)目前的客戶(hù)還是相對(duì)比較少。因此我們堅(jiān)信,隨著設(shè)計(jì)公司對(duì)產(chǎn)品的精益求精,國(guó)內(nèi)會(huì)有越來(lái)越多的公司需要定制的ESD,因?yàn)樗饺硕ㄖ频膐n-chip ESD 能給設(shè)計(jì)公司的產(chǎn)品,帶來(lái)更多附加價(jià)值。

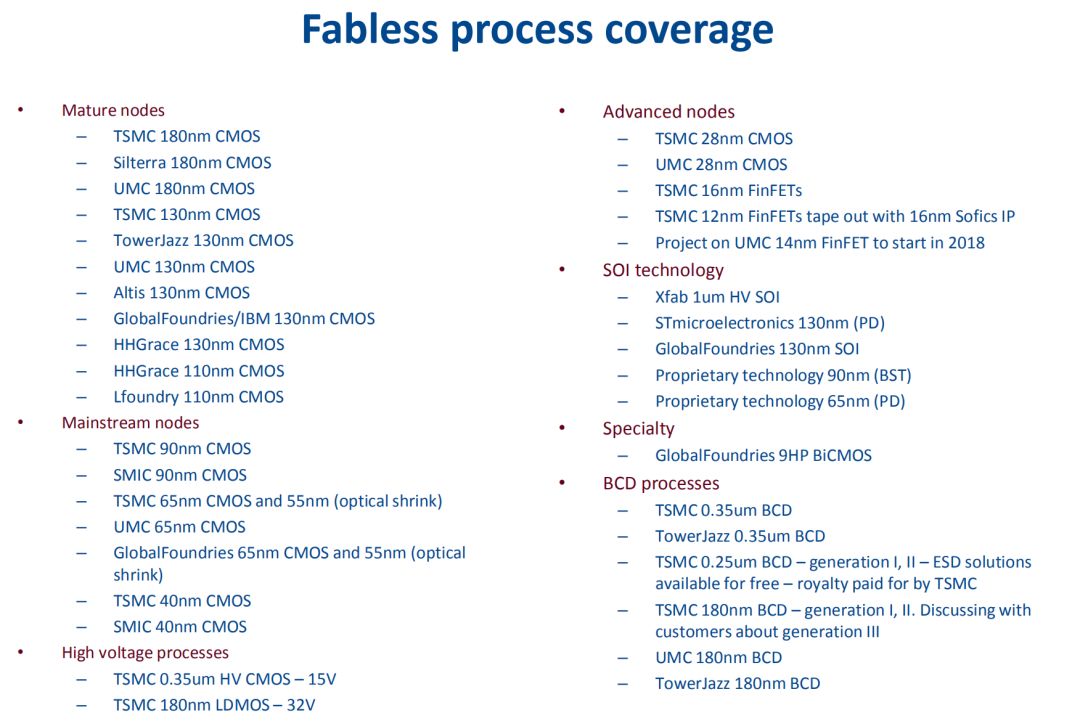

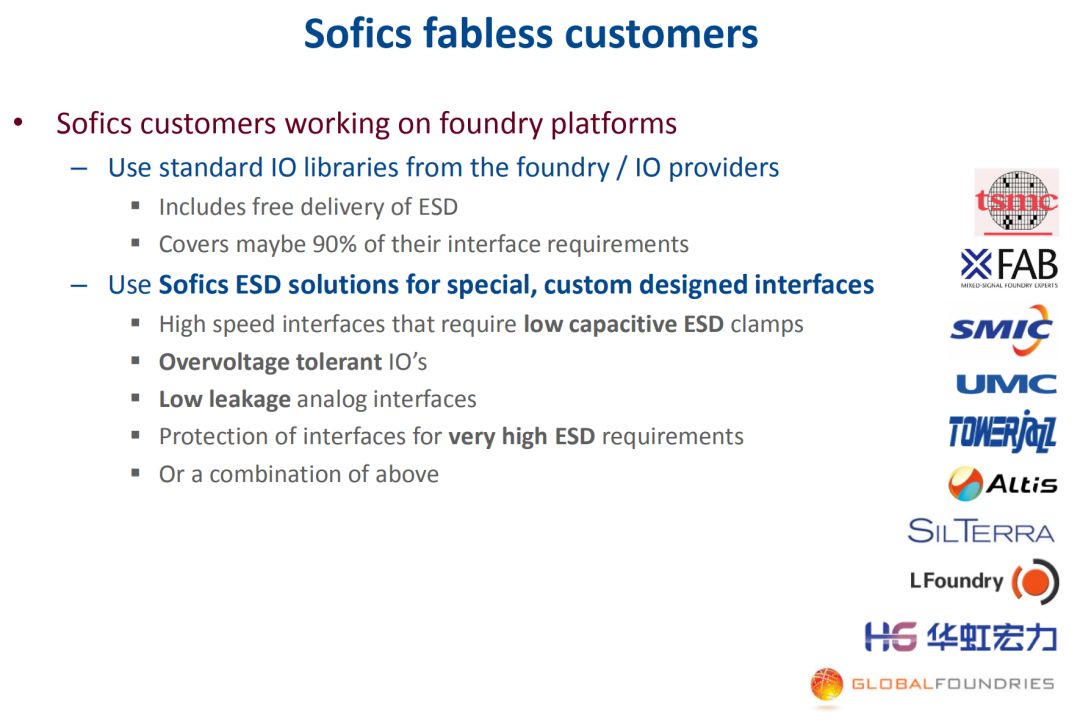

SOFICS的ESD私人定制解決方案,使特殊應(yīng)用變?yōu)榭赡埽a(chǎn)品性能得到提升,減少了產(chǎn)品的上市時(shí)間。至于具體的服務(wù)客戶(hù)和工藝節(jié)點(diǎn),可以參考下面兩張圖片。

因?yàn)閷?duì)于不同的產(chǎn)品應(yīng)用,接口,ESD 參數(shù)需求(HBM,CDM,MM)是千變?nèi)f化的。半導(dǎo)體廠(chǎng)能解決80-90%客戶(hù)的需求,但是對(duì)于高速界面,超高壓的ESD,IO的超電壓需求, 超低漏電的模擬界面等等,還是需要給出私人定制的方案。Sofics 的ESD解決方案,恰恰滿(mǎn)足了這部分客戶(hù)的私人定制需求。

很多朋友會(huì)疑問(wèn),采用SOFICS的ESD解決方案有什么優(yōu)點(diǎn)嗎,總的來(lái)說(shuō),因?yàn)橛泻芏囗?xiàng)目經(jīng)驗(yàn),成熟的解決方案,可以直接用到客戶(hù)的產(chǎn)品中,讓客戶(hù)減少產(chǎn)品設(shè)計(jì)周期,使其保持在新產(chǎn)品,高性能方面的優(yōu)勢(shì)。同時(shí),對(duì)于先進(jìn)節(jié)點(diǎn),公司的ESD也能在減少芯片面積,減少M(fèi)ASK等方面有獨(dú)特的技術(shù),幫助設(shè)計(jì)公司減少芯片費(fèi)用。

-

芯片

+關(guān)注

關(guān)注

459文章

52205瀏覽量

436457 -

靜電防護(hù)

+關(guān)注

關(guān)注

11文章

207瀏覽量

47837

發(fā)布評(píng)論請(qǐng)先 登錄

【干貨】ESD如何選型

ESD技術(shù)文檔:芯片級(jí)ESD與系統(tǒng)級(jí)ESD測(cè)試標(biāo)準(zhǔn)介紹和差異分析

概倫電子芯片級(jí)HBM靜電防護(hù)分析平臺(tái)ESDi介紹

Diodes公司PCIe 6.0時(shí)鐘緩沖器介紹

時(shí)源芯微 ESD問(wèn)題通用診斷分析方法:從現(xiàn)象定位到根治方案

ESD二極管不導(dǎo)電原因分析及解決方案

ESD對(duì)于電子器件的破壞機(jī)理分析

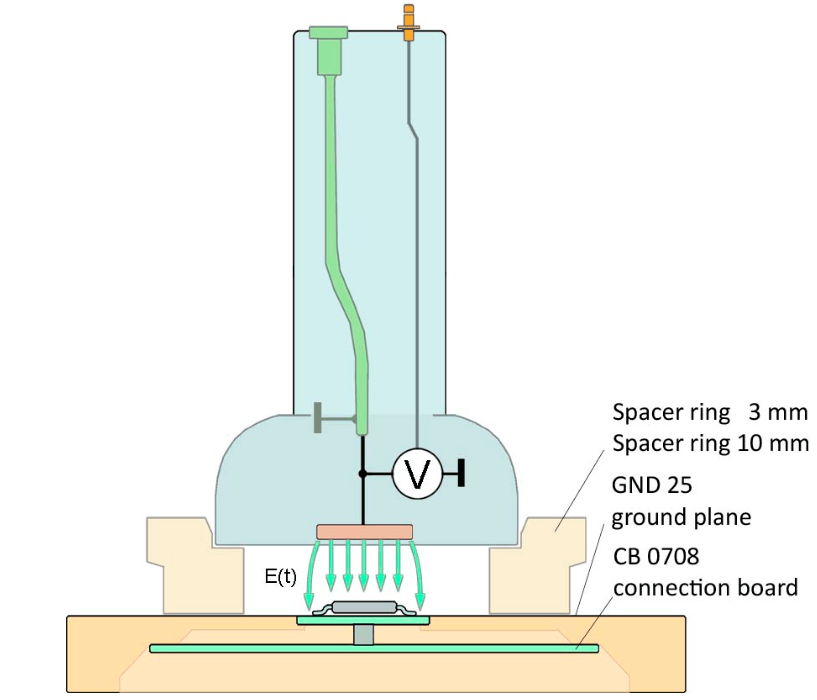

集成電路電磁兼容性及應(yīng)對(duì)措施相關(guān)分析(三)集成電路ESD 測(cè)試與分析

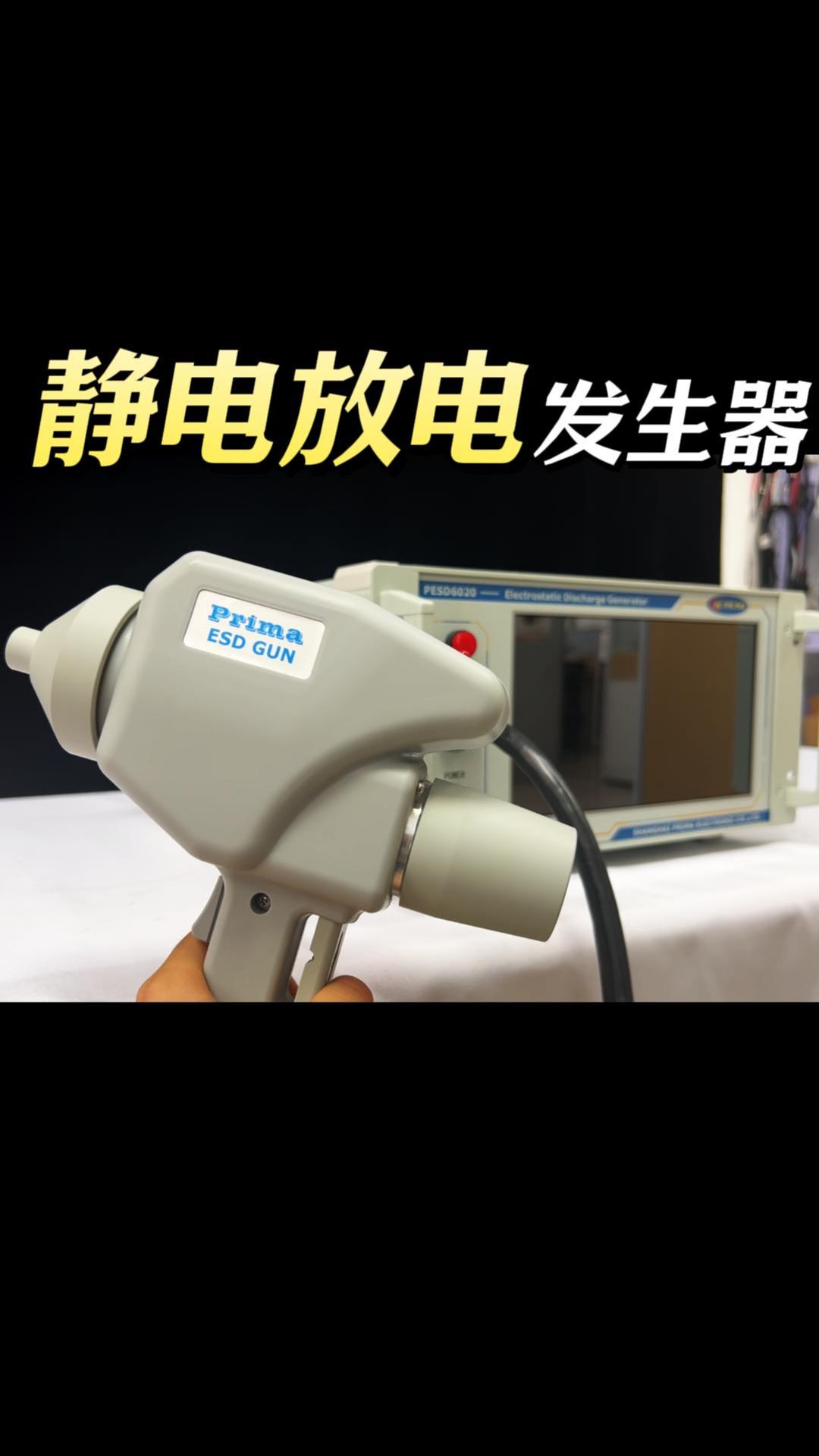

ESD測(cè)試|靜電放電抗擾度測(cè)試必備神器!#ESD測(cè)試 #靜電抗干擾測(cè)試 #電路知識(shí) #電子工程師

集成電路電磁兼容性及應(yīng)對(duì)措施相關(guān)分析(三)—集成電路ESD 測(cè)試與分析

ESD二極管特點(diǎn)優(yōu)勢(shì)有哪些?

求助,關(guān)于LM386芯片內(nèi)ESD保護(hù)電路設(shè)計(jì)和引腳分配情況求解

ESD保護(hù)電路POWERclamp原理

淺談半導(dǎo)體芯片失效分析Analysis of Semiconductor Chip Failure

關(guān)于On-chip ESD 資源的介紹和分析

關(guān)于On-chip ESD 資源的介紹和分析

評(píng)論