徐健?孫悅?孫鵬?胡文華

(華進(jìn)半導(dǎo)體封裝先導(dǎo)技術(shù)研發(fā)中心有限公司?荷蘭代爾夫特理工大學(xué))

摘要:

基于可靠性試驗所用的菊花鏈測試結(jié)構(gòu),對所設(shè)計的扇出型封裝結(jié)構(gòu)進(jìn)行了完整的菊花鏈芯片制造及后道組裝工藝制造,并對不同批次、不同工藝參數(shù)條件下的封裝樣品進(jìn)行電學(xué)測試表征、可靠性測試和失效樣品分析。通過菊花鏈設(shè)計結(jié)構(gòu)及超聲波掃描顯微鏡?(SAM)?等工具,對失效樣品進(jìn)行失效定位分析,并通過掃描電子顯微鏡?(SEM)?和能量色散 X 射線光譜儀(EDX)?等失效分析工具進(jìn)行失效分析。通過對不同批次的樣品進(jìn)行通斷電測試、可靠性預(yù)處理、可靠性試驗和失效分析,總結(jié)不同工藝方法對封裝整體結(jié)構(gòu)翹曲、芯片偏移、金屬層分層等失效模式的影響。為晶圓扇出型封裝的整體封裝結(jié)構(gòu)設(shè)計、工藝流程搭建、封裝材料選擇等工作提供了指導(dǎo)意見。

0?引言

扇出型封裝具有布線密度高、引腳間距小、封裝厚度薄和高頻傳輸損耗小等優(yōu)勢,近年來已逐漸發(fā)展成為封裝主流技術(shù),但是,扇出形封裝也面臨著很多技術(shù)問題亟待解決。

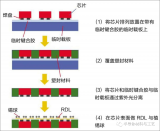

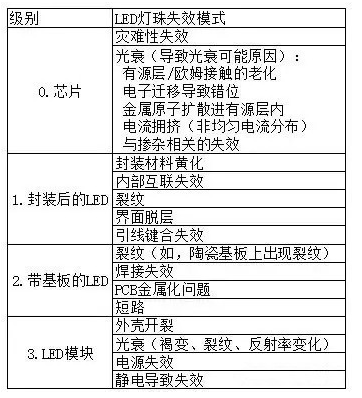

扇出型封裝技術(shù)主要面臨著兩項關(guān)鍵工藝挑戰(zhàn):?翹曲和芯片偏移。在扇出型封裝中,如果塑封工藝、重布線層?(redistribution layer,RDL)?工藝以及焊球工藝等任何一項工藝出現(xiàn)問題,都會導(dǎo)致整個芯片封裝發(fā)生物理或化學(xué)失效。

翹曲問題主要是由于不同材料間的熱膨脹系數(shù)不匹配造成的。芯片的保護(hù)材料以環(huán)氧樹脂類材料為主,在溫度變化時會發(fā)生膨脹和收縮,當(dāng)和其他材料熱膨脹系數(shù)失配時,接觸界面會發(fā)生分層或者斷裂等失效問題。對于翹曲問題,很多學(xué)者和機(jī)構(gòu)做過相關(guān)研究。一種方法是從工藝和結(jié)構(gòu)設(shè)計的角度出發(fā),重點是圍繞著環(huán)氧塑封料?(epoxy mold-ing compound,EMC)?的內(nèi)部結(jié)構(gòu)來研究的,通過在 EMC 內(nèi)部添加一些金屬支撐結(jié)構(gòu)來改善整體的應(yīng)力分布。如 Y. Lin 等人在 EMC 周圍通過印刷、電鍍和涂覆等工藝形成一層熱膨脹系數(shù)小于 EMC的材料,這種處理方式能夠通過具有較小的熱膨脹系數(shù)值的材料控制晶圓的翹曲程度,或者在 EMC之間通過金屬化工藝形成垂直的金屬結(jié)構(gòu)。金屬結(jié)構(gòu)能夠緩解 EMC 之間的應(yīng)力,減輕翹曲程度。另外,F(xiàn). Z. Hou 等人通過熱學(xué)和力學(xué)相結(jié)合的方法進(jìn)行仿真,從材料匹配、工藝優(yōu)化及設(shè)備調(diào)試方面解決這一問題。

芯片偏移是指在貼片、塑封等過程中,由于材料特性、設(shè)備精度、工藝參數(shù)等因素使芯片偏離原設(shè)計位置。在如何解決芯片偏移問題,有很多學(xué)者和機(jī)構(gòu)做過一些研究,Y. Lin 等人采用凹凸結(jié)構(gòu)的凸點制作,避免芯片偏移。而 C. Bishop 等人采用中間工藝表征的方法來預(yù)判斷芯片偏移。本文采用芯片貼片補(bǔ)償?shù)姆桨附鉀Q芯片偏移問題,并通過一系列的可靠性試驗進(jìn)行驗證,為高可靠性的扇出型封裝解決方案提供了設(shè)計指導(dǎo)。

1?扇出型封裝可靠性測試結(jié)構(gòu)設(shè)計

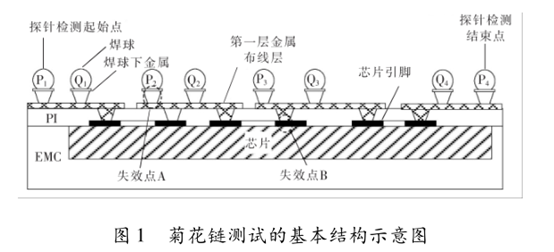

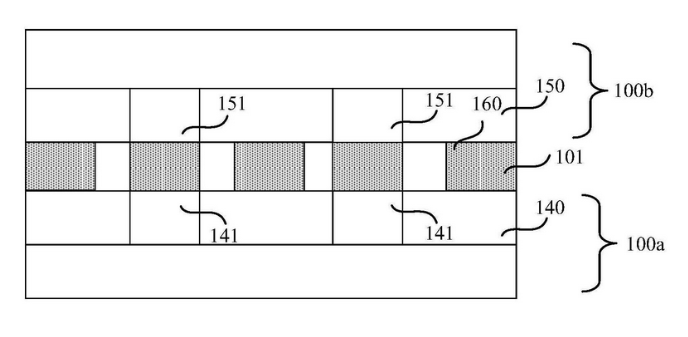

基于扇出型封裝的結(jié)構(gòu)特點以及菊花鏈的測試原理,針對扇出型封裝的可靠性測試設(shè)計了菊花鏈測試鏈路。設(shè)計該鏈路的目的是用來反映待測封裝產(chǎn)品的可靠性,如果鏈路發(fā)現(xiàn)失效,能夠依據(jù)測試結(jié)果對失效位置進(jìn)行定位,再進(jìn)行后續(xù)的失效分析。測試鏈路的基本結(jié)構(gòu)如圖 1 所示。其中,金屬層之間采用聚酰亞胺?(polyimide,PI)?材料。

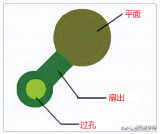

圖 1 中不同下標(biāo)的 P 點和 Q 點分別代表不同的焊球,直流電阻測試探針可以通過測量兩個焊球之間的阻值來判斷鏈路是否導(dǎo)通。根據(jù)對扇出型封裝結(jié)構(gòu)的分析,A 點和 B 點是代表結(jié)構(gòu)中兩類可能失效的位置。其中,A 點指的是包括焊球與沉積凸點下金屬層?(under ball metal,UBM)?連接位置以及 UBM 與第一層?RDL 連接位置,B 點指的是芯片的引腳與引腳上的過孔連接的位置。

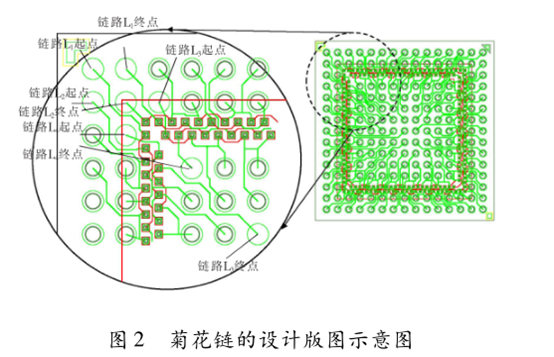

基于菊花鏈可靠性測試原理,設(shè)計的菊花鏈測試結(jié)構(gòu)的版圖如圖 2 所示,其中扇出型封裝尺寸為8 mm × 8 mm,芯片尺寸為 6 mm ×6 mm。

對應(yīng)的測試鏈路信息如圖 2 所示。版圖中有 4條測試鏈路,即 L 1 ,L 2 ,L 3 和 L 4 ,一條鏈路的兩個端子由起點焊球和終點焊球構(gòu)成。鏈路上任何一處互連結(jié)構(gòu)的橫截面積、電阻率以及互連線的長度發(fā)生變化,都會引起電阻值的變化,但變化的幅度有所不同,因此通過 4 條鏈路的電阻值?R L 1 ,R L 2 ,R L 3 和?R L 4 的變化情況能夠反映封裝可靠性。

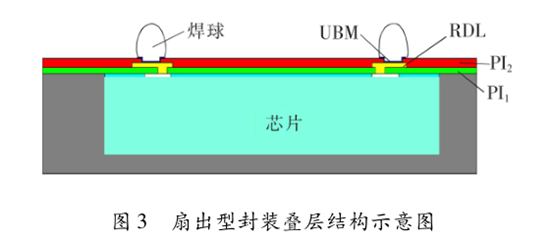

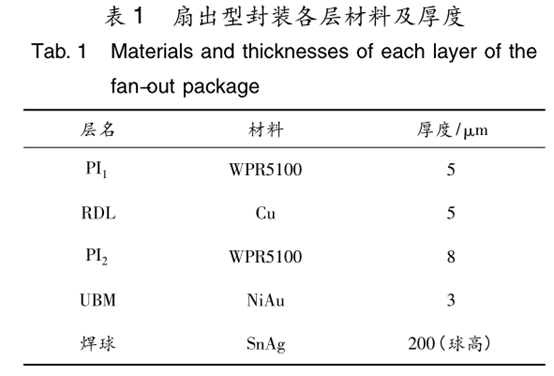

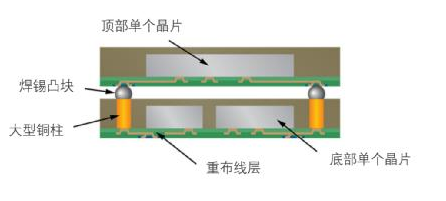

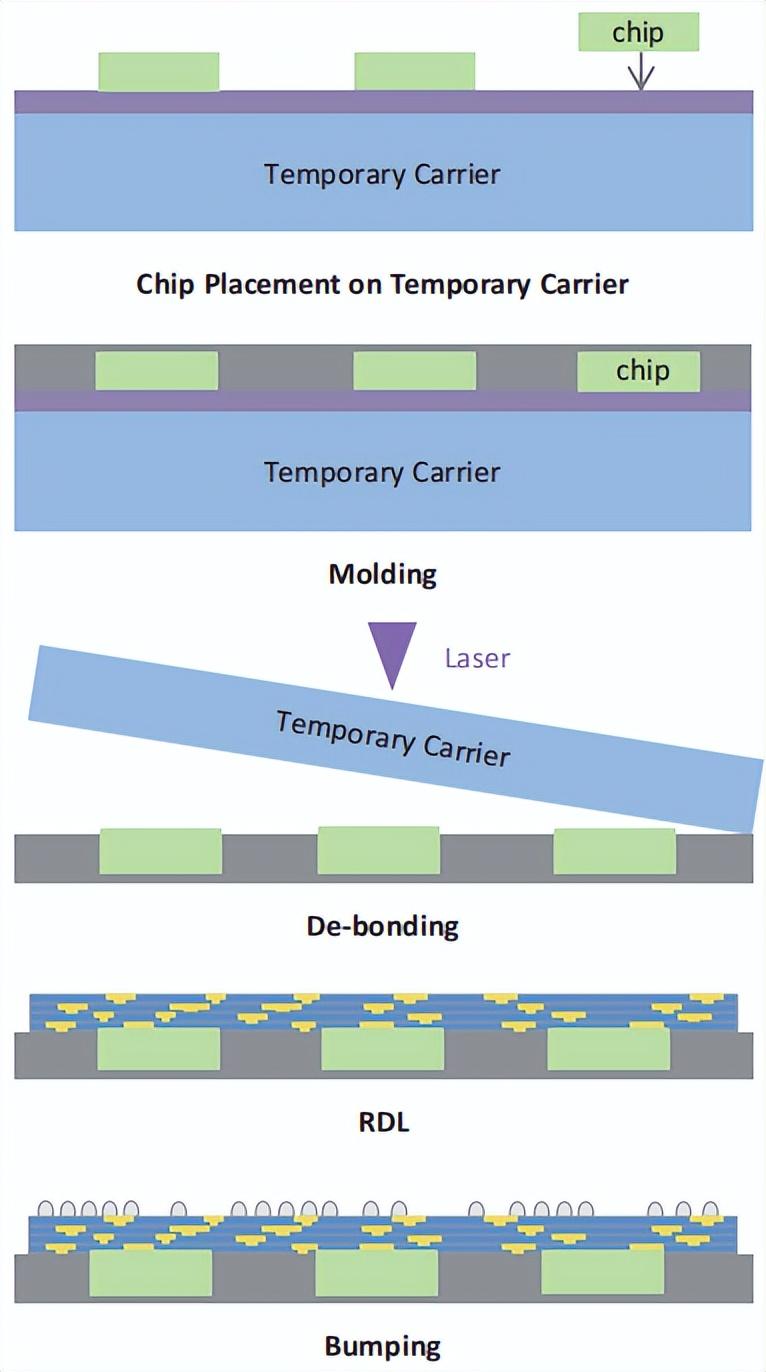

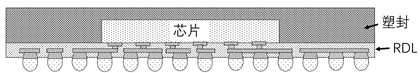

扇出封裝采用傳統(tǒng)嵌入式晶圓級球柵陣列(embedded wafer level BGA,EWLB)?封裝方案,采用單層金屬布線,封裝層疊結(jié)構(gòu)如圖 3,各層的厚度信息如表 1 所示。

2?第一批次芯片可靠性驗證及失效分析

菊花鏈的失效值規(guī)定依照標(biāo)準(zhǔn)各有不同,暫無統(tǒng)一標(biāo)準(zhǔn)。但是有兩點標(biāo)準(zhǔn)是明確的,一是隨著電路阻值增大,產(chǎn)品越接近失效。二是當(dāng)菊花鏈斷開時,電阻值趨向無窮大,必然導(dǎo)致失效。

由于行業(yè)缺乏評判標(biāo)準(zhǔn),本文采用功能公司內(nèi)部的標(biāo)準(zhǔn)進(jìn)行失效評判,將通斷測試的失效標(biāo)準(zhǔn)規(guī)定為 15 Ω。試驗準(zhǔn)備了兩個批次的菊花鏈芯片,其中,第一批次芯片為 850?顆,采用開/短路的測試方法判斷可靠性。在對第一批次芯片失效問題改善的基礎(chǔ)上,進(jìn)行第二批次芯片加工制造,取 240顆芯片,以鏈路的實際阻值大小是否超過 15 Ω?為標(biāo)準(zhǔn)判斷失效情況。

2. 1?第一批次芯片的電測試驗

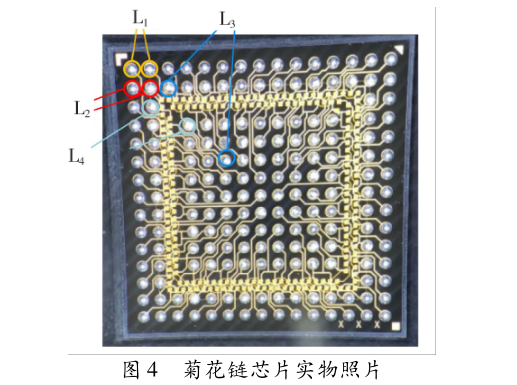

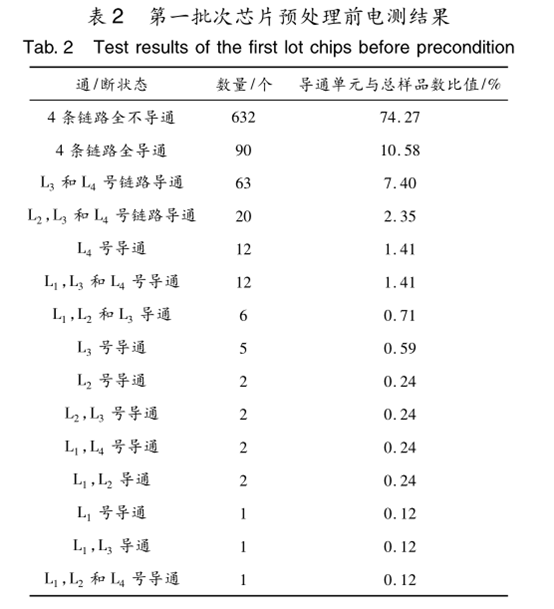

第一批次芯片的電測試驗以通斷測試為標(biāo)準(zhǔn)。最終封裝實物及鏈路端口如圖 4 所示。本方案采用 JEDEC MSL3 的預(yù)處理標(biāo)準(zhǔn)。在預(yù)處理試驗之前進(jìn)行第一次電性測量,預(yù)處理試驗后重新進(jìn)行第二次測量,分析兩次測試之間的差異,用以評判封裝的可靠性。采用萬用表的蜂鳴檔作為測試設(shè)備。表 2 統(tǒng)計了第一次電測的結(jié)果。

由測試結(jié)果可以看出,由于封裝翹曲及芯片偏移的因素,L 1 ~ L 4 的 4 條鏈路完全導(dǎo)通的芯片數(shù)量較少,只占總數(shù)的 10%。但是 L 4 號鏈路導(dǎo)通的所有芯片的數(shù)量為 200?顆,因此決定以 4 條鏈路中的 L 4 鏈路的通斷,作為判斷芯片電測是否通過的依據(jù)。

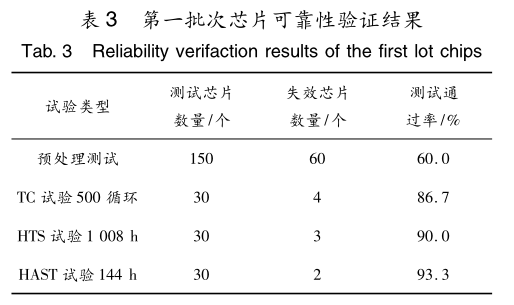

選擇 150?顆已知 L 4 鏈路導(dǎo)通的芯片進(jìn)行 MSL3預(yù)處理試驗后,進(jìn)行第 2 次電測。第 2 電測后 L 4鏈路導(dǎo)通的芯片為 90?顆,有 60?顆失效,接著進(jìn)行預(yù)處理試驗。經(jīng)過預(yù)處理測試后,將未失效的 90顆芯片分三類,每類 30?顆,分別進(jìn)行了溫度循環(huán)(TC)?試驗 500?循環(huán),高溫存儲?( HTS)?試驗1 008 h和高壓加速壽命?(HAST)?試驗144 h 試驗。測試結(jié)果如表 3 所示。

從表 3 可以看到,測試通過率高低與不同試驗項目所施加的應(yīng)力大小有直接關(guān)系,試驗應(yīng)力越大,失效芯片比例越大,測試通過率就越低。

2. 2?第一批次芯片的失效分析

基于菊花鏈定位失效位置的原理,對電測失效芯片的失效位置進(jìn)行定位以及相應(yīng)的失效分析。在本次試驗中,主要是對失效的截面和表面進(jìn)行觀察,以及對關(guān)鍵部分進(jìn)行能譜分析?(EDS)。

2. 2. 1?預(yù)處理試驗后的失效分析

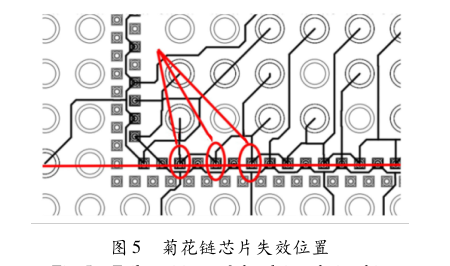

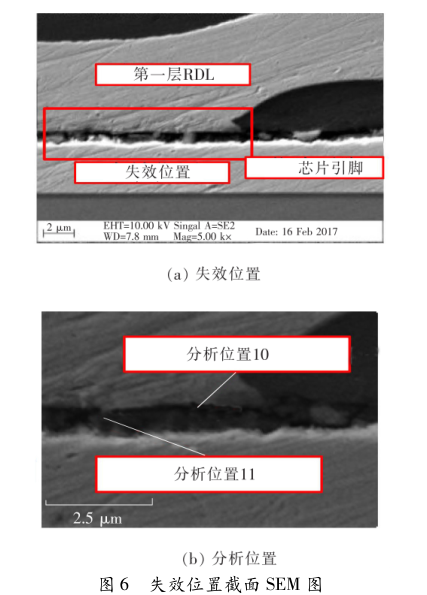

預(yù)處理試驗后,確定芯片的失效位置如圖 5,失效位置的截面掃描電子顯微鏡?(SEM)?結(jié)果如圖 6。根據(jù)觀察到的截面 SEM 圖可知,由于芯片引腳和第一層互連線之間存在類似斷裂的情況,導(dǎo)致導(dǎo)體之間產(chǎn)生斷層,引起鏈路斷路。為了確定失效原因,對斷裂層進(jìn)行 EDS 能譜分析。圖 7 是采用能譜儀對斷裂部分的分析結(jié)果。能譜分析結(jié)果顯示,位置 10?和位置 11 的主要成分是碳元素,因此,確定在RDL 和芯片引腳之間產(chǎn)生了斷裂部分。根據(jù)所采用的扇出型封裝流程,初步判斷為 PI 層在進(jìn)行完開口處理后,金屬表面任然留有殘余 PI材料。

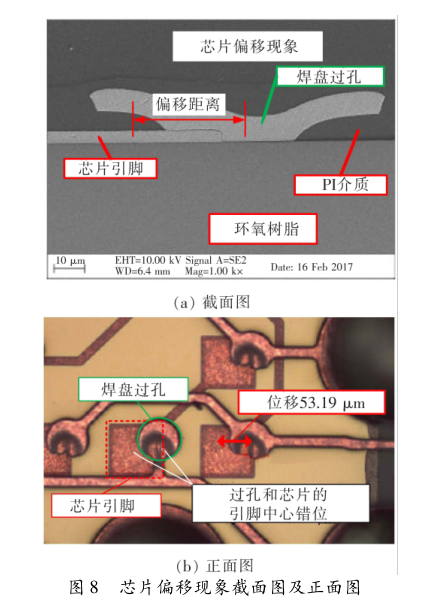

在第一批次試驗中,還出現(xiàn)了芯片偏移問題,芯片偏移的截面圖和正面圖如圖 8 所示。由圖 8(a)?和?(b)?中可以看出,正常沒有芯片偏移的情況時,過孔的位置是按照預(yù)先設(shè)計的晶圓版圖布置,芯片引腳的中心是和過孔的中心重合的。由于晶圓封裝各個材料的熱膨脹系數(shù)不匹配,產(chǎn)生材料漲縮,發(fā)生翹曲,從而影響芯片位置。初步判斷為貼片精度與材料漲縮所影響,后期擬通過在貼片階段預(yù)補(bǔ)償?shù)姆绞剑畲蠡販p少芯片位移對RDL 的影響。

2. 2. 2?第一批次可靠性試驗的失效分析

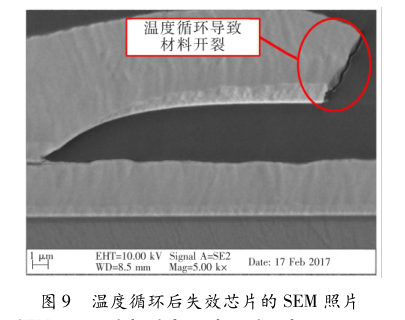

經(jīng)過 TC,HTS 和 HAST 可靠性試驗后,用SEM 對失效芯片進(jìn)行分析,其開裂形貌照片如圖 9所示。

從圖 9 可以看出,介質(zhì)和導(dǎo)體之間的連接界面雖然存在分層,但是并沒有導(dǎo)致導(dǎo)體斷裂,這是由于溫度循環(huán)導(dǎo)致材料在承受高/低溫沖擊時產(chǎn)生膨脹和收縮,從而導(dǎo)致材料間界面開裂。因此為了能夠抵抗引起界面分層的應(yīng)力,需要提高界面材料的韌度和粘接強(qiáng)度。

在對第一批次的失效分析中認(rèn)為導(dǎo)致鏈路斷開的主要原因是芯片位移和導(dǎo)體斷層。在下一批次的封裝會進(jìn)行相應(yīng)的工藝改善。

3?第二批次芯片可靠性驗證及失效分析

3. 1?第二批次芯片的電測試驗

經(jīng)過第一批次的可靠性測試和失效分析,針對失效問題進(jìn)行了物理氣相沉積?(PVD)、濺射、芯片貼片等工藝改善,進(jìn)行了第二次封裝流片。為了更準(zhǔn)確地反映該結(jié)構(gòu)的可靠性問題,第二次的電性測試檢測了 4 條鏈路的實際阻值大小,采用探針臺配合萬用表的方式進(jìn)行測試。

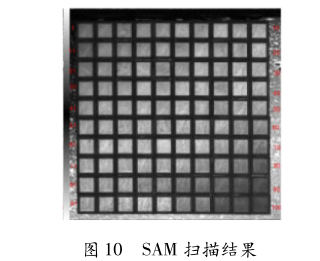

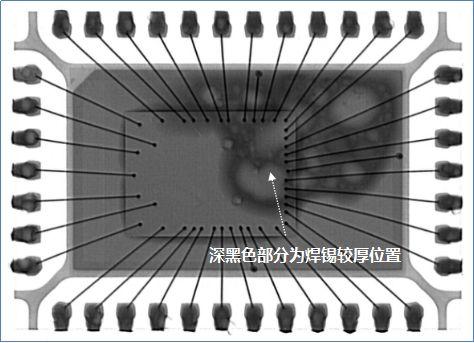

在第二批次的芯片中選擇 242 顆芯片進(jìn)行可靠性試驗。首先進(jìn)行無損超聲波掃描,掃描結(jié)果如圖10?所示。

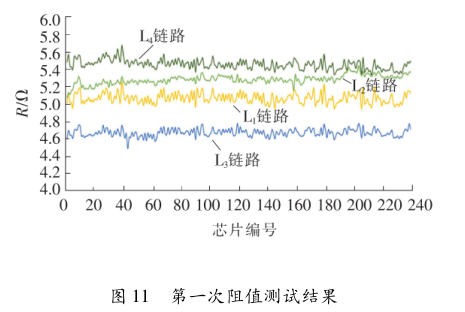

SAM 掃描結(jié)果顯示未發(fā)現(xiàn)芯片分層。在 MSL3預(yù)處理試驗之前,首先對 4 條鏈路的初始阻值進(jìn)行測試,測試結(jié)果如圖 11 所示。

由圖 11 中的結(jié)果顯示,L 1 鏈路的平均阻值約為 5. 07 Ω,L 2 鏈路的平均阻值約為 5. 2 Ω,L 3 鏈路的平均阻值約為 4. 6 Ω,L 4 鏈路的平均阻值約為5. 4 Ω。

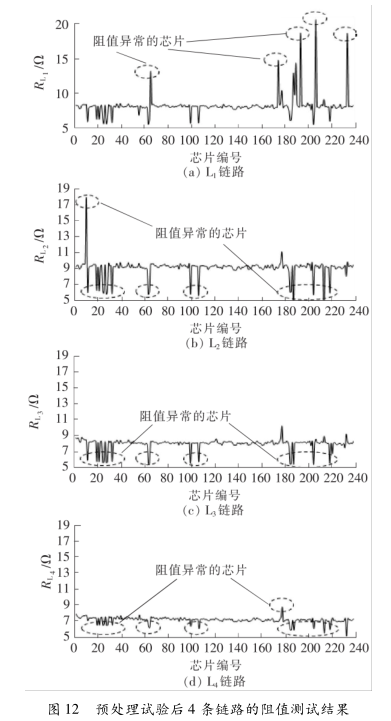

隨后對這 242 顆芯片進(jìn)行預(yù)處理測試,測試后芯片的 4 條鏈路的電阻值如圖 12 所示。

根據(jù)15 Ω?的阻值失效標(biāo)準(zhǔn),經(jīng)過統(tǒng)計有33 顆阻值異常的芯片,其中有 6 顆芯片的阻值超過了15 Ω,判斷為失效。將這些阻值異常的芯片標(biāo)記后進(jìn)行相應(yīng)的失效分析。經(jīng)過 MSL3 預(yù)處理后的芯片 4 條鏈路阻值的平均值分別為 8. 06,9. 3,8. 24和 7. 3 Ω。

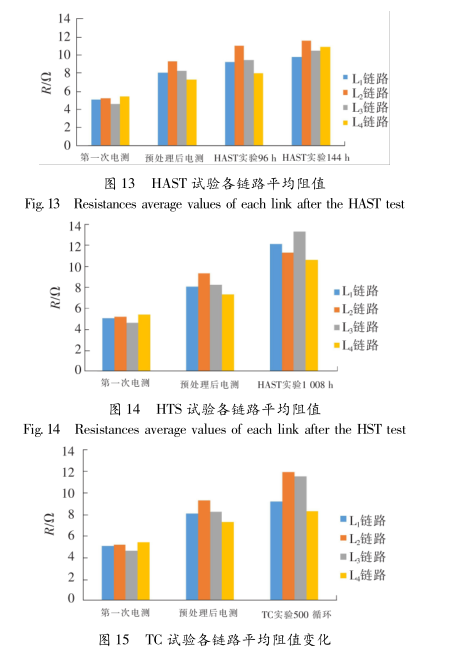

經(jīng)過預(yù)處理測試后,分 3 組進(jìn)行可靠性試驗:第一組選擇 77 顆阻值正常的芯片進(jìn)行 96 h,144 h的加速老化試驗;?第二組選擇 46 顆阻值正常的芯片進(jìn)行1 008 h 的高溫存儲試驗;?第三組選擇77 顆芯片進(jìn)行 500?個循環(huán)的溫度循環(huán)試驗。4 條鏈路在每次試驗前后平均阻值的對比結(jié)果如圖 13 ~ 15所示。

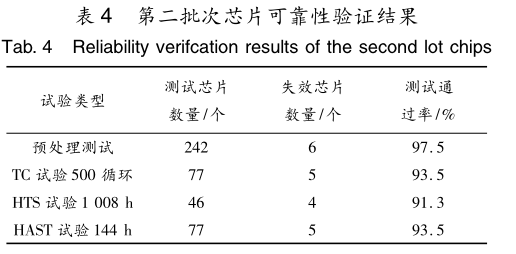

根據(jù)鏈路平均阻值的數(shù)據(jù)分析可知,每條鏈路經(jīng)過預(yù)處理試驗后,鏈路阻值都會有一定程度的上升。對于試驗結(jié)果的分析如表 4 所示。

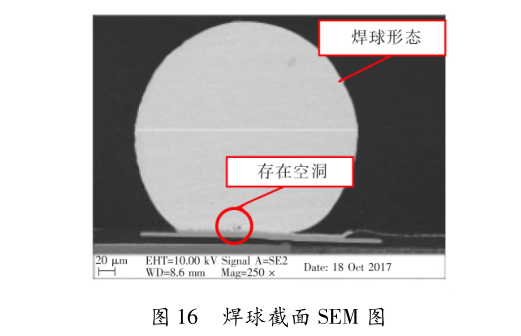

3. 2?第二批次芯片的失效分析

針對第二批次芯片封裝的失效分析,主要關(guān)注阻值變化的原因和封裝結(jié)構(gòu)是否有缺陷。為了對比試驗前后的阻值變化,首先在經(jīng)過預(yù)處理試驗之前,使用 SEM 設(shè)備對阻值正常的芯片的 L 2 鏈路的兩個端子的焊球進(jìn)行截面分析,SEM 照片如圖16 所示。

通過對焊球的截面分析發(fā)現(xiàn)兩個問題:?在第一批次中存在的芯片偏移問題已經(jīng)解決,這是通過在貼片階段對芯片偏移進(jìn)行反向補(bǔ)償?shù)姆椒ǎ瑢に囘M(jìn)行了優(yōu)化,試驗結(jié)果有明顯改善;?焊球和 UBM結(jié)合的金屬間化合物存在空洞,而且焊球并未完全塌落,由于空洞的位置在金屬間化合物?(IMC)?的晶界處,并且從焊球的形態(tài)上觀察,考慮是由于助焊劑覆蓋不均勻,導(dǎo)致回流過程中潤濕性不充分,從而導(dǎo)致空洞的產(chǎn)生。

3. 2. 1?第二批預(yù)處理試驗后的失效風(fēng)險

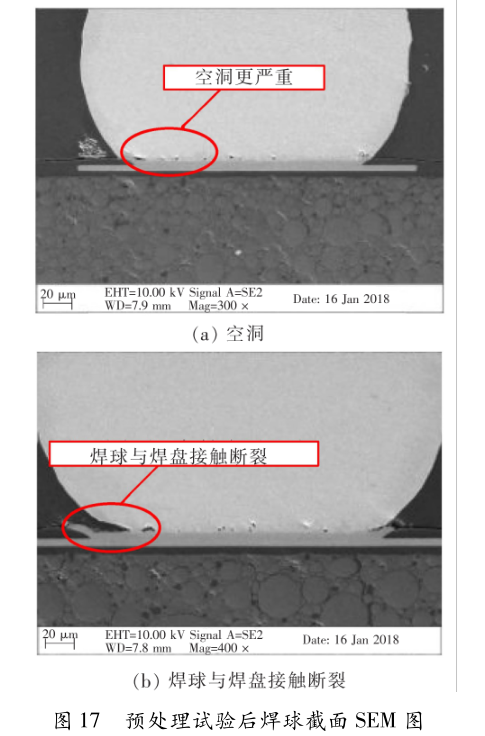

經(jīng)過預(yù)處理的試驗后,從阻值測試結(jié)果可以看出,所有鏈路的平均阻值都變大。繼續(xù)對經(jīng)過預(yù)處理試驗的芯片進(jìn)行截面分析,結(jié)果如圖 17 所示。

由圖 17 可以看出,經(jīng)過預(yù)處理試驗后空洞出現(xiàn)得更多,并且焊球和焊盤接觸的部分產(chǎn)生斷裂。根據(jù)空洞產(chǎn)生的原理可知,在經(jīng)歷預(yù)處理?(預(yù)處理含 3 次回流)?試驗的高溫及回流焊測試后,焊料內(nèi)晶粒長大和粗化。焊料的塑性變形導(dǎo)致在焊料與焊盤之間的晶界處產(chǎn)生微小空洞。之后,隨著熱循環(huán)的進(jìn)行,空洞擴(kuò)大并且增多,形成空洞的聚集,直至產(chǎn)生微裂紋,并且隨著微裂紋的增多產(chǎn)生宏觀裂紋,從而導(dǎo)致界面的空洞變大,對阻值的影響更大。

3. 2. 2?第二批次可靠性試驗的失效分析

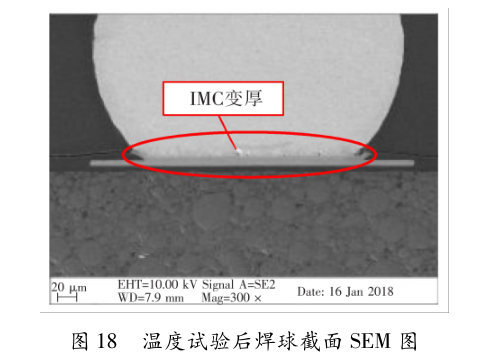

經(jīng)過 HAST 試驗 144 h 后,4 條鏈路的平均阻值上升了 5 Ω?左右。經(jīng)過 TC 試驗 500?個循環(huán)后,鏈路的平均阻值上升了約 5 Ω。經(jīng)過 HTS 試驗1 008 h后,阻值也上升了 5 Ω?左右。為了分析導(dǎo)致阻值上升的原因,對 TC 和 HTS 試驗后的焊球結(jié)構(gòu)和分層情況進(jìn)行觀察,觀察到的結(jié)果如圖 18所示。

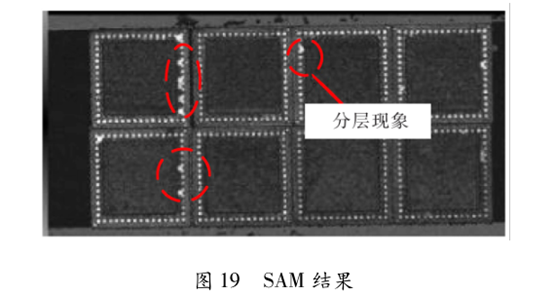

由圖 18 可以看出,在經(jīng)過溫度試驗后,觀察發(fā)現(xiàn)在焊盤和焊球之間 IMC 明顯變厚,因此導(dǎo)致阻值變大。經(jīng)過超聲波掃描后,發(fā)現(xiàn)有幾顆芯片產(chǎn)生了分層,觀察結(jié)果的超聲波掃描顯微鏡?(SAM)如圖 19。

從超聲波掃描結(jié)果可以看出,經(jīng)過溫度試驗后,從芯片正面看進(jìn)去,第二層出現(xiàn)分層,分層位置在 PI 和 EMC 上。雖然經(jīng)過 500?個循環(huán)后,在 PI和 EMC 之間分層并沒有影響到鏈路的通斷,但后續(xù)如果繼續(xù)溫度循環(huán)試驗,則有可能會造成更加嚴(yán)重的分層現(xiàn)象,引起RDL 的斷裂。

對比兩批次可靠性電測試驗結(jié)果,以鏈路阻值超過 15 Ω?作為判斷芯片失效的條件,對兩個批次的可靠性驗證結(jié)果分析如下:?經(jīng)過對芯片偏移和導(dǎo)體斷層的工藝問題改善后,預(yù)處理試驗的電測通過率明顯提高,從 60%提高到了 97. 5%; TC 試驗500?個循環(huán)后,通過率從 86. 7%?提高到了 93. 5%,有一些改善。HTS 試驗 1 008 h 以后,通過率從90. 0%提高到了 91. 3%,改善不明顯,HAST 試驗的通過率 93. 3%提高到了 93. 5%,幾乎沒有改善,這是由于焊球空洞和 IMC 結(jié)合不穩(wěn)定等問題,在第二批次工藝仍然存在引起的。

4?結(jié)論

本文主要設(shè)計了用于封裝可靠性測試的菊花鏈結(jié)構(gòu),研究了基于扇出型封裝結(jié)構(gòu)的芯片失效位置定位方法,針對芯片偏移、RDL 分層兩個主要失效問題進(jìn)行了相應(yīng)的工藝改善。經(jīng)過可靠性試驗對封裝的工藝進(jìn)行了驗證,通過菊花鏈的通斷測試和阻值變化,對失效位置定位進(jìn)行了相應(yīng)的失效分析。在第二次封裝流片中通過部分工藝上的改善,提高了封裝的可靠性。在預(yù)處理試驗后,芯片的通過率由 60%?提高到了 97. 5%,可靠性有了明顯改善。

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論