控制門(mén)電路的通斷。 可以具備這三種狀態(tài)的器件就叫做三態(tài)(門(mén),總線(xiàn),......).舉例來(lái)說(shuō):內(nèi)存里面的一個(gè)存儲(chǔ)單元,讀寫(xiě)控制線(xiàn)處于低電位時(shí),存儲(chǔ)單元被打開(kāi),可以向里面寫(xiě)入;當(dāng)處于高電位時(shí),可以讀出,但是

2008-05-26 13:01:37

三態(tài)輸出的緩沖器有哪些用途? 三態(tài)輸出緩沖器是一種電子元件,其主要作用是將一個(gè)輸入信號(hào)轉(zhuǎn)換成一個(gè)可以控制多個(gè)輸出設(shè)備的信號(hào)。這種緩沖器可以被用于一系列的應(yīng)用,包括數(shù)碼電路、計(jì)算機(jī)、消費(fèi)電子設(shè)備、通信

2023-09-21 15:55:36 389

389 本文著重探討 HDIO OBUFT 和 IOBUF 用例。如果含三態(tài)控制 (OBUFT/IOBUF) 的 HDIO 輸出緩沖器的上電電壓為 3.3 V 或 2.5 V 并且 Data(數(shù)據(jù))控制信號(hào)與 Tristate(三態(tài))控制信號(hào)的切換時(shí)間彼此相近,則可能會(huì)受到三態(tài)數(shù)據(jù)爭(zhēng)用條件的影響。

2023-07-12 09:50:32 213

213

八進(jìn)制透明鎖存器(三態(tài));八進(jìn)制 D 觸發(fā)器(三態(tài))-74F373_374

2023-03-03 20:05:16 0

0 16 位注冊(cè)驅(qū)動(dòng)器,具有反向寄存器啟用和動(dòng)態(tài)控制輸出;三態(tài)-74AVC16334A

2023-02-21 18:51:10 0

0 18 位注冊(cè)驅(qū)動(dòng)器,具有反向寄存器啟用和動(dòng)態(tài)控制輸出;三態(tài)-74AVC16834A

2023-02-21 18:50:57 0

0 具有動(dòng)態(tài)控制輸出的 18 位注冊(cè)驅(qū)動(dòng)程序;三態(tài)-74AVC16835A

2023-02-21 18:40:05 0

0 具有反向寄存器使能和動(dòng)態(tài)控制輸出的 20 位寄存驅(qū)動(dòng)程序;三態(tài)-74AVC16836A

2023-02-21 18:39:50 0

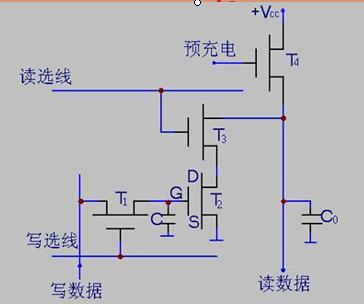

0 在當(dāng)前計(jì)算密集的高性能系統(tǒng)中,動(dòng)態(tài)隨機(jī)存儲(chǔ)器(DRAM)和嵌入式動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器(embedded-DRAM,eDRAM)是主要的動(dòng)態(tài)快速讀/寫(xiě)存儲(chǔ)器。先進(jìn)的 DRAM 存儲(chǔ)單元有兩種,即深溝

2023-02-08 10:14:57 3874

3874 在芯片設(shè)計(jì)時(shí),通常需要用到各種類(lèi)型的存儲(chǔ)單元,用以臨時(shí)或者永久地存儲(chǔ)數(shù)據(jù)。根據(jù)應(yīng)用場(chǎng)合的不同,所用到的存儲(chǔ)單元也不同。本文對(duì)常見(jiàn)的幾個(gè)存儲(chǔ)單元進(jìn)行了介紹,并簡(jiǎn)述了其工作原理和特點(diǎn)。需要特別

2022-12-02 17:36:24 1465

1465

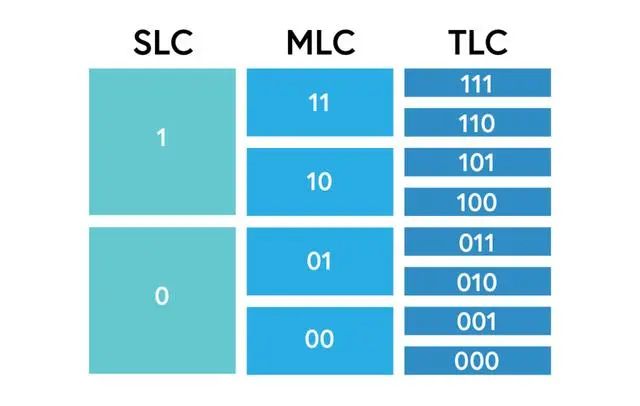

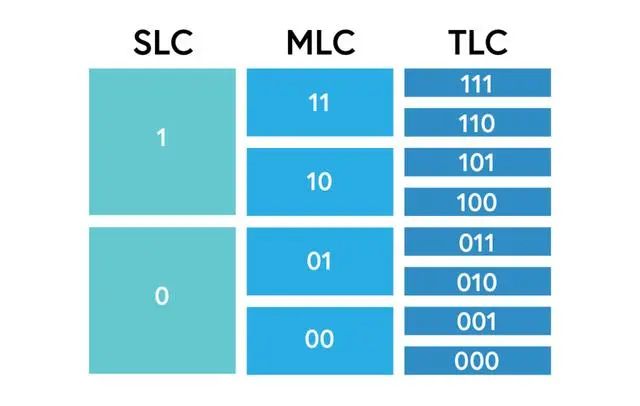

就基本的 SSD 存儲(chǔ)單元而言,有 SLC、MLC、TLC 和 QLC。其中,TLC 是最受歡迎的,不過(guò),QLC 最終將取代它們。在 I/O 方面,有 SATA 和 NVMe。

2022-08-26 16:41:35 2959

2959

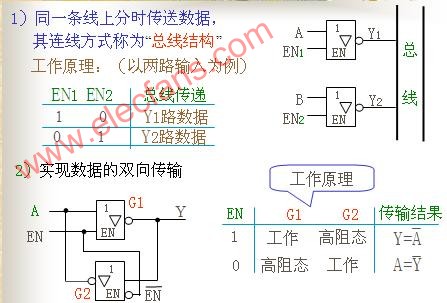

閃速存儲(chǔ)器(Flash Memory)又稱(chēng)閃存(Flash),是一種非易失性存儲(chǔ)器,用存儲(chǔ)單元閾值的高低表示數(shù)據(jù)。浮柵(Floating Gate )場(chǎng)效應(yīng)管(見(jiàn)圖5-80)是Flash存儲(chǔ)單元采用的主要技術(shù)。

2022-08-08 15:46:00 802

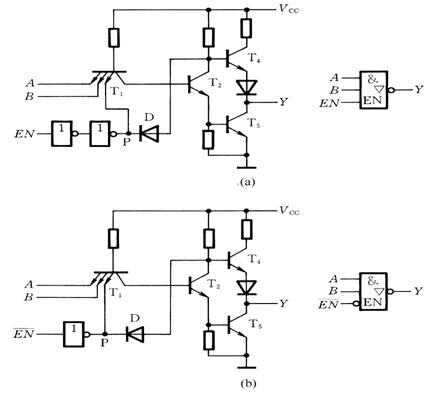

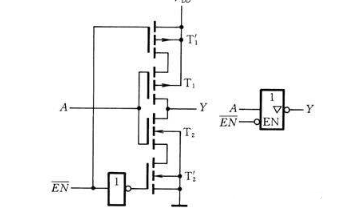

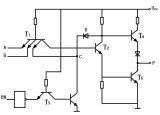

802 三態(tài)輸出門(mén)電路的輸出端除了出現(xiàn)高、低電平外,還會(huì)出現(xiàn)第三種狀態(tài)——高阻態(tài),所以叫做三態(tài)輸出門(mén)電路。 ? ?三態(tài)門(mén)的工作原理: 當(dāng)控制端a為“1”時(shí),b型管3導(dǎo)通,同時(shí)a端電平通過(guò)反向器成為低電平,讓

2021-08-12 11:39:49 10760

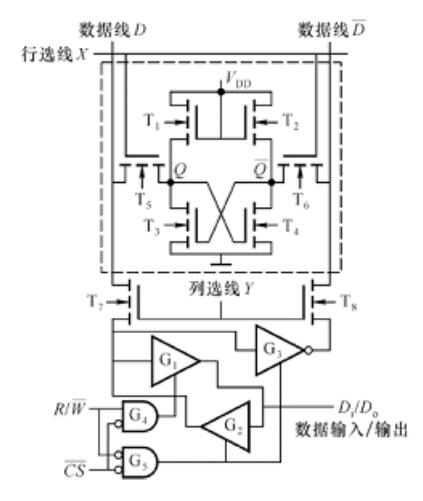

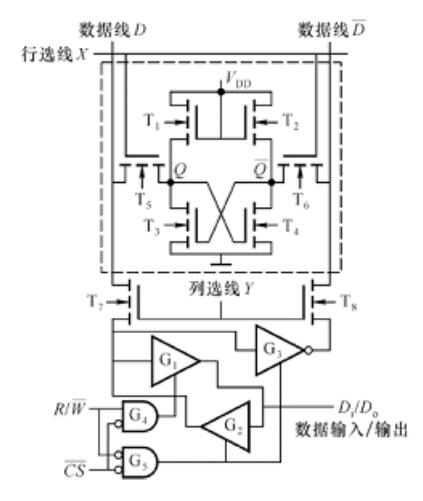

10760 數(shù)據(jù)必須首先在計(jì)算機(jī)內(nèi)被表示,然后才能被計(jì)算機(jī)處理。計(jì)算機(jī)表示數(shù)據(jù)的部件主要是存儲(chǔ)設(shè)備;而存儲(chǔ)數(shù)據(jù)的具體單位是存儲(chǔ)單元;因此,了解存儲(chǔ)單元的結(jié)構(gòu)是十分必要的。

2021-01-08 10:03:55 2042

2042 按照數(shù)據(jù)存取的方式不同,ram中的存儲(chǔ)單元分為兩種:靜態(tài)存儲(chǔ)單元一靜態(tài)RAM(SRAM);動(dòng)態(tài)存儲(chǔ)單元動(dòng)態(tài)RAM(DRAM)。 1.靜態(tài)存儲(chǔ)單元(SRAM):它由電源來(lái)維持信息,如觸發(fā)器,寄存器等

2020-12-02 14:31:30 2036

2036

本文檔的主要內(nèi)容詳細(xì)介紹的是三態(tài)門(mén)應(yīng)用的Multisim仿真實(shí)例電路圖免費(fèi)下載。

2020-09-23 17:32:00 38

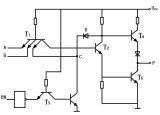

38 大學(xué)計(jì)算機(jī)教學(xué)中的計(jì)算機(jī)硬件實(shí)驗(yàn)。在計(jì)算機(jī)硬件實(shí)驗(yàn)中,三態(tài)電路有著廣泛的應(yīng)用,例如構(gòu)建一個(gè)具有分時(shí)共享功能的總線(xiàn)電路就需要用到多個(gè)三態(tài)電路。

2020-08-07 17:14:32 1593

1593

1.74HC595是典型的移位串轉(zhuǎn)并三態(tài)輸出驅(qū)動(dòng)器。2、8位并行三態(tài)輸出,并且可以級(jí)聯(lián)輸出。3、100MHz的移位頻率傳輸數(shù)據(jù)。4、高阻抗輸入,Mos推動(dòng)輸出。可以兼容TTL。5、74HC595常用封裝是s016和DP16。

2020-07-27 08:00:00 0

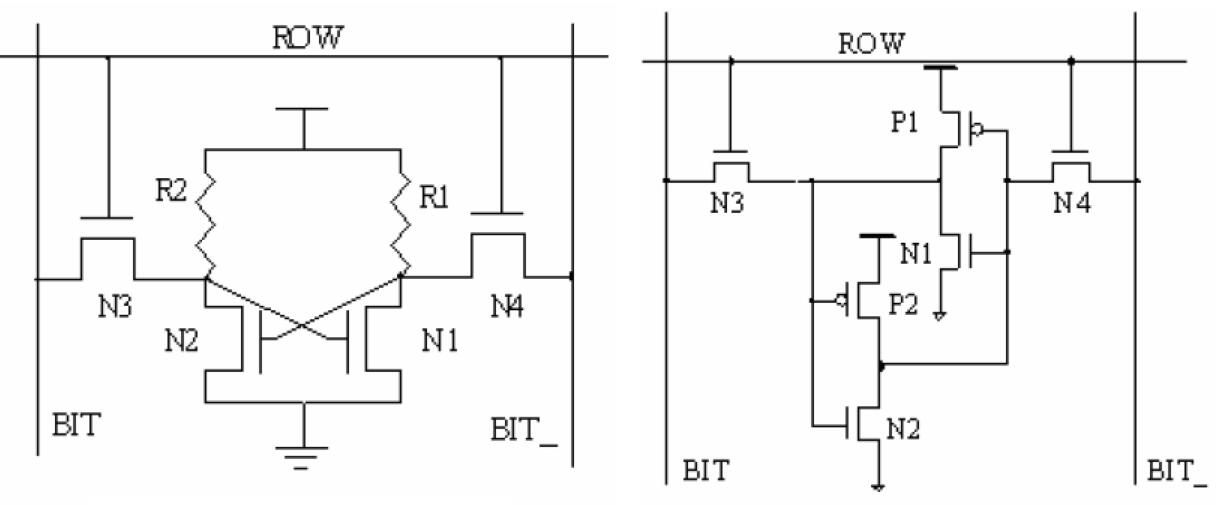

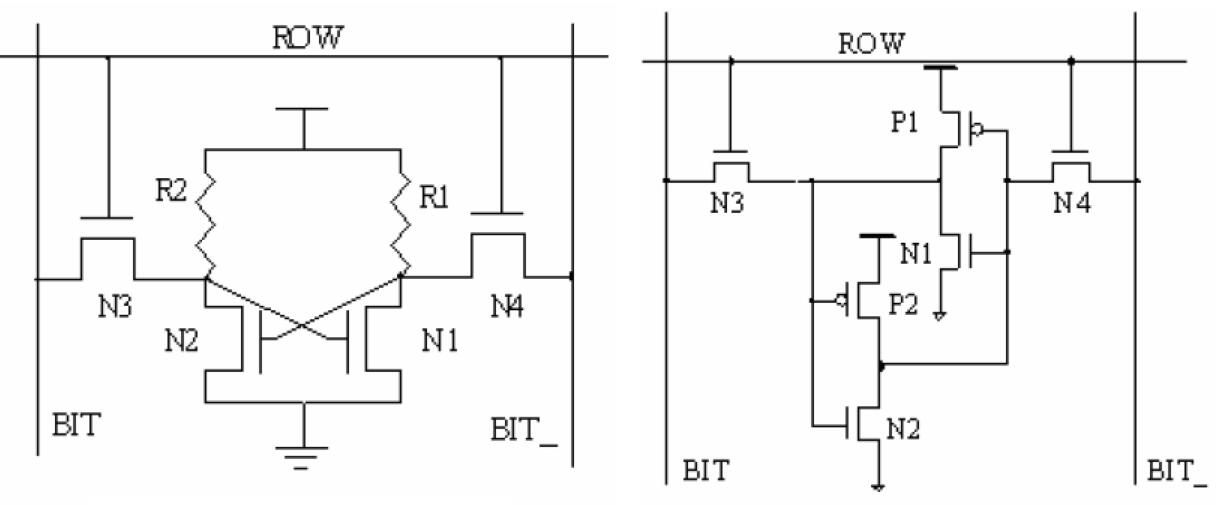

0 靜態(tài)RAM的基本構(gòu)造塊是SRAM存儲(chǔ)單元。通過(guò)升高字線(xiàn)的電平觸發(fā)存儲(chǔ)單元,再通過(guò)位線(xiàn)對(duì)所觸發(fā)的存儲(chǔ)單元進(jìn)行讀出或?qū)懭搿T陟o態(tài)CMOS存儲(chǔ)器中,存儲(chǔ)單元陣列將會(huì)占去整個(gè)存儲(chǔ)器芯片面積的一半以上,在一些

2020-05-14 09:19:47 2996

2996

常規(guī)的硬件實(shí)驗(yàn)測(cè)試三態(tài)總線(xiàn)電路邏輯功能的方法是,將三態(tài)輸出門(mén)的控制端、輸入端分別接邏輯電平開(kāi)關(guān),改變邏輯電平開(kāi)關(guān)為邏輯1、邏輯0觀測(cè)輸出函數(shù)的邏輯狀態(tài)。存在的問(wèn)題是,總線(xiàn)分時(shí)傳輸關(guān)系不直觀。用

2020-04-18 12:50:00 6304

6304 存儲(chǔ)單元的作用:可以進(jìn)行讀寫(xiě)操作以及存放數(shù)據(jù)。

2020-03-22 17:34:00 3663

3663 三態(tài)電路可提供三種不同的輸出值:邏輯“0”,邏輯“1”和高阻態(tài)。高阻態(tài)主要用來(lái)將邏輯門(mén)同系統(tǒng)的其他部分加以隔離。例如雙向I/O電路和共用總線(xiàn)結(jié)構(gòu)中廣泛應(yīng)用三態(tài)特性。

2019-11-29 07:09:00 3339

3339 三態(tài)電路可提供三種不同的輸出值:邏輯“0”,邏輯“1”和高阻態(tài)。高阻態(tài)主要用來(lái)將邏輯門(mén)同系統(tǒng)的其他部分加以隔離。例如雙向I/O電路和共用總線(xiàn)結(jié)構(gòu)中廣泛應(yīng)用三態(tài)特性。

2019-11-21 07:05:00 7465

7465 三態(tài)電路有什么特點(diǎn),什么是上拉電阻、下拉電阻以及高阻態(tài)?

2019-05-21 07:28:00 6003

6003

三態(tài)門(mén)亦稱(chēng)“三態(tài)輸出門(mén)”、“三態(tài)門(mén)輸出電路”。是一種重要的總線(xiàn)接口電路。具有高電平、低電平和高阻抗三種輸出狀態(tài)的門(mén)電路。

2019-03-10 09:29:25 15025

15025 三態(tài)指其輸出既可以是一般二值邏輯電路,即正常的高電平(邏輯1)或低電平(邏輯0),又可以保持特有的高阻抗?fàn)顟B(tài),那么三態(tài)門(mén)輸出的三種狀態(tài)是什么呢?

2019-02-21 16:45:59 66152

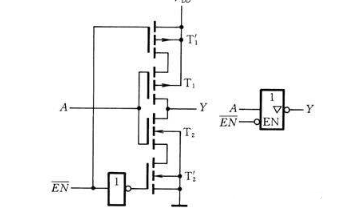

66152 三態(tài)緩沖器(Three-state buffer),又稱(chēng)為三態(tài)門(mén)、三態(tài)驅(qū)動(dòng)器,其三態(tài)輸出受到使能輸出端的控制,當(dāng)使能輸出有效時(shí),器件實(shí)現(xiàn)正常邏輯狀態(tài)輸出(邏輯0、邏輯1),當(dāng)使能輸入無(wú)效時(shí),輸出處于高阻狀態(tài),即等效于與所連的電路斷開(kāi)。

2018-10-24 16:09:36 32926

32926 本文從傳統(tǒng)三態(tài)開(kāi)關(guān)交錯(cuò)并聯(lián)DC/DC變換器的基本結(jié)構(gòu)出發(fā),將耦合電感和二極管電容同時(shí)融合到傳統(tǒng)的交錯(cuò)并聯(lián)DC/DC變換器中,構(gòu)造基于三態(tài)開(kāi)關(guān)單元與雙耦合電感的新型輸入端交錯(cuò)并聯(lián)高增益DC/DC變換器

2018-03-21 15:17:24 3

3 本文開(kāi)始介紹了三態(tài)門(mén)的定義與三態(tài)門(mén)的應(yīng)用,其次對(duì)三態(tài)門(mén)的三態(tài)及特點(diǎn)進(jìn)行了介紹,最后闡述了三態(tài)輸出門(mén)電路與三態(tài)門(mén)電路的圖形符號(hào)與真值表。

2018-03-01 14:47:41 113066

113066

三態(tài)指其輸出既可以是一般二值邏輯電路,即正常的高電平(邏輯1)或低電平(邏輯0),又可以保持特有的高阻抗?fàn)顟B(tài)。本文開(kāi)始介紹了三態(tài)門(mén)的定義,其次介紹了三態(tài)門(mén)的邏輯符號(hào),最后介紹了三款三態(tài)門(mén)邏輯電路。

2018-03-01 14:03:10 69342

69342

三態(tài)數(shù)據(jù)緩沖器是數(shù)據(jù)輸入/輸出的通道,數(shù)據(jù)傳輸?shù)姆较蛉Q于控制邏輯對(duì)三態(tài)門(mén)的控制。本文介紹三態(tài)緩沖器的邏輯符號(hào)。

2018-01-11 10:42:36 13281

13281

低電平,隨它后面接的東西定。三態(tài)門(mén),是指邏輯門(mén)的輸出除有高、低電平兩種狀態(tài)外,還有第三種狀態(tài)——高阻狀態(tài)的門(mén)電路。高阻態(tài)相當(dāng)于隔斷狀態(tài)(電阻很大,相當(dāng)于開(kāi)路)。 三態(tài)門(mén)都有一個(gè)EN控制使能端,來(lái)控制門(mén)電路的通斷。 可以具備這三種狀態(tài)的器件就叫做三態(tài)(門(mén),總線(xiàn),......)。

2017-12-25 11:27:11 20313

20313

。O工P存儲(chǔ)器的種類(lèi)很多,很多是基于熔絲和反熔絲,本文介紹的O工P存儲(chǔ)器基于反熔絲結(jié)構(gòu)。在反熔絲O工P存儲(chǔ)器中,通過(guò)對(duì)選中單元的編程改變了存儲(chǔ)單元內(nèi)部的結(jié)構(gòu)。理想的讀機(jī)制下,沒(méi)有編程的存儲(chǔ)單元讀取時(shí)會(huì)讀出0,而通過(guò)編程的存儲(chǔ)單元在讀取時(shí)會(huì)讀出1。反

2017-11-07 11:45:21 11

11 PSoC 4 三態(tài)緩沖器 Bufoe

2017-10-10 08:39:49 13

13 三態(tài)門(mén)在數(shù)字電路上可以說(shuō)是應(yīng)用的非常廣泛,特別是一些總線(xiàn)上的應(yīng)用,因而,隨著數(shù)字電路的發(fā)展,就避免不了用硬件描述語(yǔ)言在FPGA上來(lái)設(shè)計(jì)實(shí)現(xiàn)三態(tài)門(mén)。

2017-02-08 11:37:06 7000

7000 使用賽道存儲(chǔ)單元的近閾值非易失SRAM_孫憶南

2017-01-07 21:45:57 1

1 應(yīng)用于超低電壓下的SRAM存儲(chǔ)單元設(shè)計(jì)_劉冰燕

2017-01-07 21:39:44 0

0 三態(tài)緩沖器三態(tài)緩沖器三態(tài)緩沖器三態(tài)緩沖器三態(tài)緩沖器三態(tài)緩沖器三態(tài)緩沖器

2015-11-16 11:59:30 23

23 介紹了用Multisim仿真軟件分析三態(tài)門(mén)工作過(guò)程的方法,目的是探索三態(tài)門(mén)工作波形的仿真實(shí)驗(yàn)技術(shù),即用Multisim仿真軟件中的字組產(chǎn)生器產(chǎn)生三態(tài)門(mén)的控制信號(hào)及輸入信號(hào),用Multisim中示

2011-05-06 15:59:38 76

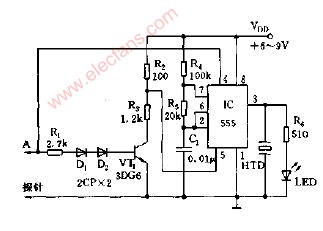

76 圖中所示用555時(shí)基電路集成三態(tài)聲光邏輯筆電路.555時(shí)基集成電路接成多諧振蕩器.

控

2010-10-03 16:56:03 1204

1204 本文就三態(tài)電路在FPGA中的應(yīng)用作了詳細(xì)的說(shuō)明。文章首先描述了一個(gè)調(diào)用lpm中三態(tài)電路模塊的VHDL程序,這個(gè)程序會(huì)出現(xiàn)編譯不能通過(guò)的問(wèn)題。然后從這個(gè)問(wèn)題出發(fā),通過(guò)嘗試三態(tài)電

2010-08-06 16:56:22 27

27 對(duì)第一代開(kāi)關(guān)電流存儲(chǔ)單元產(chǎn)生的時(shí)鐘饋通誤差做了合理的近似分析,設(shè)計(jì)了一種高性能開(kāi)關(guān)電流存儲(chǔ)單元。該電路僅在原存儲(chǔ)單元的基礎(chǔ)上增加了一個(gè)MOS管,使誤差降為原來(lái)的4%,

2010-07-05 14:50:48 22

22 具有三態(tài)輸出的集成電路其輸出具有可控的高阻抗?fàn)顟B(tài),廣泛應(yīng)用于總線(xiàn)結(jié)構(gòu)中。凡是輸出連接到總線(xiàn)的邏輯部件,例如:存儲(chǔ)器、總線(xiàn)控制器、總線(xiàn)接口等等。無(wú)論是TTL電路,還

2010-05-05 10:15:13 16

16 三態(tài)門(mén)的組成及工作原理

2010-02-28 19:13:26 23595

23595

單管動(dòng)態(tài)MOS存儲(chǔ)單元

2009-12-04 16:50:24 3661

3661 四管動(dòng)態(tài)MOS存儲(chǔ)單元

2009-12-04 16:34:14 2189

2189 六管NMOS靜態(tài)存儲(chǔ)單元

2009-12-04 15:30:03 6393

6393 E2PROM存儲(chǔ)單元的三種工作狀態(tài)

2009-12-04 13:04:45 1265

1265 E2PROM的存儲(chǔ)單元

2009-12-04 13:03:57 1418

1418 使用FAMOS管的存儲(chǔ)單元

2009-12-04 12:27:29 823

823

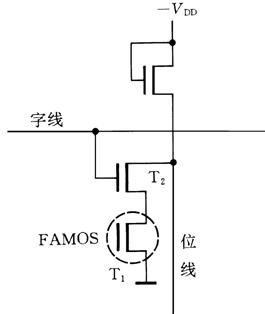

熔絲型PROM的存儲(chǔ)單元

2009-12-04 12:25:26 2114

2114

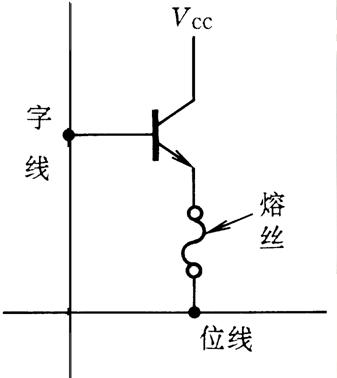

CMOS三態(tài)門(mén)電路結(jié)構(gòu)

(a)用或非門(mén)控制 (b)用與非門(mén)控制

2009-07-15 19:09:10 10707

10707

三態(tài)輸出門(mén)的電路圖和圖形符號(hào)

2009-07-15 19:03:57 2698

2698

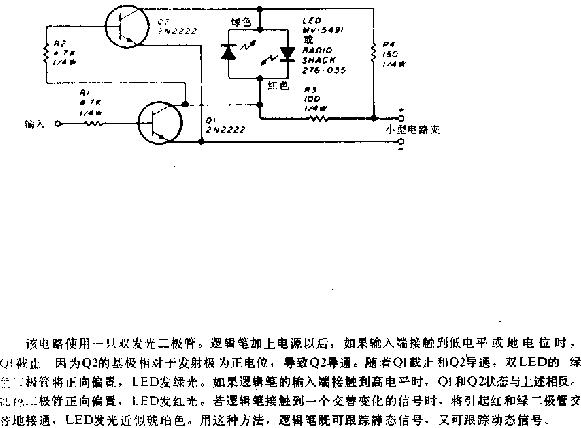

五用途三態(tài)聲頻邏輯比電路圖

2009-05-19 13:45:31 309

309

三態(tài)聲光邏輯筆電路圖

2009-05-19 13:42:17 652

652

三態(tài)邏輯筆電路圖

2009-04-07 09:16:34 1514

1514

TTL或非門(mén)、集電極開(kāi)路門(mén)和三態(tài)門(mén)電路

1.TTL或非門(mén)

下圖為T(mén)TL或非門(mén)的邏輯電路及其代表符號(hào)。

2009-04-07 00:11:59 13667

13667

如何處理內(nèi)部三態(tài)電路—PLD設(shè)計(jì)技巧 Tri-State vsMUX

Tri-State Buffer

There are two application area

2008-09-11 09:27:21 29

29 什么是三態(tài)門(mén)?

三態(tài)門(mén),是指邏輯門(mén)的輸出除有高、低電平兩種狀態(tài)外,還有第三種狀態(tài)——高阻狀態(tài)的門(mén)電路 高阻態(tài)相當(dāng)于隔斷狀態(tài)。

2008-05-26 12:48:24 41856

41856

低電壓甲乙類(lèi)開(kāi)關(guān)電流存儲(chǔ)單元

引言 開(kāi)關(guān)電流存儲(chǔ)單元是電流模式采樣數(shù)據(jù)信號(hào)處理系統(tǒng)的基本單元電路,其性能的優(yōu)

2007-08-15 16:06:29 532

532

電子發(fā)燒友App

電子發(fā)燒友App

硬聲App

硬聲App

389

389 213

213

0

0 0

0 0

0 0

0 0

0 3874

3874 1465

1465

2959

2959

802

802 10760

10760 2042

2042 2036

2036

38

38 1593

1593

0

0 2996

2996

6304

6304 3339

3339 7465

7465 6003

6003

15025

15025 66152

66152 32926

32926 3

3 113066

113066

69342

69342

13281

13281

20313

20313

11

11 7000

7000 0

0 23

23 76

76 1204

1204 27

27 22

22 16

16 10707

10707

13667

13667

29

29 41856

41856

532

532

評(píng)論