在紅外抄表等電路中,要用到38kHz載波來實現串口通訊,其串口就是普通的UART。總結出6種調制電路供發燒友們參考。1、基于三態門的標準的調制方式:當UART_TX為低電平時,38kHz信號可以通過

2016-12-30 18:24:57

上才都有顯示,這時測出的電壓是5V上面的是用proteus仿真的情況,在實際中,我看jtag模塊上都有一個74HC244這種芯片,我上網搜了一下,說244是三態8同相緩沖/驅動器,說是增加什么驅動

2014-07-20 11:49:56

FPGA 門數計算方法FPGA 門數計算方法 FPGA 等效門數的計算方法有兩種: 1.把FPGA 基本單元(如LUT+FF ,ESB/BRAM)和實現相同功能的標準門陣列比較,門陣列中包含的門數

2012-08-11 10:29:07

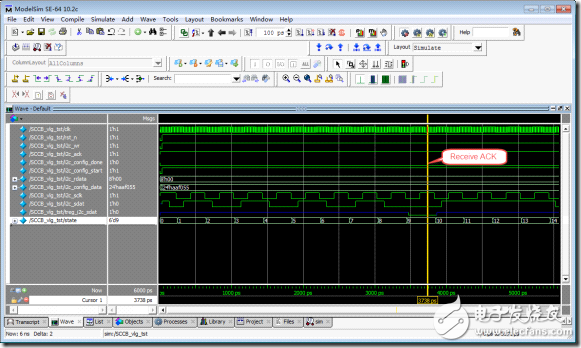

iic_sda_out賦想要輸出的值即可,當想要使用iic_sda作為輸入時,只需要令iic_en為0,然后去讀iic_sda的電平即可。但是需要注意三態門或者說時雙向端口定義最好只定義在頂層文件中,頂層

2020-06-03 18:32:58

1. 把FPGA 基本單元(如LUT+FF,ESB/BRAM)和實現相同功能的標準門陣列比較,門陣列中包含的門數即為該FPGA 基本單元的等效門數,然后乘以基本單元的數目就可以得到FPGA 門數

2012-03-01 10:08:53

FPGA中等效邏輯門概念數的計算方法有兩種,一是把FPGA基本單元(如LUT+FF,ESB/BRAM)和實現相同功能的標準門陣列比較,門陣列中包含的門數即為該FPGA基本單元的等效門數,然后乘以

2012-08-10 14:05:35

我遇到的情景中,一般后仿真出現不定態的原因有三個:更多的后仿出現不定態的的情形可以參考以下文章。驗證那些事最近陸續寫了點工作方面的小文章,遂決定新開一個公眾號,專門放工作相關的文章,就叫《超人驗證

2022-01-18 06:35:33

FPGA布線開關的電路設計1 研究方法及其條件假定2 導通晶體管布線開關設計 2.1導通晶體管布線開關尺寸優化2.2 導通晶體管存在的問題及其改進3 三態緩沖布線開關的設計3.1三態緩沖器尺寸優化3.2 三態緩沖布線開關的缺點及其改進4 各種布線開關性能比較及其建議

2011-03-02 09:50:16

出來的是一個什么樣的電路,計數器選擇器 三態門等等,理解時序,邏輯是一拍一拍的東西,在設計初期想的不是很清楚的時候可以畫畫時序圖,這樣思路會更加的清晰,還有就是仿真很重要,不要寫完程序就去往FPGA中去

2017-05-02 16:59:07

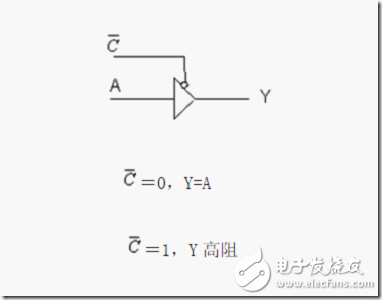

三態門的工作原理是什么?

2021-05-20 06:55:47

三態門輸入信號和輸出信號之間接電阻是什么用法?

2017-04-09 19:36:20

一、三態單片機IO的三態是指:高電平(1)、低電平(0)、高組態(Z)。二、高阻態高阻i是一種電路狀態.既不是高電平,也不是低電平,以高阻態對下級電路輸出,下級電路什么影響也沒有.高阻態的IO電平

2021-11-25 06:42:28

如圖是一個三態反相緩沖器,我想把它和一個自偏電阻連起來做一個放大器。

2019-01-28 16:40:28

如果我在其中一個存儲器上使用32位三態輸出,則合成器會添加一個切片。有人能告訴我內部三態緩沖器在FPGA架構中的位置(我得到了kintex 7)嗎?我在CLB指南中找了它,但沒找到

2019-03-04 13:17:18

。看起來微處理器正在寫入FPGA而不是從FPGA讀取。但情況應該不是這樣,而應該恰恰相反!在推斷三態緩沖區時,我是否設置了錯誤?當我在planAhead中打開設計時,我可以看到“io_data”被認為是

2019-03-08 14:01:02

三態輸出門的電路圖和圖形符號

2019-10-25 07:17:31

1、AD5420的SDO是否是三態輸出腳

2、MCU的SPI接口配置CPOL=0、CPAH=0,是否正確

2023-12-20 08:08:51

AD9280三態引腳是否只是控制數據輸出端的,和轉換過程沒有關系?

現在問題是FPGA引腳不夠用了,能否將兩片AD9280數據D0-D7接在一起,時鐘是共用的,兩片AD同步輸出,在數據開始輸出后用三態引腳控制取數?

2023-12-14 06:49:33

一片ADS1211時要求其余兩片的ADS1211的SDOUT引腳此時具有三態狀態,以實現讓出SPI數據接口的目的,ADS1211的SDOUT具有三態狀態,可是:The CS signal does

2019-05-23 08:07:10

CPLD/FPGA實現I2C的透傳,使用三態門,那么SDA的方向應向該如何確定?assign SCL_OUT = SCL_IN;wire mid;assign mid = dir?1'bz

2019-01-11 09:49:55

我正在尋找在Spartan 3A中使用多路復用器與三態緩沖器之間的比較。從某個區域和時間角度來看哪個更好?謝謝,戴爾以上來自于谷歌翻譯以下為原文I'm looking for a

2019-01-16 10:37:07

PSoC Creator組件數據手冊/PSoC 4:三態緩沖器 (Bufoe) 組件是非反相緩沖器,其使能信號高電平有效。當輸出使能信號為真時,次緩沖器用作標準緩沖器。當輸出使能信號為假時,次緩沖器關閉。

2013-07-03 11:15:11

inout Key_inout;wire Key_input;//輸入reg Key_output;//輸出reg Key_Ctr;//三態控制assign Key_inout=Key_Ctr

2014-09-23 15:34:43

芯片外部引腳很多都使用inout類型的,為的是節省管腿。一般信號線用做總線等雙向數據傳輸的時候就要用到INOUT類型了。就是一個端口同時做輸入和輸出。 inout在具體實現上一般用三態門來實現。三態

2012-01-17 10:08:04

這兩個模塊都是編寫的一個4位4通道的三態總線驅動器,編譯后RTL圖是一樣的第二個模塊仿真是沒有問題的,輸出都是正常的但,第一個模塊從仿真上看,當en 為“00”時輸出是正常的,en其余狀態時,輸出

2019-01-30 11:18:46

一介紹。當三態輸出信號es選通時,即es=“1”,PC可輸出,否則輸出為高阻態。數據或地址與總線相關的子模塊都需采用三態門。由于采用了三態門,最好用QuartusⅡ軟件來進行編譯,Max+plusⅡ有時

2014-12-04 14:35:41

一介紹。當三態輸出信號es選通時,即es=“1”,PC可輸出,否則輸出為高阻態。數據或地址與總線相關的子模塊都需采用三態門。由于采用了三態門,最好用QuartusⅡ軟件來進行編譯,Max+plusⅡ有時

2014-12-04 14:36:22

如果:紅色-0,綠色-1,藍色-2

輸入:數組

輸出:布爾數組或簇

例如:輸入數組為〔0 1 2 1 0〕

希望輸出顯示為紅色,綠色,藍色,綠色,紅色的一組三態燈。

網上給的子vi是利用bool引用句柄實現一個燈的三態顯示,如果數組元素少的話用枚舉可以實現,但是如果數組元素很多,有什么簡便的方法嗎?

2015-12-09 14:32:54

求教大佬:proteus中用74LS164驅動共陽極數碼管顯示,顯示的時候數字是對的,但是數字一直在閃爍是為什么呢?是因為沒有在74LS164的輸出端接三態門嗎? ???

2020-11-02 06:42:30

等,要求信號為三態類型,也就是我們所說的輸入輸出(inout)類型。那么,本節夢翼師兄將和大家一起來探討三態門的用法。項目需求設計一個三態門電路,可以實現數據的輸出和總線“掛起”。系統架構 模塊功能

2019-12-12 16:11:51

本帖最后由 gk320830 于 2015-3-4 23:25 編輯

【經典】集電極開路,漏極開路,推挽,上拉電阻,弱上拉,三態門,準雙向口

2012-07-29 21:17:03

并不能直接并接使用,否則這些門的輸出管之間由于低阻抗形成很大的短路電流(灌電流),而燒壞器件.在硬件 上,可用OC門或三態門(ST門)來實現. 用OC門實現線與,應同時在輸出端口應加一個上拉電阻.3

2016-08-23 21:39:46

,VCCBRAM,VCCAUX和VCCO,以實現最小電流消耗,即I / O在上電時為3。我應該關心這件事嗎?在上電過程中,I / O引腳是否應該處于三態?任何幫助將不勝感激。謝謝,菲利普

2020-07-30 09:51:29

AD9280三態引腳是否只是控制數據輸出端的,和轉換過程沒有關系?現在問題是FPGA引腳不夠用了,能否將兩片AD9280數據D0-D7接在一起,時鐘是共用的,兩片AD同步輸出,在數據開始輸出后用三態引腳控制取數?

2019-01-09 09:30:29

三態門和OC門一、OC門實際使用中,有時需要兩個或兩個以上與非門的輸出端連接在同一條導線上,將這些與非門上的數據(狀態)用同一條導線輸送出去。因此,需要一種新的與非門電路來實現線與邏輯,這種門電路

2008-05-26 13:01:37

的不足,同時也方便在現場可編程門陣列(FPGA)中增加一些其他相關的應用功能,因此在FPGA中實現CVSD語音編譯碼調制功能的前景將是非常廣闊的。這里將詳細介紹什么是CVSD?其算法分析如何在FPGA中實現?

2019-08-07 07:04:27

`剛剛本科畢業,假期導師要求做一個設計。實驗室沒有做過FPGA的學長只好問網上的各位了。寫好的FPGA代碼進行RTL仿真波形是符合要求的,如下圖。但是做門級仿真的時候,時序就不對了,變成了這樣

2016-08-06 12:12:03

三態LED 子vi

2017-01-13 10:39:39

在一起,并且在需要將門彼此分離的應用中,可以使用三態緩沖器或三態輸出驅動器。“三態緩沖器”除了上面看到的標準數字緩沖器外,還有另一種類型的數字緩沖器電路,其輸出可以在需要時從其輸出電路“電子斷開”。這種

2021-01-26 09:16:58

設計上,它會成為一個錯誤!對我來說,三態使能引腳沒有連接到芯片上的引腳,不是它是一個輸出,所以它沒有轉換約束,測試設計沒有用戶約束文件,只是選擇IO向導為選擇IO IP制作的文件, 所以我在xilinx

2020-08-05 12:07:55

/ axigpio_v2_0.tcl中有一個額外的']'是第246行的結尾在GPIO2接口上添加三態GPIO端口時會導致錯誤。以上來自于谷歌翻譯以下為原文There is a small bug

2019-04-19 10:32:27

三態門高阻態時,同或門輸出狀態怎么判斷?F的 邏輯表達式

2015-12-15 10:59:57

大家好!我想知道如何在FPGA中使用VHDL實現過零檢測器。所以我想實現一個數字常數小數鑒別器。 firt部分提供了雙極性信號,但我想知道如何在vhdl中實現過零檢測器。感謝您的幫助!以上來自于谷歌

2019-01-29 08:16:40

親愛的大家! 如何在IOB中為spartan-3生成FPGA使用TFF(TFF1和TFF2三態觸發器)? 我想在spartan-3 FPGA(Spartan-3 GenerationFPGA用戶指南

2019-06-28 09:53:28

必須是明確的。 OFDDRSE元素可用于IOB中的數據路徑,但我找不到更“完整”的元素,其中還包含三態路徑(OFDDRTRSE只有簡單的三態路徑)。我嘗試使用OFDDRSE并使用它來控制三態上的啟用

2019-05-13 08:41:11

在FPGA中,動態相位調整(DPA)主要是實現LVDS接口接收時對時鐘和數據通道的相位補償,以達到正確接收的目的。那么該如何在低端FPGA中實現DPA的功能呢?

2021-04-08 06:47:08

]set to input with tri-state,我給芯片配置完之后,只需要將DO(數據)引腳設置輸入就行了嗎?不太懂這里的輸入三態啥意思?[size=18.6667px]而且,時鐘線應該沒啥

2017-03-29 10:29:23

如何才能制作一個三態指示燈?需要什么材料等等

2014-10-28 19:51:17

反相器的速度與哪些因素有關?什么是轉換時間和傳播延遲呢?怎樣去設計一種CMOS三態緩沖器的電路呢?

2021-10-20 06:24:39

本帖最后由 yogaqingyun 于 2016-1-11 13:17 編輯

b=1時輸出高阻態,cde都是高電平,當d變為低電平,ce也都為低;b=0時,輸出為a是低電平。求個小程序,我自己的仿真總是不對啊。用Verilog描述完是這樣的就行。

2016-01-11 13:03:18

要找一個7路輸入/輸出并帶高阻的三態輸出的邏輯IC,體積要小點的,有知道的請推薦一下,謝謝!!!積分只有13分,全給了。

2016-01-04 11:36:40

大家好,我是一名大學生,最近剛接觸數字電子和單片機,產生了興趣后,嘗試著去學習它,但是碰到不少問題,其中TTL門中的OC門和三態門不是很清楚,所以找了幾道題想知道詳細的解答,我知道答案,但是為什么是這個結果,請各路大神多關照一下,帶帶初級生。

2014-03-13 23:56:56

如圖一中,unused pin是配置為“三態輸入輸入”,還是“三態輸入加弱上拉”。圖二中,為什么要把這些dual_purpose_pin設置為“use as regular IO”.他們可是專用的引腳的啊

2018-07-11 23:35:47

我有一個使用MCLR作為輸入的項目。用PICTIT2 MCLR放在編程后的三態,但是用皮卡4,似乎PIN保持高。這有什么設置嗎? 以上來自于百度翻譯 以下為原文 I have a project

2018-10-26 16:11:59

描述PCB_三態極性指示器使用 1K 電阻 (x2) 和任何硅二極管。頂部的綠色 LED 底部的紅色。使用厚二極管腿作為探針和帶有鱷魚夾的接地線。

2022-08-30 07:31:27

新人在工作中經常碰到三態門與高阻態;請教技術大佬,這兩個到底是什么東西 ?

2021-04-07 06:59:01

1、AD5420的SDO是否是三態輸出腳2、MCU的SPI接口配置CPOL=0、CPAH=0,是否正確

2018-12-20 09:26:31

ISIM不能處理1Mb信號)。我也測試了它,用邏輯分析儀我可以看到信號,地址和寫入數據是正確的,時間也很好,但讀數不對。我的猜測是它與雙向數據總線有關,我知道內部三態在spartan-3上不再可用,但我

2019-06-26 10:24:04

請問這個三態門為什么不能實現非功能?它的邏輯表達式不應該是A非嗎?

2023-04-26 11:49:06

請問這個三態門為什么不能實現非功能?它的邏輯表達式不應該是A非嗎?

2023-05-10 17:44:20

邏輯門及組合邏輯電路實驗實驗目的1. 掌握與非門、或非門、與或非門及異或門的邏輯功能。2. 了解三態門的邏輯功能以及禁止狀態的判別方法。了解三態門的應用。3. 掌握組合邏輯電路的設計和實現方法。4.

2008-09-25 17:28:34

集電極開路 漏極開路 推挽 上拉電阻 弱上拉 三態門 準雙向口

2016-06-02 16:22:21

高阻態和三態門高阻態 高阻態的實質:電路分析時高阻態可做開路理解。你可以把它看作輸出(輸入)電阻非常大。他的極限可以認為懸空。也就是說理論上高阻態不是懸空,它是對地或對電源電阻極大的狀態。而實際

2019-01-08 11:03:07

數字電路常見術語:高阻態,三態門高阻態常用的表示方法

2021-03-01 11:09:49

懸空,顧名思義,就是不接任何器件啦高阻態:無上拉和無下拉,對外表現出電平不確定性不是所有的單片機都支持三態輸出。三態輸出一般由寄存器控制,需進行配置。高阻態既然無確定電平,怎么能做輸出呢?把一個端口

2021-11-24 08:19:25

小波盲源分離算法的仿真及FPGA實現:提出了一種基于小波變換的盲源分離方法,在理論分析和仿真結果的基礎上,給出了FPGA 的實現方案。針對傳統盲分離算法對源信號統計特征敏

2009-06-21 22:44:09 21

21 本文就三態電路在FPGA中的應用作了詳細的說明。文章首先描述了一個調用lpm中三態電路模塊的VHDL程序,這個程序會出現編譯不能通過的問題。然后從這個問題出發,通過嘗試三態電

2010-08-06 16:56:22 27

27 介紹了用Multisim仿真軟件分析三態門工作過程的方法,目的是探索三態門工作波形的仿真實驗技術,即用Multisim仿真軟件中的字組產生器產生三態門的控制信號及輸入信號,用Multisim中示

2011-05-06 15:59:38 0

0 dac0832ad08098259a,825382508255等芯片的fpga實現及仿真

2016-01-20 15:12:47 13

13 的一個例子,HDL語言的INOUT端口仿真暨三態門仿真,VerilogHDL 的三態門實現與仿真,ARM 總線的三態門實現與仿真

2019-07-09 16:49:27 10

10 核的不同模塊進行實體/塊的仿真。前文回顧如何測試與驗證復雜的FPGA設計(1)——面向實體或塊的仿真在本篇文章中,我們將介紹如何在虹科IP核中執行面向全局的仿真,而這也是測

2022-06-15 17:31:20 389

389

電子發燒友App

電子發燒友App

評論