三態(tài)門的組成及工作原理

- 三態(tài)門(18568)

相關(guān)推薦

什么是三態(tài)門和OC門?

三態(tài)門和OC門一、OC門實(shí)際使用中,有時(shí)需要兩個(gè)或兩個(gè)以上與非門的輸出端連接在同一條導(dǎo)線上,將這些與非門上的數(shù)據(jù)(狀態(tài))用同一條導(dǎo)線輸送出去。因此,需要一種新的與非門電路來(lái)實(shí)現(xiàn)線與邏輯,這種門電路

2008-05-26 13:01:37

三態(tài)輸出的緩沖器有哪些用途?

三態(tài)輸出的緩沖器有哪些用途? 三態(tài)輸出緩沖器是一種電子元件,其主要作用是將一個(gè)輸入信號(hào)轉(zhuǎn)換成一個(gè)可以控制多個(gè)輸出設(shè)備的信號(hào)。這種緩沖器可以被用于一系列的應(yīng)用,包括數(shù)碼電路、計(jì)算機(jī)、消費(fèi)電子設(shè)備、通信

2023-09-21 15:55:36 389

389

389

389Versal HDIO OBUFT和IOBUF三態(tài)時(shí)序影響

本文著重探討 HDIO OBUFT 和 IOBUF 用例。如果含三態(tài)控制 (OBUFT/IOBUF) 的 HDIO 輸出緩沖器的上電電壓為 3.3 V 或 2.5 V 并且 Data(數(shù)據(jù))控制信號(hào)與 Tristate(三態(tài))控制信號(hào)的切換時(shí)間彼此相近,則可能會(huì)受到三態(tài)數(shù)據(jù)爭(zhēng)用條件的影響。

2023-07-12 09:50:32 213

213

213

213

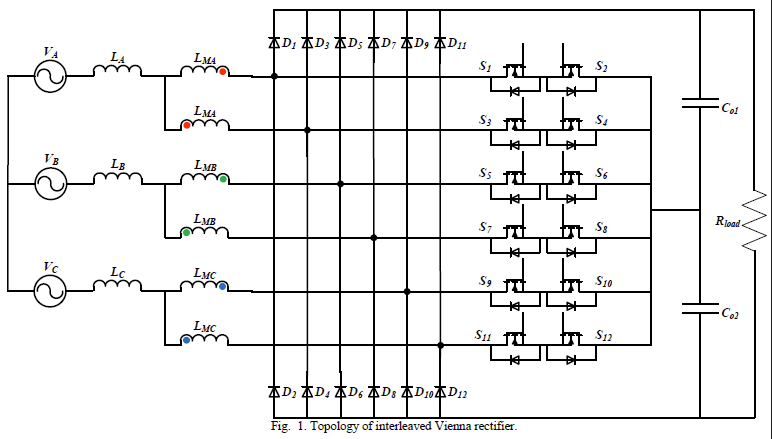

三相五電平VIENNA的工作原理

該拓?fù)渑c傳統(tǒng)三相三電平VIENNA主要區(qū)別是每相都有一個(gè)三態(tài)開關(guān)電路。所謂三態(tài)開關(guān)中的“三態(tài)”,就是指每相都會(huì)有三種開關(guān)狀態(tài)或者工作狀態(tài),同時(shí)會(huì)在橋臂端口Vx點(diǎn)的位置形成五種電平狀態(tài),因此也稱

2023-03-23 09:26:27 1972

1972

1972

1972

八進(jìn)制透明鎖存器(三態(tài));八進(jìn)制D觸發(fā)器(三態(tài))-74F373_374

八進(jìn)制透明鎖存器(三態(tài));八進(jìn)制 D 觸發(fā)器(三態(tài))-74F373_374

2023-03-03 20:05:16 0

0

0

018 位緩沖器/驅(qū)動(dòng)器;三態(tài)-74ALVCH16825

18 位緩沖器/驅(qū)動(dòng)器;三態(tài)-74ALVCH16825

2023-02-21 19:36:42 0

0

0

0FPGA三態(tài)門的結(jié)構(gòu)是怎樣的呢?

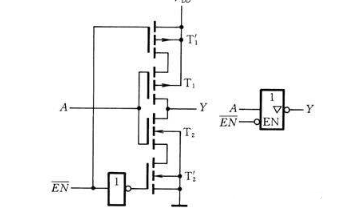

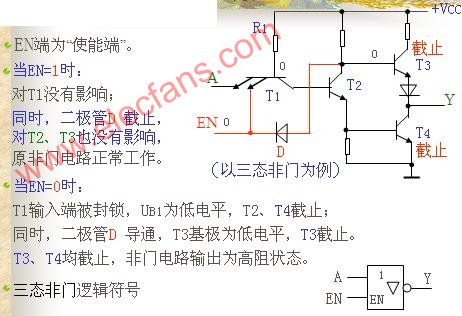

由上圖看出,在單相三態(tài)門中,當(dāng)EN=1時(shí),對(duì)原電路無(wú)影響,電路的輸出符合原來(lái)電路的所有邏輯關(guān)系,即A可以輸出到B。當(dāng)EN= 0時(shí),電路內(nèi)部的所有輸出與外部將處于一種關(guān)斷狀態(tài)。

2022-10-20 11:01:02 904

904

904

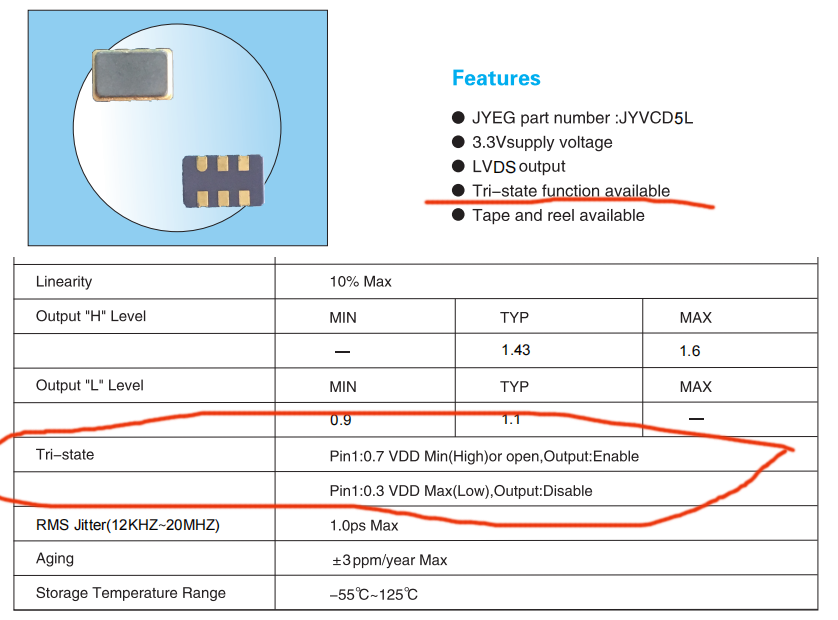

904晶體振蕩器的三態(tài)功能及控制邏輯

選購(gòu)石英晶體振蕩器(XO)時(shí),有些規(guī)格書(datasheet)標(biāo)有三態(tài)(tri-state)控制功能,有些則沒有該功能。那么,三態(tài)控制究竟是什么神秘武器?

2022-07-25 08:54:03 1828

1828

1828

1828

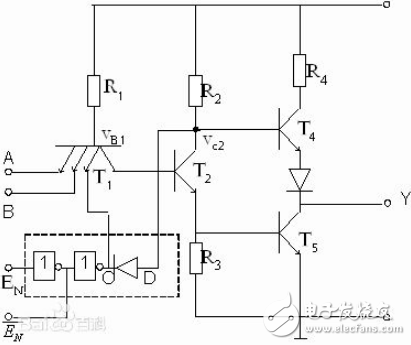

三態(tài)輸出門的工作原理

三態(tài)輸出門電路的輸出端除了出現(xiàn)高、低電平外,還會(huì)出現(xiàn)第三種狀態(tài)——高阻態(tài),所以叫做三態(tài)輸出門電路。 ? ?三態(tài)門的工作原理: 當(dāng)控制端a為“1”時(shí),b型管3導(dǎo)通,同時(shí)a端電平通過(guò)反向器成為低電平,讓

2021-08-12 11:39:49 10760

10760

10760

10760數(shù)字電路常見術(shù)語(yǔ):高阻態(tài),三態(tài)門資料下載

電子發(fā)燒友網(wǎng)為你提供數(shù)字電路常見術(shù)語(yǔ):高阻態(tài),三態(tài)門資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計(jì)、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-27 08:45:27 13

13

13

13三態(tài)門應(yīng)用的Multisim仿真實(shí)例電路圖免費(fèi)下載

本文檔的主要內(nèi)容詳細(xì)介紹的是三態(tài)門應(yīng)用的Multisim仿真實(shí)例電路圖免費(fèi)下載。

2020-09-23 17:32:00 38

38

38

38三態(tài)門總線傳輸電路的工作特性及仿真研究

Multisim仿真軟件進(jìn)行三態(tài)總線電路工作過(guò)程波形仿真分析,用環(huán)形計(jì)數(shù)器做實(shí)驗(yàn)中的信號(hào)源產(chǎn)生所需的各個(gè)控制信號(hào)、用脈沖信號(hào)源產(chǎn)生各數(shù)據(jù)輸入信號(hào),用邏輯分析儀多蹤同步顯示各個(gè)三態(tài)門的控制信號(hào)、數(shù)據(jù)輸入信號(hào)及總線輸出信號(hào)波形,可直觀形象地描述三態(tài)門總線傳輸電路的工作特性。

2020-04-18 12:50:00 6304

6304

6304

6304FPGA之三態(tài)門

三態(tài)電路可提供三種不同的輸出值:邏輯“0”,邏輯“1”和高阻態(tài)。高阻態(tài)主要用來(lái)將邏輯門同系統(tǒng)的其他部分加以隔離。例如雙向I/O電路和共用總線結(jié)構(gòu)中廣泛應(yīng)用三態(tài)特性。

2019-11-29 07:09:00 3339

3339

3339

3339三態(tài)門的用法及模塊功能介紹

三態(tài)電路可提供三種不同的輸出值:邏輯“0”,邏輯“1”和高阻態(tài)。高阻態(tài)主要用來(lái)將邏輯門同系統(tǒng)的其他部分加以隔離。例如雙向I/O電路和共用總線結(jié)構(gòu)中廣泛應(yīng)用三態(tài)特性。

2019-11-21 07:05:00 7465

7465

7465

7465三態(tài)門原理HDL語(yǔ)言DSP和ARM總線的仿真及Modelsim使用教程資料

本文檔的主要內(nèi)容詳細(xì)介紹的是三態(tài)門原理HDL語(yǔ)言DSP和ARM總線的仿真及Modelsim使用教程資料主要內(nèi)容包括了:1 ModelSimSE的使用流程,2 一個(gè)Verilog計(jì)數(shù)器仿真詳細(xì)流程附

2019-07-09 16:49:27 9

9

9

9什么是三態(tài)電路 三態(tài)電路有什么特點(diǎn)

三態(tài)電路有什么特點(diǎn),什么是上拉電阻、下拉電阻以及高阻態(tài)?

2019-05-21 07:28:00 6003

6003

6003

6003

三態(tài)門怎么理解

三態(tài)門亦稱“三態(tài)輸出門”、“三態(tài)門輸出電路”。是一種重要的總線接口電路。具有高電平、低電平和高阻抗三種輸出狀態(tài)的門電路。

2019-03-10 09:29:25 15025

15025

15025

15025三態(tài)門的作用

三態(tài)門主要是用于總線的連接,因?yàn)榭偩€只允許同時(shí)只有一個(gè)使用者。通常在數(shù)據(jù)總線上接有多個(gè)器件,每個(gè)器件通過(guò)OE/CE之類的信號(hào)選通。如器件沒有選通的話它就處于高阻態(tài),相當(dāng)于沒有接在總線上,不影響其它器件的工作。

2019-03-08 16:49:37 21629

21629

21629

21629三態(tài)門輸出的三種狀態(tài)

三態(tài)指其輸出既可以是一般二值邏輯電路,即正常的高電平(邏輯1)或低電平(邏輯0),又可以保持特有的高阻抗?fàn)顟B(tài),那么三態(tài)門輸出的三種狀態(tài)是什么呢?

2019-02-21 16:45:59 66152

66152

66152

66152三態(tài)緩沖器工作原理

三態(tài)緩沖器(Three-state buffer),又稱為三態(tài)門、三態(tài)驅(qū)動(dòng)器,其三態(tài)輸出受到使能輸出端的控制,當(dāng)使能輸出有效時(shí),器件實(shí)現(xiàn)正常邏輯狀態(tài)輸出(邏輯0、邏輯1),當(dāng)使能輸入無(wú)效時(shí),輸出處于高阻狀態(tài),即等效于與所連的電路斷開。

2018-10-24 16:09:36 32926

32926

32926

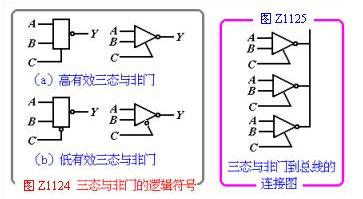

32926三態(tài)邏輯與非門基本輸出狀態(tài)及其應(yīng)用電路解析

三態(tài)門,是指邏輯門的輸出除有高、低電平兩種狀態(tài)外,還有第三種狀態(tài)——高阻狀態(tài)的門電路 高阻態(tài)相當(dāng)于隔斷狀態(tài)。

2018-07-26 10:53:43 29132

29132

29132

29132

傳輸門和三態(tài)門什么區(qū)別

本文主要介紹了傳輸門和三態(tài)門什么區(qū)別,三態(tài)門就是指輸出有三種狀態(tài)(0,1,高阻)的門。傳輸門就是指可以控制通路通斷的門,導(dǎo)通時(shí),一端的信號(hào)可以傳到另一端,不導(dǎo)通時(shí),一端信號(hào)不能傳到另一端。兩者不是

2018-04-08 15:33:49 51792

51792

51792

51792

三態(tài)門有哪三態(tài)_三態(tài)門有什么特點(diǎn)

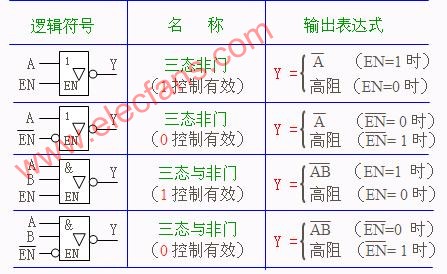

本文開始介紹了三態(tài)門的定義與三態(tài)門的應(yīng)用,其次對(duì)三態(tài)門的三態(tài)及特點(diǎn)進(jìn)行了介紹,最后闡述了三態(tài)輸出門電路與三態(tài)門電路的圖形符號(hào)與真值表。

2018-03-01 14:47:41 113066

113066

113066

113066

三態(tài)門邏輯電路圖大全(三款三態(tài)門邏輯電路圖)

三態(tài)指其輸出既可以是一般二值邏輯電路,即正常的高電平(邏輯1)或低電平(邏輯0),又可以保持特有的高阻抗?fàn)顟B(tài)。本文開始介紹了三態(tài)門的定義,其次介紹了三態(tài)門的邏輯符號(hào),最后介紹了三款三態(tài)門邏輯電路。

2018-03-01 14:03:10 69342

69342

69342

69342

三態(tài)緩沖器介紹_三態(tài)緩沖器邏輯符號(hào)

三態(tài)數(shù)據(jù)緩沖器是數(shù)據(jù)輸入/輸出的通道,數(shù)據(jù)傳輸?shù)姆较蛉Q于控制邏輯對(duì)三態(tài)門的控制。本文介紹三態(tài)緩沖器的邏輯符號(hào)。

2018-01-11 10:42:36 13281

13281

13281

13281

高阻態(tài)實(shí)質(zhì)意義和應(yīng)用以及三態(tài)門的詳細(xì)分析

低電平,隨它后面接的東西定。三態(tài)門,是指邏輯門的輸出除有高、低電平兩種狀態(tài)外,還有第三種狀態(tài)——高阻狀態(tài)的門電路。高阻態(tài)相當(dāng)于隔斷狀態(tài)(電阻很大,相當(dāng)于開路)。 三態(tài)門都有一個(gè)EN控制使能端,來(lái)控制門電路的通斷。 可以具備這三種狀態(tài)的器件就叫做三態(tài)(門,總線,......)。

2017-12-25 11:27:11 20313

20313

20313

20313

三態(tài)門如何在FPGA中實(shí)現(xiàn)與仿真

三態(tài)門在數(shù)字電路上可以說(shuō)是應(yīng)用的非常廣泛,特別是一些總線上的應(yīng)用,因而,隨著數(shù)字電路的發(fā)展,就避免不了用硬件描述語(yǔ)言在FPGA上來(lái)設(shè)計(jì)實(shí)現(xiàn)三態(tài)門。

2017-02-08 11:37:06 7000

7000

7000

7000集電極開路_漏極開路_推挽_上拉電阻_弱上拉_三態(tài)門_準(zhǔn)雙向口

集電極開路_漏極開路_推挽_上拉電阻_弱上拉_三態(tài)門_準(zhǔn)雙向口,感興趣的小伙伴們可以瞧一瞧。

2016-11-16 18:32:35 14

14

14

14三態(tài)緩沖器介紹

三態(tài)緩沖器三態(tài)緩沖器三態(tài)緩沖器三態(tài)緩沖器三態(tài)緩沖器三態(tài)緩沖器三態(tài)緩沖器

2015-11-16 11:59:30 23

23

23

23三態(tài)門總線傳輸電路的Multisim仿真方案

基于探索仿真三態(tài)門總線傳輸電路的目的,采用Multisim10仿真軟件對(duì)總線連接的三態(tài)門分時(shí)輪流工作時(shí)的波形進(jìn)行了仿真實(shí)驗(yàn)測(cè)試,給出了仿真實(shí)驗(yàn)方案,即用Multisim仿真軟件構(gòu)成環(huán)形計(jì)

2013-06-08 17:58:44 48

48

48

48三態(tài)門邏輯功能的Multisim仿真方案

介紹了用Multisim仿真軟件分析三態(tài)門工作過(guò)程的方法,目的是探索三態(tài)門工作波形的仿真實(shí)驗(yàn)技術(shù),即用Multisim仿真軟件中的字組產(chǎn)生器產(chǎn)生三態(tài)門的控制信號(hào)及輸入信號(hào),用Multisim中示

2011-05-06 15:59:38 76

76

76

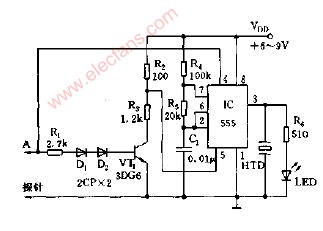

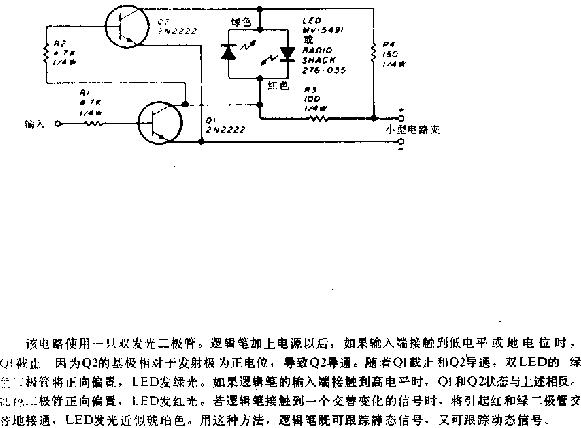

76555電路組成三態(tài)聲光邏輯筆電路圖

圖中所示用555時(shí)基電路集成三態(tài)聲光邏輯筆電路.555時(shí)基集成電路接成多諧振蕩器.

控

2010-10-03 16:56:03 1204

1204

1204

1204三態(tài)電路在FPGA應(yīng)用設(shè)計(jì)中的分析

本文就三態(tài)電路在FPGA中的應(yīng)用作了詳細(xì)的說(shuō)明。文章首先描述了一個(gè)調(diào)用lpm中三態(tài)電路模塊的VHDL程序,這個(gè)程序會(huì)出現(xiàn)編譯不能通過(guò)的問(wèn)題。然后從這個(gè)問(wèn)題出發(fā),通過(guò)嘗試三態(tài)電

2010-08-06 16:56:22 27

27

27

27三態(tài)門:計(jì)算機(jī)的邏輯部件

三態(tài)門:計(jì)算機(jī)的邏輯部件

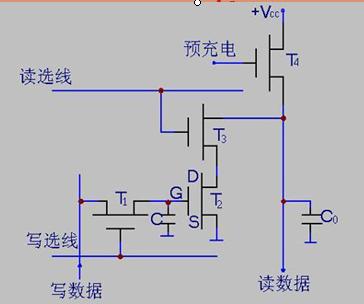

常用的集成門電路器件分為兩大類:CMOS和TTL。 CMOS是由單極型場(chǎng)效應(yīng)三極管組成集成電路, TTL是晶體管-晶體管邏輯電路

2010-04-15 14:55:00 1685

1685

1685

1685集電極開路門和三態(tài)輸出門的應(yīng)用

集電極開路門和三態(tài)輸出門的應(yīng)用

一、 實(shí)訓(xùn)目的1.熟悉集電極開路門(OC門)和三態(tài)輸出門(TSL門)的邏輯功能;2.熟悉用OC門構(gòu)成線與功能;3.熟悉用TSL門

2009-04-07 23:23:53 59

59

59

59三態(tài)與非門(TSL)

三態(tài)與非門(TSL)

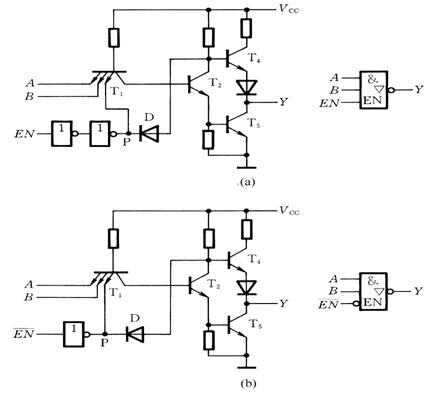

利用OC門雖然可以實(shí)現(xiàn)線與的功能,但外接電阻Rp的選擇要受到一定的限制而不能取得太小,因此影響了工作速度。

2009-04-07 00:15:37 7965

7965

7965

7965

TTL或非門、集電極開路門和三態(tài)門電路

TTL或非門、集電極開路門和三態(tài)門電路

1.TTL或非門

下圖為TTL或非門的邏輯電路及其代表符號(hào)。

2009-04-07 00:11:59 13667

13667

13667

13667

什么是三態(tài)門? 三態(tài)邏輯與非門電路以及三態(tài)門電路

什么是三態(tài)門?

三態(tài)門,是指邏輯門的輸出除有高、低電平兩種狀態(tài)外,還有第三種狀態(tài)——高阻狀態(tài)的門電路 高阻態(tài)相當(dāng)于隔斷狀態(tài)。

2008-05-26 12:48:24 41856

41856

41856

41856

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論