在現(xiàn)代電子系統(tǒng)的核心組件中,內(nèi)存的性能與穩(wěn)定性至關重要。高密度DDR4芯片作為當前內(nèi)存技術(shù)的杰出代表,不僅憑借其卓越的性能表現(xiàn)和微型化技術(shù)贏得了廣泛認可,還在多個方面展現(xiàn)出了獨特的優(yōu)勢。

2024-03-22 14:47:42 17

17

中國上海,2024 年 3 月 22 日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)推出業(yè)界首個全面的 AI 驅(qū)動數(shù)字孿生解決方案,旨在促進數(shù)據(jù)中心的可持續(xù)發(fā)展及現(xiàn)代化的設計,標志著在優(yōu)化數(shù)據(jù)中心能效和運營能力方面取得了重大飛躍。

2024-03-22 11:38:05 201

201 新思科技(Synopsys)日前重磅推出了業(yè)界首個1.6T以太網(wǎng)IP整體解決方案,這一創(chuàng)新性的方案在數(shù)據(jù)密集型人工智能(AI)工作負載的處理上,顯著提升了帶寬和吞吐量,為行業(yè)樹立了新的技術(shù)標桿。

2024-03-19 10:24:59 86

86 新思科技1.6T以太網(wǎng)IP整體解決方案現(xiàn)已上市并被多家客戶用,與現(xiàn)有實現(xiàn)方案相比,其互連功耗最多可降低50%

2024-03-19 10:23:06 96

96 全球電子設計自動化和半導體IP解決方案的領先企業(yè)楷登電子(Cadence)近日宣布,其進一步擴展了Tensilica IP產(chǎn)品系列,以滿足汽車行業(yè)中日益增長的傳感器融合應用計算需求。新推出

2024-03-14 11:38:29 314

314 電子發(fā)燒友網(wǎng)站提供《完整的DDR2、DDR3和DDR3L內(nèi)存電源解決方案同步降壓控制器TPS51216數(shù)據(jù)表.pdf》資料免費下載

2024-03-13 13:58:12 0

0 電子發(fā)燒友網(wǎng)站提供《適用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF緩沖基準的TPS51206 2A峰值灌電流/拉電流DDR終端穩(wěn)壓器數(shù)據(jù)表.pdf》資料免費下載

2024-03-13 13:53:03 0

0 電子發(fā)燒友網(wǎng)站提供《具有同步降壓控制器、2A LDO和緩沖基準的TPS51916完整DDR2、DDR3、DDR3L和DDR4存儲器電源解決方案數(shù)據(jù)表.pdf》資料免費下載

2024-03-13 11:24:34 0

0 電子發(fā)燒友網(wǎng)站提供《具有同步降壓控制器、2A LDO和緩沖基準的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4內(nèi)存電源解決方案數(shù)據(jù)表.pdf》資料免費下載

2024-03-13 11:13:44 0

0 電子發(fā)燒友網(wǎng)站提供《完整的DDR、DDR2和DDR3內(nèi)存電源解決方案同步降壓控制器數(shù)據(jù)表.pdf》資料免費下載

2024-03-13 10:16:45 0

0 電子發(fā)燒友網(wǎng)站提供《TPS65295完整 DDR4 存儲器電源解決方案數(shù)據(jù)表.pdf》資料免費下載

2024-03-06 10:17:54 0

0 Autotalks 作為V2X通信解決方案的全球領導者,依托羅德與施瓦茨(以下簡稱“R&S”)的專業(yè)測試技術(shù)和設備,驗證了其第三代V2X 芯片組的性能。

2024-02-28 18:27:20 938

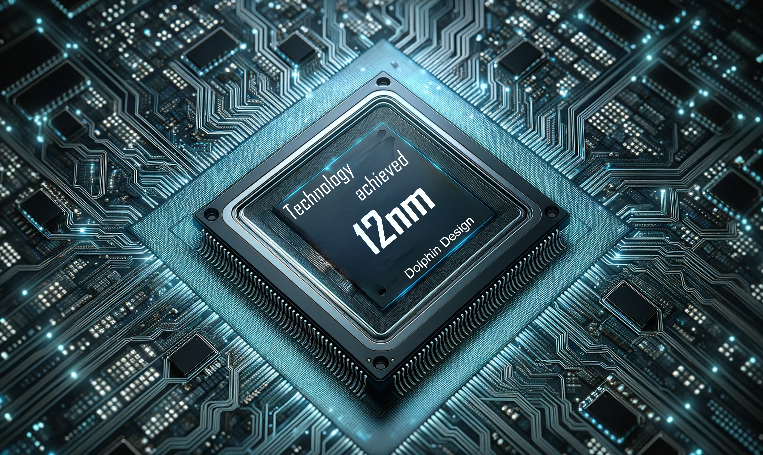

938 且值此具有歷史意義的時刻,位于法國格勒諾布爾的行業(yè)領軍企業(yè)Dolphin Design,已于近期成功流片首款內(nèi)置先進音頻IP的12 nm FinFET測試芯片,這無疑是公司發(fā)展路上一座新的里程碑。

2024-02-22 15:53:11 172

172 這款測試芯片是業(yè)界首款采用12納米FinFet(FF)技術(shù)為音頻IP提供完整解決方案的產(chǎn)品。該芯片完美結(jié)合了高性能、低功耗和優(yōu)化的占板面積,為電池供電應用提供卓越的音質(zhì)與功能。這款專用測試芯片通過

2024-02-22 14:46:18 523

523

楷登電子(Cadence Design Systems)今日宣布推出了一款業(yè)界領先的產(chǎn)品——Cadence? Celsius? Studio。這款產(chǎn)品是業(yè)內(nèi)首個完整的用于電子系統(tǒng)的AI散熱設計和分析解決方案,專為滿足現(xiàn)代電子設計中日益復雜的散熱需求而打造。

2024-02-03 11:32:27 543

543 高精度納米級壓電位移平臺“PIEZOCONCEPT”半導體界后摩爾時代的手術(shù)刀!第三代半導體是后摩爾時代實現(xiàn)芯片性能突破的核心技術(shù)之一,優(yōu)越性能和廣泛的下游應用使相關廠商存在良好發(fā)展前景。隨著下

2024-01-26 08:16:17 162

162

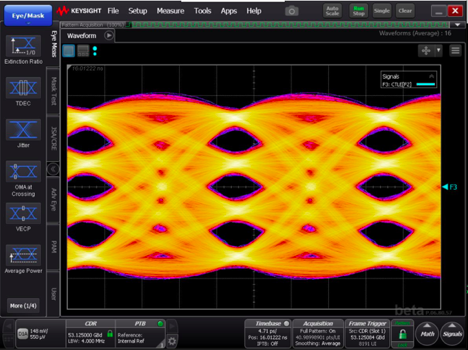

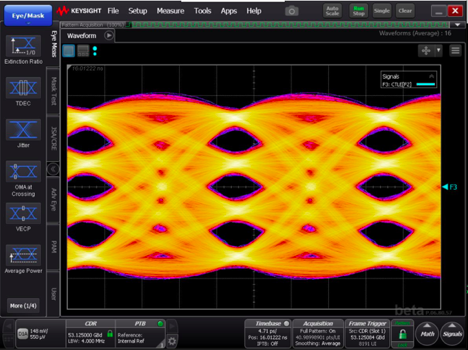

DDR5已經(jīng)開始商用,但是有的產(chǎn)品還才開始使用DDR4。本文分享一些DDR4的測試內(nèi)容。DDR4 和前代的 DDR3 相比, 它的速度大幅提升,最高可以達到 3200Mb/s,這樣高速的信號,對信號完整性的要求就更加嚴格,JESD79‐4 規(guī)范也對 DDR4 信號的測量提出了一些要求。

2024-01-08 09:18:24 463

463

ASIC設計服務暨IP研發(fā)銷售廠商智原科技(Faraday Technology Corporation,TWSE:3035)提供完整的FinFET 14納米ASIC整合設計開發(fā)服務,搭配SoC驗證平臺與高速傳輸IP解決方案

2023-12-26 18:20:56 356

356 )

DDR3內(nèi)存條,240引腳(120針對每側(cè))

DDR4內(nèi)存條,288引腳(144針對每側(cè))

DDR5內(nèi)存條,288引腳(144針對每側(cè))

DDR芯片引腳功能如下圖所示:

DDR數(shù)據(jù)線的分組

2023-12-25 14:02:58

PCB的DDR4布線指南和PCB的架構(gòu)改進

2023-12-07 15:15:58 753

753 完整的電源解決方案。得益于 IP5316 的高集成度與豐富功能,使其在應用時僅需極少的外圍器件,并有效減小整體方案的尺寸,降低 BOM 成本。IP5316 只需一個電感即可實現(xiàn)降壓與升壓功能。可以支持

2023-12-05 09:28:42

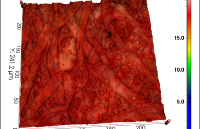

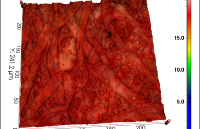

中圖儀器SuperViewW3d光學輪廓儀以白光干涉技術(shù)原理,對各種精密器件表面進行納米級測量的儀器,通過測量干涉條紋的變化來測量表面三維形貌,專用于精密零部件之重點部位表面粗糙度、微小形貌輪廓

2023-11-20 11:46:25

新思科技加入“Arm全面設計”(Arm Total Design)生態(tài)系統(tǒng)并提供IP和芯片設計服務,通過Synopsys.ai全棧式AI驅(qū)動型EDA全面解決方案和硬件輔助驗證產(chǎn)品組合降低定制SoC

2023-11-17 09:24:09 384

384 DDR4和DDR3內(nèi)存都有哪些區(qū)別? 隨著計算機的日益發(fā)展,內(nèi)存也越來越重要。DDR3和DDR4是兩種用于計算機內(nèi)存的標準。隨著DDR4內(nèi)存的逐漸普及,更多的人開始對兩者有了更多的關注。 DDR

2023-10-30 09:22:00 3885

3885 雙方的共同客戶可獲取 Cadence 的全流程系統(tǒng)級設計驗證和實現(xiàn)解決方案以及接口 IP,依托 Neoverse CSS 加速開發(fā)基于 Arm 的定制 SoC 中國上海,2023 年 10 月 25

2023-10-25 10:40:02 196

196

電子設計自動化領域領先的供應商 Cadence,誠邀您參加“2023 Cadence 中國技術(shù)巡回研討會”。會議將集聚 Cadence 的開發(fā)者與資深技術(shù)專家,與您分享系統(tǒng)驗證及 IC 驗證解決方案

2023-10-25 10:40:02 185

185

設計基礎架構(gòu)、3Dblox 設計原型驗證解決方案、毫米波設計解決方案和 DSP IP 方面取得的出色成果。Cadence 和 TSMC 的合作由來已久并且頗有成果,二者共同向全球市場推出了許多極具創(chuàng)新性的

2023-10-23 11:55:02 378

378

電子設計自動化領域領先的供應商 Cadence,誠邀您參加“2023 Cadence 中國技術(shù)巡回研討會”。會議將集聚 Cadence 的開發(fā)者與資深技術(shù)專家,與您分享系統(tǒng)驗證及 IC 驗證解決方案

2023-10-23 11:55:02 287

287

納米科技的迅猛發(fā)展將我們的視野拓展到了微觀世界,而測量納米級尺寸的物體和現(xiàn)象則成為了時下熱門的研究領域。納米級測量儀器作為一種重要的工具,扮演著重要的角色。那么,如何才能準確測量納米級物體

2023-10-12 09:12:16 1

1 在納米級測量中,由于物體尺寸的相對較小,傳統(tǒng)的測量儀器往往無法滿足精確的要求。而納米級測量儀器具備高精度、高分辨率和非破壞性的特點,可以測量微小的尺寸。納米級測量儀器在納米科技研究領域中扮演著重要的角色。通過共聚焦顯微鏡、光學輪廓儀等的運用,科研人員們能夠更加深入地了解納米世界的奧秘。

2023-10-11 15:23:16 0

0 納米科技的迅猛發(fā)展將我們的視野拓展到了微觀世界,而測量納米級尺寸的物體和現(xiàn)象則成為了時下熱門的研究領域。納米級測量儀器作為一種重要的工具,扮演著重要的角色。那么,如何才能準確測量納米級物體呢?在

2023-10-11 14:37:46

納米科技的迅猛發(fā)展將我們的視野拓展到了微觀世界,而測量納米級尺寸的物體和現(xiàn)象則成為了時下熱門的研究領域。納米級測量儀器作為一種重要的工具,扮演著重要的角色。那么,如何才能準確測量納米級物體呢?在

2023-10-11 13:49:37

納米級測量儀器在納米科技研究領域中扮演著重要的角色。通過共聚焦顯微鏡、光學輪廓儀等的運用,科研人員們能夠更加深入地了解納米世界的奧秘。

2023-10-09 15:42:08 292

292

做高速鏈路的小伙伴都知道,Stub總是會帶來各種影響,或者導致阻抗突變,或者導致插入損耗曲線上存在諧振,等等。本文介紹了Via stub在DDR4并行鏈路上的表現(xiàn)。下面是論文的全文。

2023-10-09 10:35:30 321

321

電子發(fā)燒友網(wǎng)站提供《如何在STM32F10xxx上得到最佳的ADC精度.pdf》資料免費下載

2023-10-07 14:46:02 13

13 摘要:本文將對DDR3和DDR4兩種內(nèi)存技術(shù)進行詳細的比較,分析它們的技術(shù)特性、性能差異以及適用場景。通過對比這兩種內(nèi)存技術(shù),為讀者在購買和使用內(nèi)存產(chǎn)品時提供參考依據(jù)。

2023-09-27 17:42:10 1088

1088 DDR4 3200和3600是內(nèi)存模塊的頻率標準,表示其頻率值,具有以下差異

2023-09-26 15:24:18 8974

8974 解決方案,并與技術(shù)專家們面對面直接溝通交流。Cadence 期待您的參與! Cadence 將在 北京 、 成都 、 西安 開展線下研討會,您可以自由選擇您所在城市或就近城市報名參加 系統(tǒng)驗證及 IC

2023-09-21 17:20:02 338

338

相對于DDR3, DDR4首先在外表上就有一些變化,比如DDR4將內(nèi)存下部設計為中間稍微突出,邊緣變矮的形狀,在中央的高點和兩端的低點以平滑曲線過渡,這樣的設計可以保證金手指和內(nèi)存插槽有足夠的接觸面

2023-09-19 14:49:44 1481

1481

三星公司計劃在下半年再次削減DRAM制程的產(chǎn)能,而今年以來這一減產(chǎn)主要針對DDR4。業(yè)界普遍預期,三星的目標是在今年年底之前將庫存水平降至合理水平。這一減產(chǎn)舉措可能會導致DDR4市場價格上漲,而目前

2023-09-15 17:42:08 996

996 隨著英特爾和amd將新的pc/筆記本電腦和服務器平臺更換為ddr4, ddr4的需求開始減少。因此,三星大幅減少ddr4的生產(chǎn),轉(zhuǎn)向ddr5,試圖鞏固業(yè)界第一的位置。

2023-09-15 11:40:33 555

555 電子發(fā)燒友網(wǎng)站提供《Teledyne e2v的宇航級DDR4的硬件設計指南.pdf》資料免費下載

2023-09-13 17:14:55 1

1 和存儲器接口 PHY IP 業(yè)務。 隨著人工智能、數(shù)據(jù)中心和超大規(guī)模應用、CPU 架構(gòu)和網(wǎng)絡設備日新月異的發(fā)展,此次技術(shù)資產(chǎn)收購豐富了 Cadence 現(xiàn)有的 IP 組合,并增強了公司的智能系統(tǒng)

2023-09-12 10:10:03 298

298

基于VU440T的多核處理器多輸入芯片驗證板卡

一、板卡概述

基于XCVU440-FLGA2892的多核處理器多輸入芯片驗證板卡為實現(xiàn)網(wǎng)絡交換芯片的驗證,包括四個FMC接口、DDR、GPIO等

2023-09-08 15:07:12

是面向汽車Qi充電器的整體式安全解決方案,符合Qi WPC 1.3規(guī)范。它內(nèi)嵌在Qi充電器中,鑒別真正獲得Qi認證的充電器,從而確保用戶安全并保護設備免受任何由非認證無線充電器造成的損害。STSAFE-V110是高度安全的身份驗證解決方案,其安全性獲得獨立第三方的通用標準EAL4+認證。

2023-09-08 07:01:38

關節(jié)模組伺服驅(qū)動基于STM32G4解決方案的優(yōu)勢 ? STM32G4芯片體積9X9 mm ? 內(nèi)嵌MOS管前級驅(qū)動,省去外部3個驅(qū)動芯片PCB布局 ? 完全滿足高性能伺服驅(qū)動控制主芯片資源 ? 低成本

2023-09-06 08:06:24

芯片為啥不能低于1納米 芯片可以突破1納米嗎? 從計算機發(fā)明以來,芯片技術(shù)已經(jīng)有了數(shù)十年的發(fā)展,從最初的晶體管到如今的微米級或納米級芯片,一直在不斷地創(chuàng)新。現(xiàn)在,隨著計算機技術(shù)的日益發(fā)展,芯片的尺寸

2023-08-31 10:48:31 3374

3374 基于XCVU440-FLGA2892的多核處理器多輸入芯片驗證板卡為實現(xiàn)網(wǎng)絡交換芯片的驗證,包括四個FMC接口、DDR、GPIO等,板卡用于完成甲方的芯片驗證任務,多任務功能驗證。

2023-08-24 10:58:23 475

475

DDR4 3200和DDR4 3600是兩種常見的內(nèi)存頻率規(guī)格,它們在性能上會有一定的差別,但差別大小取決于具體的應用場景和系統(tǒng)配置。

2023-08-22 14:45:05 28253

28253 PH1A100是否支持DDR3,DDR4

2023-08-11 06:47:32

使用DDR4作為外接存儲單元時,蜂鳥e203的訪問地址為0x40000000,但是經(jīng)過vivado的Block design后使用DDR4,在板子上跑測試DDR4讀寫程序,報store訪問異常

2023-08-11 06:17:58

DDR5的主板不支持使用DDR4內(nèi)存。DDR5(第五代雙倍數(shù)據(jù)率)和DDR4(第四代雙倍數(shù)據(jù)率)是兩種不同規(guī)格的內(nèi)存技術(shù),它們在電氣特性和引腳布局上存在明顯差異。因此,DDR5內(nèi)存模塊無法插入DDR4主板插槽中,也不兼容DDR4內(nèi)存控制器。

2023-08-09 15:36:25 12794

12794 SBC ,最近推出的基于 Raspberry Pi CM4 的 KVM over IP 解決方案的價格低于 200 美元。看到這些解決方案的受歡迎程度,Banana Pi 決定加入競爭,推出

2023-07-29 12:37:34

中國上海,2023 年 7 月 28 日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布,雙方已就 Cadence 收購 Rambus SerDes 和存儲器接口 PHY

2023-07-28 17:11:51 988

988 基于XCVU440-FLGA2892的多核處理器多輸入芯片驗證板卡為實現(xiàn)網(wǎng)絡交換芯片的驗證,包括四個FMC接口、DDR、GPIO等,板卡用于完成甲方的芯片驗證任務,多任務功能驗證。

2023-07-25 14:17:35 400

400

電子發(fā)燒友網(wǎng)站提供《PI2DDR3212和PI3DDR4212在DDR3/DDR4中應用.pdf》資料免費下載

2023-07-24 09:50:47 0

0 推出 Cadence ?Joules RTL Design Studi o,這款新的解決方案可為用戶提供實用的洞察,有助于加快寄存器傳輸級(RTL)設計和實現(xiàn)流程。 前端設計人員可以在一個統(tǒng)一的界面使用數(shù)

2023-07-17 10:10:01 492

492

DDR是Double Data Rate的縮寫,即“雙倍速率同步動態(tài)隨機存儲器”。DDR是一種技術(shù),中國大陸工程師習慣用DDR稱呼用了DDR技術(shù)的SDRAM,而在中國臺灣以及歐美,工程師習慣用DRAM來稱呼。

2023-07-16 15:27:10 3362

3362

內(nèi)容提要 ● ?Cadence 流程已通過認證,可立即投入生產(chǎn),該工藝下 Design IP 產(chǎn)品現(xiàn)已完備,可支持客戶進行 Intel 16 工藝下 SOC 設計 ● ? 客戶可以基于已被充分認證

2023-07-14 12:50:02 381

381

近日,泛林集團 (Nasdaq: LRCX) 推出了Coronus DX產(chǎn)品,這是業(yè)界首個晶圓邊緣沉積解決方案,旨在更好地應對下一代邏輯、3D NAND和先進封裝應用中的關鍵制造挑戰(zhàn)。隨著半導體芯片

2023-07-05 00:39:29 422

422 RF IP 解決方案提供商 Sirius Wireless 的 Wi-Fi6/BT 射頻 IP 驗證系統(tǒng)已被廣泛應用,該系統(tǒng)是基于思爾芯的原型驗證 EDA 工具搭建而成。

2023-06-29 10:23:42 257

257 近日,泛林集團推出了Coronus DX產(chǎn)品,這是業(yè)界首個晶圓邊緣沉積解決方案,旨在更好地應對下一代邏輯、3D NAND和先進封裝應用中的關鍵制造挑戰(zhàn)。隨著半導體芯片關鍵尺寸的不斷縮小,其制造變得

2023-06-29 10:08:27 650

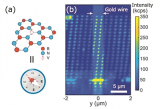

650 日本東京大學科學家利用六方氮化硼二維層中的硼空位,首次完成了在納米級排列量子傳感器的精細任務,從而能夠檢測磁場中的極小變化,實現(xiàn)了高分辨率磁場成像。

2023-06-28 09:23:20 164

164

和混合信號 IP,與現(xiàn)有流程相比,在達到所需精度的同時,可幫助提升 2 倍性能。 Cadence 的這款解決方案助力 DB GlobalChip 加速了 IP 開發(fā)和驗證周期,可以更快將產(chǎn)品推向市場。 在客戶規(guī)定的時間內(nèi)滿足模擬和混

2023-06-25 12:25:02 512

512 高級存儲器接口 IP 解決方案擴展到 SF3 并支持具有豐富接口協(xié)議的完整 SF5A 設計 IP 組合 中國上海,2023 年 6 月 16 日——楷登電子(美國 Cadence 公司,NASDAQ

2023-06-16 12:15:06 412

412

電子設計自動化領域領先的供應商 Cadence,誠邀您參加 “2023 CadenceCONNECT:HPC 芯片全流程驗證解決方案” 線下研討會北京站。 會議將聚焦提供業(yè)界領先的虛擬云計算、快速

2023-06-12 14:15:01 368

368

新思科技系統(tǒng)級全方位解決方案涵蓋了設計、驗證、芯片生命周期管理和IP,可提供業(yè)界領先的性能和能效 Synopsys.ai全棧式人工智能驅(qū)動型EDA解決方案和新思科技Fusion Compiler

2023-06-07 01:50:02 366

366

2023 年 6 月 2 日—3 日,Cadence 受邀出席了第七屆集微半導體峰會。在首日舉辦的 EDA IP 工業(yè)軟件峰會中,Cadence 高級 AE 經(jīng)理王正算作為代表向與會嘉賓介紹

2023-06-07 00:20:03 466

466

連接到電路板。在 DDR 配置窗口中,我選擇“從目標讀取”選項。看起來某些通信有效,并且填充了具有非默認參數(shù)的屬性窗口。

但是現(xiàn)在,如果我運行驗證頁面,我永遠不會通過測試(自動搜索和檢測 VREF 或

2023-06-05 08:12:06

? 內(nèi)容提要: 新推出的 Arm TCS23 和 Cadence 工具為芯片流片提供了捷徑 Cadence 對其 RTL-to-GDS 數(shù)字流程進行了精細優(yōu)化,為 Arm Cortex-X4

2023-06-03 09:44:22 329

329 思爾芯(S2C)近日宣布,公司的系統(tǒng)級驗證原型驗證解決方案獲得了較為全面的正向市場反饋,成功協(xié)助多家設計企業(yè)完成低功耗藍牙音頻(BLE Audio)領域的IP/藍牙SoC定制方案設計。

2023-05-30 15:52:52 401

401 MES50HP 開發(fā)板簡介

MES50HP 開發(fā)板集成兩顆 4Gbit(512MB)DDR3 芯片,型號為 MT41K256M16。DDR3 的總線寬度共為 32bit。DDR3 SDRAM 的最高

2023-05-19 14:28:45

我在導入一個示例后安裝了s32design studio,我在項目上得到了紅叉,這可能是什么問題,以及我該如何解決這個問題,請觀察下面標記的錯誤,它顯示為描述資源路徑位置類型當前

版本不再支持工具鏈

2023-05-18 06:24:08

目前,用于制造具有復雜形狀的納米級物體的最精確的3D打印技術(shù)可能是雙光子光刻。這種方法依賴于液態(tài)樹脂,只有當它們同時吸收兩個光子而不是一個光子時,它們才會固化。這使得能夠精確制造具有體素(相當于像素的3D)的物體,尺寸只有幾十納米。

2023-05-17 09:59:22 661

661

我有一塊自制的imx8mp主板,使用DDR4的型號是:K4ABG165WA-MCWE,單片容量32Gb,主頻3200Mhz,我的主板使用了兩顆芯片,但是使用MX8M_Plus_DDR4_RPA_v9.xlsx無法完成配置

2023-05-17 06:12:25

DDR4內(nèi)存模塊支持單個64位通道(如果考慮ECC,則為72位通道)。相比之下,DDR5內(nèi)存模塊配備了兩個獨立的32位通道(40位ECC)。

2023-05-08 10:27:44 1331

1331 思爾芯(S2C)近日宣布,公司的系統(tǒng)級驗證原型驗證解決方案獲得了較為全面的正向市場反饋,成功協(xié)助多家設計企業(yè)完成低功耗藍牙音頻(BLEAudio)領域的IP/藍牙SoC定制方案設計。萬物互聯(lián)時代開啟

2023-05-08 09:29:37 274

274

/MCK0_B) 感到有點困惑。

在上一代相同的主板上,啟動并運行不同的 DDR4 內(nèi)存,我們可以按預期測量 DDR 時鐘。

我們了解 NXP 是否無法支持特定的內(nèi)存配置,但我們想知道在 LS1046A

2023-05-06 08:20:49

免費的 I3C 從屬 IP 芯片是否經(jīng)過驗證?

2023-05-05 07:16:21

來源:Cadence楷登 2023年4月26日,楷登電子近日宣布基于臺積電 3nm(N3E)工藝技術(shù)的 Cadence? 16G UCIe? 2.5D 先進封裝 IP 成功流片。該 IP 采用

2023-04-27 16:35:40 452

452

我有 LS1046AFRWY 板的克隆。高速公路板使用 MT40A512M16JY-083E:B(商業(yè)級DDR4)。我的克隆使用 MT40A512M16JY-083E IT:B(工業(yè)級 DDR4

2023-04-24 08:08:20

白光干涉儀和激光共聚焦顯微鏡同為微納米級表面光學分析儀器,都具有非接觸式、高速度測量、高穩(wěn)定性的特點,都有表征微觀形貌的輪廓尺寸測量功能,適用范圍廣,可測多種類型樣品的表面微細結(jié)構(gòu)

2023-04-20 14:38:43 1595

1595

將 DDR4 內(nèi)存添加到 imx8mp

2023-04-20 10:59:17

NXP IMX8M Mini DDR4 校準

2023-04-20 07:36:55

電容器............................................. 41.5 速度補償.....................................52 DDR4

2023-04-14 17:03:27

2 組 64bit 的DDR4 SDRAM,每組容量2GB,可穩(wěn)定運行在2400MT/s。支持PCIE Gen3 x8模式及一路FMC HPC接口。同時可提供 Windows,Linux 上位機驅(qū)動

2023-04-13 15:56:21

技術(shù)很快將難以滿足質(zhì)量和上市時間的要求。通過新思科技VCS(Synopsys.ai解決方案的組成部分)的AI驅(qū)動型驗證,我們在減少功能覆蓋盲區(qū)方面實現(xiàn)了高達10倍的優(yōu)化,并將IP驗證效率提高了30

2023-04-03 16:03:26

你能告訴我在哪里可以獲得 i.MX8M Plus 的詳細 DDR4 布局跟蹤路由指南嗎?我在 i.MX8M Plus 硬件開發(fā)人員指南中找不到它。順便問一下,NXP 有帶 DDR4 的 i.MX8M Plus 評估板嗎?

2023-03-31 07:52:02

PROSLIC?單芯片FXS解決方案

2023-03-25 02:23:12

你好 我們正在使用 4 * 2GB DDR4 芯片構(gòu)建我們的定制 ls1046a 板。(我們參考LS1046AFRWY,容量翻倍,去掉ECC)首先我生成了 BL2 二進制文件制作 PLAT

2023-03-24 08:50:43

電子發(fā)燒友App

電子發(fā)燒友App

評論