摘 要:單載波頻域均衡(SC-FDE)是數字通信中克服多徑衰落的有效技術。寬帶通信系統中應用單載波頻域均衡系統設計,實現137.5 MHz 載波下27.5 Mbps 的碼元傳輸速率。同時在系統中添加1/2 碼率卷積碼與(239,223)里德-所羅門(RS)碼的級聯信道糾錯編碼,提高系統的可靠性。完成單載波頻域均衡系統設計,分析設計系統的關鍵技術,最終在現場可編程門陣列硬件平臺上進行系統實現、調試和驗證,完成系統實際誤碼率的測試。

?

在現代無線數字通信系統中,信號的傳輸從窄帶變?yōu)閷拵В鴮拵?a href="http://www.asorrir.com/v/tag/1252/" target="_blank">無線通信的信道是頻率選擇性衰落的多徑信道。多徑效應引起的時延擴展導致嚴重的符號間干擾(Inter Symbol Interference,ISI),嚴重影響通信的可靠性,因此需要采用一種有效的方法抵抗信道的影響[1]。目前提出的方法主要有:單載波時域均衡(Single Carrier Time Domain Equalization,SC-TDE)、單載波頻域均衡(Single Carrier Frequency Domain Equalization,SC-FDE)和正交頻分復用(Orthogonal Frequency Division Multiplexing,OFDM)技術。SC-TDE 在接收端采用一個自適應均衡器來補償符號間干擾[2]。它的主要部件就是一個或多個橫向濾波器,而橫向濾波器抽頭系數的數目由多徑時延來確定。在高速無線通信系統中較大的時延會導致復雜度很高。3GPP(3rd Generation Partnership Project)的長期演進計劃中,提出了上行采用單載波技術,下行采用OFDM 技術的方案。

OFDM 系統在發(fā)射端通過快速傅里葉逆變換(Inverse Fast Fourier Transform,IFFT)將數據符號并行調制到正交的子載波上,克服了頻率選擇性衰落造成的影響,在頻域實現均衡。其頻譜利用率高,系統復雜度較低(與信道最大時延擴展的對數成正比),但是它對定時誤差和載波同步敏感,且每個OFDM 符號的多路子載波在時域疊加會產生很大的峰值平均功率比,因而對射頻前端的要求較高。SC-FDE 技術綜合了OFDM 技術和單載波傳輸的優(yōu)點[3-5],同時文獻[6]分析指出對于一般的SC-FDE 和OFDM 系統,在低信噪比下OFDM 系統的誤碼性能略優(yōu)于SC-FDE 系統,而在高信噪比下,SC-FDE 系統要優(yōu)于OFDM 系統。本文設計的系統可以實現137.5 MHz 載波下的27.5 Mbps 碼元傳輸速率,實現了寬帶SC-FDE 系統。

1 系統設計

1.1 SC-FDE 系統模型

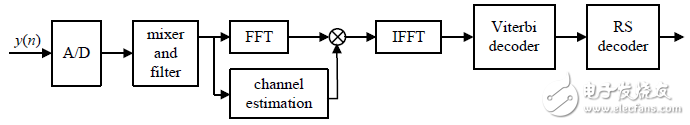

在傳統的單載波系統中,接收機主要由A/D 變換、混頻濾波、信道估計、信道均衡等模塊組成[7-8]。本文在單載波頻域均衡傳輸系統中添加了信道編譯碼模塊,以獲得更好的誤碼率性能。系統采用的是1/2 碼率的卷積碼和RS 碼級聯的方案。為提高系統的傳輸速率,使用了正交相移鍵控(Quadrature Phase Shift Keying,QPSK)的調制方式,系統框圖見圖1。

圖1 SC-FDE 系統框圖

1.2 系統幀結構

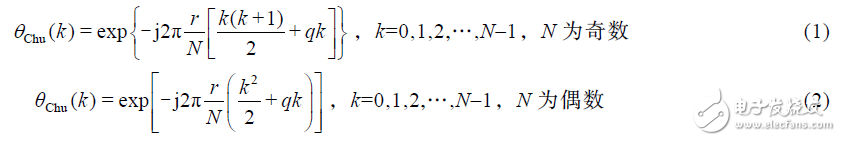

單載波頻域均衡系統中使用的數據幀結構是基于獨特字(Unique Word,UW)的幀結構,接收端使用UW 完成幀同步、信道估計、循環(huán)前綴的功能。而作為UW 的序列應該滿足在時域上和頻域上均具有較小的起伏。常用的UW 字有Newsman 序列、Frank-Zadoff 序列等。本文使用的是偽疊加序列(Zadoff-Chu)序列,其定義為:

式中:N 表示序列長度;r 是與N 互質的正整數;q 取任意值。

Zadoff-Chu 序列的算法在各種信道環(huán)境下的性能都很優(yōu)越,Zadoff-Chu 序列具有良好的周期自相關和互相關特性,其幅值恒定,并且具有傅里葉變換保持特性。

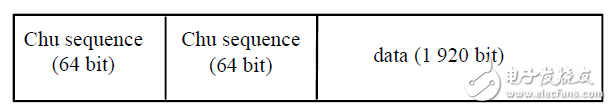

系統傳輸幀由2 個完全相同的64 位Zadoff-Chu 序列和1 920 個數據位構成,見圖2。每一幀起始位置的2 段Zadoff-Chu序列用來充當循環(huán)前綴,完成幀同步、信道估計、噪聲估計等功能。數據幀連續(xù)傳輸[9]。

圖2 系統幀結構

圖3 三態(tài)同步圖示

2 寬帶單載波頻域均衡系統中關鍵技術

2.1 幀同步與頻偏估計

本設計利用UW 完成幀同步,對接收到的每一幀頭部的2 段64 位Zadoff-Chu 序列與本地的Zadoff-Chu 序列做相關運算,由于序列自相關特性,會得到一對相關峰(理想情況)或一對主峰和若干對副峰(存在多徑)。根據相關峰完成峰值搜索,最終完成信號幀同步[10]。

幀同步采用有限狀態(tài)機設計完成。狀態(tài)機的實現采用了基于搜索態(tài)-同步態(tài)-保護態(tài)的三態(tài)同步機制,見圖3。

頻偏估計同樣采用搜索到的相關峰來完成,假設載波頻偏為Δf,每幀有N 個符號,每個符號的周期為T。設當前幀的主相關峰為p(n),前一幀的主相關峰為p(n–1),則2 個主峰的相位差滿足:

式中:Δφ 表示相位差;arctan 表示取反正切角; p*表示取 p 的共軛值。

載波的頻偏為:

式中:Re[]表示取復數的實部;Im[]表示取復數的虛部。

由于相偏相對較小,實際設計中可以只使用虛部完成計算,以降低復雜度。設計幀長度為2 048 位,故采用本方法所能糾正的最大頻偏為:

。

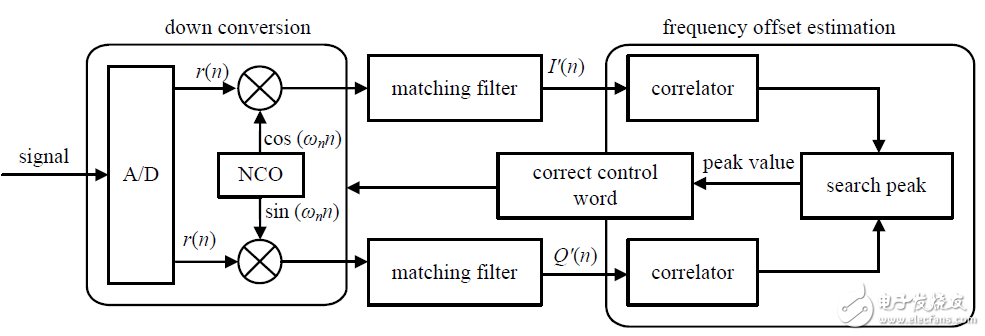

同步與頻偏估計的實現框圖見圖4。

圖4 同步與頻偏估計

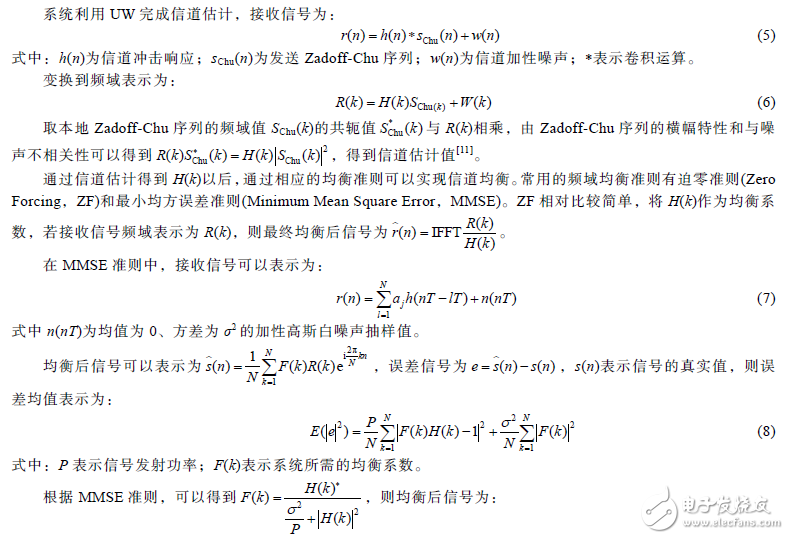

2.2 信道估計和均衡

3 FPGA 實現與測試

3.1 FPGA 實現

系統在XILINX 的xc4vlx160 上完成設計驗證、調試和實際測試。系統實際測試見圖5,一臺電腦與安捷倫E4438C 相連接,通過matlab 設計發(fā)射機控制矢量信號發(fā)生器產生發(fā)射波形。發(fā)射機設計載波頻率為137.5 MHz,符號速率為27.5 Mbps,系統采用QPSK 調制來增加傳信率。信道編碼模塊使用碼率為1/2 的卷積碼與(239,223)RS碼級聯的方式。E4438C 的RF 端口連接到硬件平臺的ADC 接口,通過示波器和另一臺電腦上安裝的chipscope觀測接收機的各項信息,完成驗證和測試。系統接收機主要由以下幾部分構成:模擬前端、頻偏估計、幀同步、頻域信道估計和均衡、信道譯碼。

圖5 系統實際測試

圖6 頻域信道估計和均衡

頻域信道估計和均衡是系統中較復雜的部分,涉及到FFT、IFFT、除法器、乘法器、RAM、ROM 等XILINX IP 核。硬件實現結構見圖6。均衡時,需要對接收幀做2 048 點的FFT 和IFFT,這導致系統硬件開銷和時間開銷很大,難以滿足實時處理的要求,因此采用乒乓操作的結構,配置FFT 核為基4 突發(fā)模式。此舉雖然增加了硬件開銷,但能夠滿足處理的時間需求。此外,鑒于除法器的硬件開銷很大,在設計上使用查找表的方法將除法器轉化為ROM+乘法器的結構來節(jié)省資源。

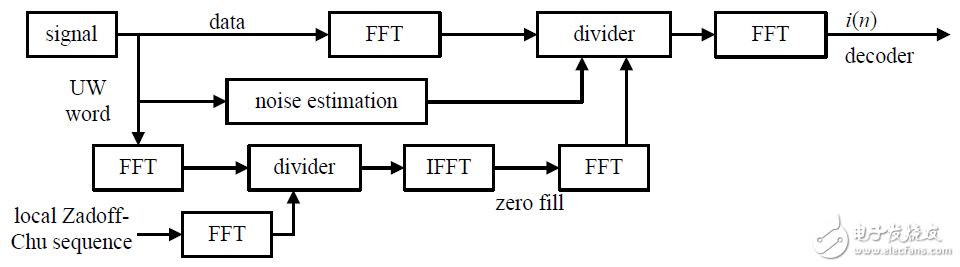

在多徑能量–3 dB、延時30 個符號的信道條件下均衡前后實際系統星座圖對比如圖7(a)和圖7(b)。圖中能明顯看出均衡后信號的星座點匯聚成4 個點。

圖7 均衡前后星座圖對比

經過信道均衡后的數據已經可以作為接收數據,但為了獲得更高的系統性能,均衡后的數據還要經過信道譯碼模塊。系統設計實現了Viterbi 譯碼器和GF(28)域中任意長度下糾正8 或4 個錯誤的RS 譯碼器,本文不再詳細介紹。

3.2 測試結果

系統在硬件平臺上完成實測驗證,使用Agilent E4438C 信號源獲得發(fā)射信號,發(fā)射波形由matlab 編寫配置文件來完成,接收端設計誤碼率統計模塊統計系統性能。系統共占用FPGA 資源40 344 個Slice,占總量的29%。

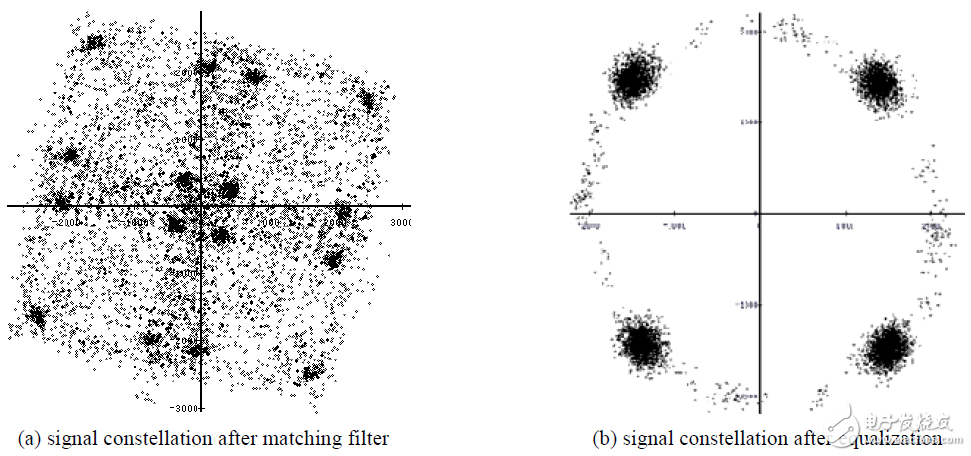

測試環(huán)境下信道包含1 條主徑和1 條多徑,多徑能量為–3 dB,分別測試信噪比為10 dB,9 dB,8 dB,7 dB,6.5 dB,沒有多徑及多徑時延為10,20,30,40,50 個符號時的誤碼率情況,每種條件測試2.048×107 個數據,獲得均衡后、Viterbi 譯碼后、RS 譯碼后的誤碼率統計見表1、表2、表3。

表中第1 列表示RSN,第1 行表示時延(Time Delay,TD),以延時符號個數為單位。

由表1 可以看出,隨著信噪比的下降,均衡后誤碼率會有較大變化,當信噪比下降到6.5 dB 時,誤碼率達到10-2 量級;隨著多徑時延的增大,誤碼率略有提高。對比表1 和表2 可以看出,在總體趨勢保持基本一致的情況下Viterbi 譯碼后,除6.5 dB 下時延40 個和50 個符號的情況之外,誤碼率下降到10-4 量級,這說明Viterbi譯碼有效地糾正了均衡后系統的錯誤。對比表3,RS 譯碼后在信噪比為7 dB 以上時,除去時延50 個符號的情況下,誤碼率下降到10-6 量級,即使在6.5 dB 的情況下,也能達到10-4 量級,顯然性能又有顯著的提升。

4 結論

本文設計了寬帶單載波頻域均衡系統并完成FPGA 實現。實現了137.5 MHz 載波下27.5 Mbps 的碼元傳輸速率,并在MMSE 準則下完成頻域均衡,此外添加了卷積碼和RS 碼級聯編譯碼。最終在Virtix-4 芯片上實現整個系統,并分別對均衡后、Viterbi 譯碼、RS 譯碼后的誤碼率性能做了統計和對比,測試結果表明本系統可以很好地實現寬帶單載波通信。

電子發(fā)燒友App

電子發(fā)燒友App

評論