完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

電子發燒友網技術文庫為您提供最新技術文章,最實用的電子技術文章,是您了解電子技術動態的最佳平臺。

現場可編程門陣列FPGA(Field Programmable Gate Array)是美國Xilinx公司于1984年首先開發的一種通用型用戶可編程器件。FPGA內部由可綰程邏輯單元陣列、布線資源和可編程的I/O單元陣列構成,包含豐富的邏輯門、寄存器和I/O資源。目前,面向大規模可編程器件附的廣泛...

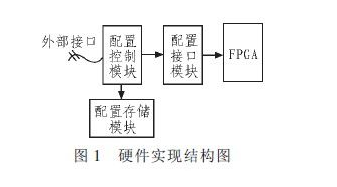

目前FPGA通過USB接口獲取USB設備中數據的方案大致分為兩大類,一類為在FPGA內部實現USB設備控制,另一類為在FPGA外部實現USB設備控制。在FPGA內部實現的方案需要在FPGA內部實現USB控制器,在內部實現或者外接USB收發器。該方案的實現具有較大難度,同時由于USB協議和文件系統都相...

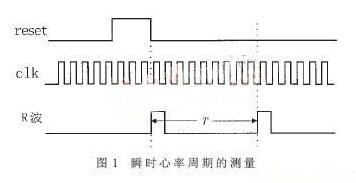

心率計是常用的醫學檢查設備,實時準確的心率測量在病人監控、臨床治療及體育競賽等方面都有著廣泛的應用。心率測量包括瞬時心率測量和平均心率測量。瞬時心率不僅能夠反映心率的快慢。同時能反映心率是否勻齊;...

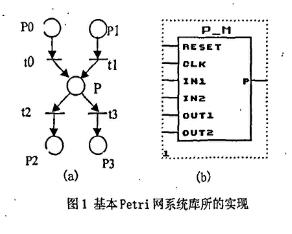

Petri網是異步并發現象建模的重要工具,Petri網的硬件實現將為并行控制器的設計提供一種有效的途徑.本文在通用的EDA軟件Max+PlusII中,研究了基本Petri網和時延Petrii網的硬件實現,用VHDL語言分別建立了庫所和變遷元件。最后給出了一個時延Petri網系統實例,通過調用元件庫中...

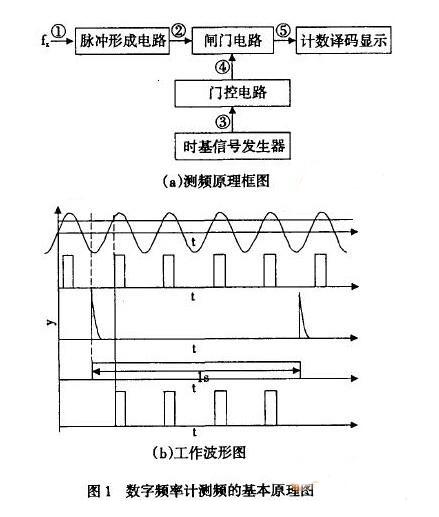

在電子工程,資源勘探,儀器儀表等相關應用中,頻率計是工程技術人員必不可少的測量工具。頻率測量也是電子測量技術中最基本最常見的測量之一。不少物理量的測量,如轉速、振動頻率等的測量都涉及到或可以轉化為頻率的測量。目前,市場上有各種多功能、高精度、高頻率的數字頻率計,但價格不菲。為適應實際工作的需要,本文...

隨著現代通信技術的迅速發展,信號的調制方式向多樣化發展,解淵技術也隨之不斷向前發展。為了對高速大帶寬的信號進行實時解調,現在很多的解調關鍵算法都是在高速硬件上用可編程邏輯器件(FPGA)實觀,利用FPGA強大的資源和實時處理能力來快速的實現信號的跟蹤、鎖定和解調但是,基于硬件的實現方案和基于軟件的方...

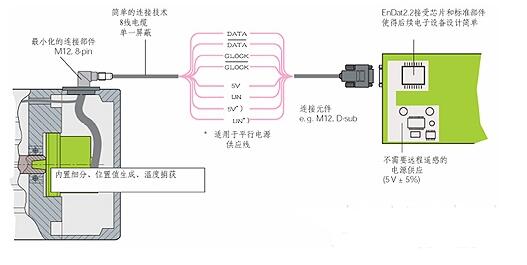

EnDat接口是HEIDENHAIN專為編碼器設計的數字式、全雙工同步串行的數據傳輸協議,具有傳輸速度快、功能強大、連線簡單、抗干擾能力強等優點,是編碼器、光柵尺數據傳輸的通用接口。本文闡述了EnDat接口的特點、功能、時序和數據傳輸、OEM數據存儲,同時介紹了編碼器數據采集后續電路設計方案、基于F...

復雜度日益增加的系統設計要求高性能FPGA的設計與PCB設計并行進行。通過整合FPGA和PCB設計工具以及采用高密度互連(HDI)等先進的制造工藝,這種設計方法可以降低系統成本、優化系統性能并縮短設計周期。...

電子系統功能實現的模式不外硬件和軟件兩種。基于馮。諾依曼或者哈佛體系結構的通用微處理器(MPU、MCU、DSP等)系統是軟件實現模式,其硬件電路結構固定,通過串行執行指令實現功能。軟件設計靈活、易升級,但執行速度慢、效率低;而專用集成電路(ASIC)采用硬件模式,通過固化的特定運算和單元電路完成功能...

開源硬件領域MCU板卡很火,著名的Arduino、樹莓派(Raspberry Pi)、Micro:bit,開源的MCU也是個熱門的話題,除了老牌的8051、OpenRisc等,這兩年的明星就是Risc V了,在中國集成電路大躍進的加持下,它幾乎成了中國處理器追趕世界的一劑春藥。...

在開發PL時一般都會用到分頻或倍頻,對晶振產生的時鐘進行分頻或倍頻處理,產生系統時鐘和復位信號,這是同步時序電路的關鍵,這時就需要使用到時鐘向導IP,下面就介紹一下在vivado中進行PL開發時調用IP的方法。...

在開發PL時一般都會用到分頻或倍頻,對晶振產生的時鐘進行分頻或倍頻處理,產生系統時鐘和復位信號,下面就介紹一下在vivado2017.3中進行PL開發時調用IP的方法。...

Xilinx每一個FPGA都有一個獨特的ID,也就是Device DNA,這個ID相當于我們的身份證,在FPGA芯片生產的時候就已經寫死在芯片的eFuse寄存器中,具有不可修改的屬性,因為使用的是熔斷技術。...

在sdk中選擇lwip模板,編譯調試可輕松連接成功并進行通信,模板中代碼完成的任務是client給server發什么,server就會回復什么。...

“No PP,No WAY”這是個眼見為實的世界,這是個視覺構成的信息洪流的世界。大腦處理視覺內容的速度比文字內容快6萬倍,而隨著智能手機的普及,圖片、視頻的產生和分享已經是人們在社交平臺上的基本交流方式。用戶通過手機、平板、電腦上傳和分享自己的圖片,而且這個趨勢是每年都在增長(參見圖1)。...

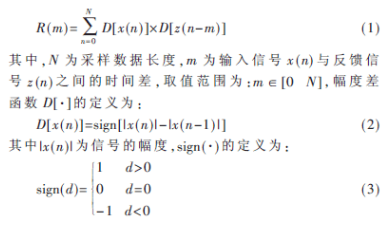

基于FPGA芯片Stratix II EP2S60F672C4設計實現了數字基帶預失真系統中的環路延遲估計模塊。該模塊運用了一種環路延遲估計新方法,易于FPGA實現。同時,在信號失真的情況下也能給出正確的估計結果。Modelsim SE 6.5c的時序仿真結果和SignalTaps II的硬件調試結...

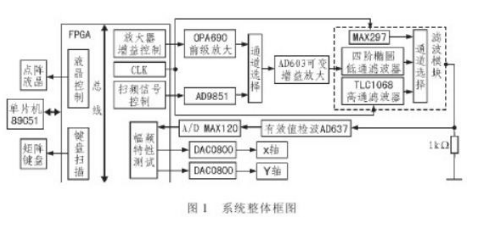

以單片機和可編程邏輯器件(FPGA)為控制核心,設計了一個程控濾波器,實現了小信號程控放大、程控調整濾波器截止頻率和幅頻特性測試的功能。其中放大模塊由可變增益放大器AD603實現,最大增益60dB,10dB步進可調,增益誤差小于1%。程控濾波模塊由MAX297低通濾波、TLC1068高通濾波及橢圓低...

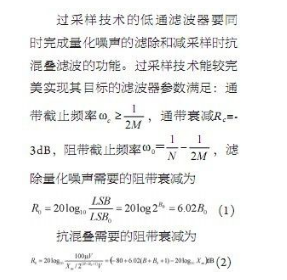

過采樣技術是數字信號處理者用來提高模數轉換器(ADC)性能經常使用的方法之一,它通過減小量化噪聲,提高ADC的信噪比,從而提高ADC的有效分辨率[1]。過采樣技術不但沒有增加額外的模擬電路,而且由于提高了有效分辨率還能簡化模擬電路,并且簡單易行,因而被數字信號處理實踐者廣泛應用于測控領域...