完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

電子發(fā)燒友網(wǎng)技術(shù)文庫(kù)為您提供最新技術(shù)文章,最實(shí)用的電子技術(shù)文章,是您了解電子技術(shù)動(dòng)態(tài)的最佳平臺(tái)。

可編程邏輯陣列(FPGA)由于其具有可編程、上市時(shí)間短、靈活性及高吞吐量等特性廣泛應(yīng)用于數(shù)字信號(hào)處理、接口電路控制、圖像處理及算法加速等領(lǐng)域,如在接口協(xié)議并串轉(zhuǎn)換電路、圖像算法加速電路及矩陣分解電路加速等領(lǐng)域應(yīng)用廣泛。隨著微電子工藝技術(shù)的進(jìn)步,F(xiàn)PGA器件向集成更多資源、更高速度及片上系統(tǒng)方向發(fā)展...

安裝好python、設(shè)置好環(huán)境變量后,在python安裝目錄下Script文件夾內(nèi)會(huì)存在pip.exe和easy_install.exe兩種在線安裝工具。...

浪潮聯(lián)合賽靈思宣布推出全球首款集成HBM2高速緩存的FPGA AI加速卡F37X,可在不到75W典型應(yīng)用功耗提供28.1TOPS的INT8計(jì)算性能和460GB/s的超高數(shù)據(jù)帶寬。...

TIDA-01480 參考設(shè)計(jì)是一種可擴(kuò)展的電源設(shè)計(jì),旨在為 Xilinx Zynq UltraScale+ (ZU+) 系列 MPSoC 器件供電。此設(shè)計(jì)接收來(lái)自標(biāo)準(zhǔn)直流電源的電力,并通過(guò)明確的 Samtec 插座端子板連接方式為 Xilinx 芯片組和 DDR 存儲(chǔ)器的所有電源軌供電。...

啟用 Alveo 加速器卡是 Xilinx 及合作伙伴應(yīng)用的一個(gè)生態(tài)系統(tǒng),主要面向數(shù)據(jù)中心的工作負(fù)載。對(duì)于定制解決方案,Xilinx 應(yīng)用開發(fā)工具套件 (SDAccel?) 和機(jī)器學(xué)習(xí)套件可為開發(fā)人員提供將差異化應(yīng)用推向市場(chǎng)的各種工具。...

智慧醫(yī)療整合個(gè)人生理狀態(tài)感測(cè)與結(jié)合物聯(lián)網(wǎng),是眾多IoT應(yīng)用中的重點(diǎn)項(xiàng)目,因?yàn)獒t(yī)療IoT應(yīng)用市場(chǎng)的特殊性,不僅相關(guān)設(shè)備需達(dá)到高穩(wěn)定性要求,同時(shí)所開發(fā)的產(chǎn)品受法規(guī)、產(chǎn)品驗(yàn)證嚴(yán)格管制,選擇開發(fā)平臺(tái)就成為左右成敗的重要關(guān)鍵。.. ...

對(duì)于基于數(shù)字信號(hào)處理器(DSP)的設(shè)計(jì),如果DSP沒(méi)有足夠的安全能力,便特別容易受到入侵。在許多應(yīng)用中,如果使用FPGA以作配合來(lái)卸載DSP的部分工作,便可以輕易實(shí)施先進(jìn)的安全功能。而且,如果配合的FPGA使用flash存儲(chǔ)技術(shù),在芯片上存儲(chǔ)結(jié)構(gòu)中的配置位流以及關(guān)鍵性密匙信息,便可以實(shí)現(xiàn)固有的防止復(fù)...

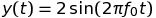

隨著現(xiàn)代通信技術(shù)的廣泛使用,通信企業(yè)問(wèn)的競(jìng)爭(zhēng)不斷加劇,為提升自身的競(jìng)爭(zhēng)優(yōu)勢(shì),通信企業(yè)需要將其通信信號(hào)的質(zhì)量提升,并提高通信系統(tǒng)各項(xiàng)指標(biāo)的穩(wěn)定性、安全性、高效性。在音頻信號(hào)處理方法及FPGA實(shí)現(xiàn)中,采用AGC算法,可提高音頻信號(hào)系統(tǒng)和音頻信號(hào)輸出的穩(wěn)定性,解決了AGC調(diào)試后的信號(hào)失真問(wèn)題。本文針對(duì)基于...

人工神經(jīng)網(wǎng)絡(luò)在智能控制、模式識(shí)別、圖像處理等領(lǐng)域中應(yīng)用廣泛。在進(jìn)行神經(jīng)網(wǎng)絡(luò)的應(yīng)用研究時(shí),人們可以將神經(jīng)網(wǎng)絡(luò)模型或算法在通用的計(jì)算機(jī)上軟件編程實(shí)現(xiàn),但很多時(shí)間浪費(fèi)在分析指令、讀出寫入數(shù)據(jù)等,其實(shí)現(xiàn)效率并不高。軟件實(shí)現(xiàn)的缺點(diǎn)是并行程度較低,因此利用軟件實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)的方法無(wú)法滿足某些對(duì)數(shù)據(jù)實(shí)時(shí)處理要求較高...

FPGA本身是有專門的時(shí)鐘cell的,以xilinx FPGA為例,就是primitive庫(kù)中的BUFG。...

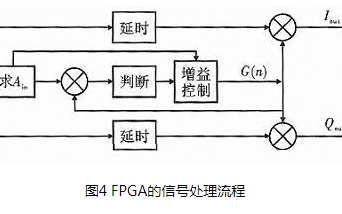

心電信號(hào)( electrocardiogram,ECG) 能夠客觀反映心臟各部分的生理狀況,也是用來(lái)診斷心臟疾病的主要依據(jù),由于其具有易于檢測(cè)和有較好直觀性等特點(diǎn),在臨床醫(yī)學(xué)中得到較為廣泛的研究與應(yīng)用[1,2]。自1906 年,第一臺(tái)心電圖儀用于臨床以來(lái),各種形式的心電監(jiān)護(hù)儀相繼出現(xiàn)。傳統(tǒng)的心電圖檢...

Python 是一個(gè)高層次的結(jié)合了解釋性、編譯性、互動(dòng)性和面向?qū)ο蟮哪_本語(yǔ)言。...

這些新設(shè)備有兩個(gè)主要市場(chǎng)。機(jī)器學(xué)習(xí)中的神經(jīng)網(wǎng)絡(luò)將數(shù)據(jù)分為兩個(gè)主要階段:訓(xùn)練和推理,并且在每個(gè)階段中使用不同的芯片。雖然神經(jīng)網(wǎng)絡(luò)本身通常駐留在訓(xùn)練階段的數(shù)據(jù)中心中,但它可能具有用于推理階段的邊緣組件。現(xiàn)在的問(wèn)題是什么類型的芯片以及哪種配置能夠產(chǎn)生最快、最高效的深度學(xué)習(xí)。...

雖然定制實(shí)現(xiàn)DSP功能,但在很多應(yīng)用中幾種功能,如FIR(有限脈沖響應(yīng))濾波器,IIR(無(wú)限脈沖響應(yīng))濾波器、FFT(快速傅里葉)和混頻器是共同的。所有這些功能都需要與加、減、累加一起的乘法單元組合。...

車載導(dǎo)航系統(tǒng)電路采用TI公司的TMS320C6713B-A200作為DSP,該DSP芯片標(biāo)稱主頻為200 MHz,工作在160 MHz主頻時(shí)DSP處理能力為1600 MI·s-1/1 200MFLOPS。...

首先是內(nèi)核的選擇。LPC4350基于32位的ARM Cortex-M4和Cortex-M0內(nèi)核(以下簡(jiǎn)稱M4和M0),兩個(gè)內(nèi)核均可在高達(dá)204MHz的主頻下執(zhí)行代碼。...

既然HDL設(shè)計(jì)是并行的,那么就只能各個(gè)擊破了。我的習(xí)慣是先抓幾個(gè)重要端口,比如時(shí)鐘(CLK)、復(fù)位(RESET)等出現(xiàn)頻率比較高的端口,把它先弄清楚,比如時(shí)鐘是什么頻率的?復(fù)位是高有效還是低有效?...

剛開始玩CPLD/FPGA開發(fā)板的時(shí)候使用的一塊基于EPM240T100的板子,alter的這塊芯片雖說(shuō)功耗小體積小,但是資源還是很小的,你寫點(diǎn)稍微復(fù)雜的程序,如果不注意coding style,很容易就溢出了。當(dāng)時(shí)做一個(gè)三位數(shù)的解碼基本就讓我苦死了,對(duì)coding style的重要性也算是有一個(gè)比...

近十年來(lái),人工智能又到了一個(gè)快速發(fā)展的階段。深度學(xué)習(xí)在其發(fā)展中起到了中流砥柱的作用,盡管擁有強(qiáng)大的模擬預(yù)測(cè)能力,深度學(xué)習(xí)還面臨著超大計(jì)算量的問(wèn)題。在硬件層面上,GPU,ASIC,F(xiàn)PGA都是解決龐大計(jì)算量的方案。本文將闡釋深度學(xué)習(xí)和FPGA各自的結(jié)構(gòu)特點(diǎn)以及為什么用FPGA加速深度學(xué)習(xí)是有效的,并且...

說(shuō)到頻域,不可避免的會(huì)提到傅里葉變換,傅里葉變換提供了一個(gè)將信號(hào)從時(shí)域轉(zhuǎn)變到頻域的方法。之所以要有信號(hào)的頻域分析,是因?yàn)楹芏嘈盘?hào)在時(shí)域不明顯的特征可以在頻域下得到很好的展現(xiàn),可以更加容易的進(jìn)行分析和處理。...