基于eFPGAsim的電機(jī)硬件在環(huán)測(cè)試系統(tǒng),是面向電驅(qū)HIL測(cè)試的高精度FPGA的解決方案,利用最新的eHS (Electric Hardware Solver)技術(shù)實(shí)現(xiàn),在獲得基于FPGA片上仿真

2017-08-09 10:52:21 2930

2930

參考設(shè)計(jì)演示了10GbE MAC英特爾FPGA IP功能的運(yùn)行,在許多環(huán)回硬件配置中采用低成本SFP +接口實(shí)現(xiàn)最高線(xiàn)速性能,如圖1所示。特征展示10GbE MAC和XAUI PHY Intel FPGA

2018-07-26 16:33:03

本人剛?cè)腴T(mén)FPGA,不知道如何實(shí)現(xiàn)FPGA+DSP,FPGA+ARM接口設(shè)計(jì),網(wǎng)上查詢(xún)有的說(shuō)FPGA+DSP可以通過(guò)EMIF,IP核實(shí)現(xiàn),FPGA+ARM可以通過(guò)SPI,有沒(méi)有具體硬件參考的?

2016-08-27 11:30:26

PHY是什么意思?FPGA實(shí)現(xiàn)網(wǎng)口通信主要有哪幾種方式?

2022-02-22 07:57:17

,整板硬件包括FPGA電路, DDR3電路,外圍接口電路,加上時(shí)鐘和控制邏輯等輔助電路,形成一個(gè)完整的、一體化的數(shù)字系統(tǒng)硬件平臺(tái)。能夠快速接入FC-AE網(wǎng)絡(luò),實(shí)現(xiàn)光纖總線(xiàn)終端的數(shù)據(jù)通訊。課程提供項(xiàng)目

2021-11-17 23:12:06

【作者】:陳志德;曾凡平;【來(lái)源】:《小型微型計(jì)算機(jī)系統(tǒng)》2010年03期【摘要】:分析和研究UML狀態(tài)圖、擴(kuò)展?fàn)顟B(tài)機(jī)和Petri網(wǎng)在類(lèi)測(cè)試用例生成的特點(diǎn),提出結(jié)合三者優(yōu)勢(shì)的類(lèi)測(cè)試用例生成方法.通過(guò)

2010-04-24 09:52:23

摘要:為了實(shí)現(xiàn)對(duì)非相干雷達(dá)的接收相參處理,基于數(shù)字穩(wěn)定校正(DSU)的原理,采用ALTERA公司的StratixⅡ系列芯片和VHDL編程語(yǔ)言,設(shè)計(jì)了一種基于FPGA的DSU硬件實(shí)現(xiàn)方法。實(shí)驗(yàn)結(jié)果表明

2019-06-28 08:27:33

通過(guò)編程來(lái)改變內(nèi)部結(jié)構(gòu)的芯片。FPGA 功能實(shí)現(xiàn):需要通過(guò)編程即設(shè)計(jì)硬件描述語(yǔ)言,經(jīng)過(guò) EDA 工具編譯、

2022-01-25 06:45:52

如何利用以太網(wǎng)硬件協(xié)仿真接口實(shí)現(xiàn)便捷和高帶寬的仿真?

2021-05-28 06:36:35

以太網(wǎng)EMC接口硬件電路如何在PCB上實(shí)現(xiàn)

2021-02-25 07:43:22

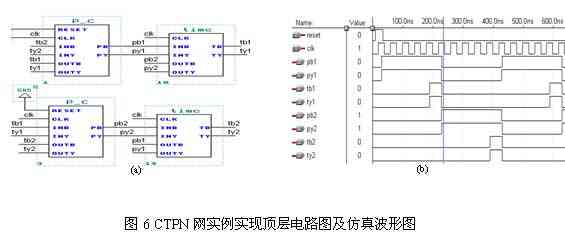

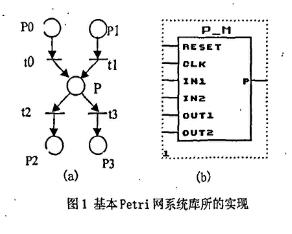

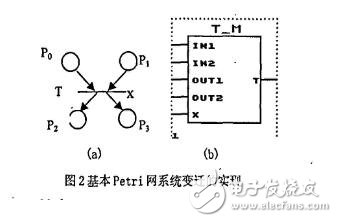

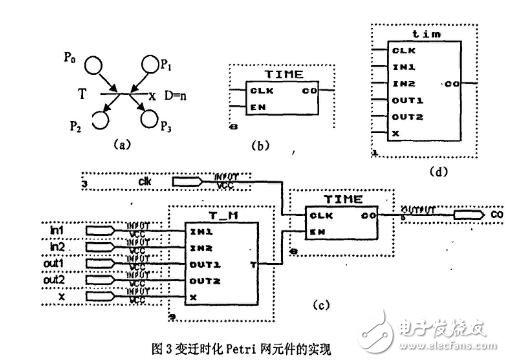

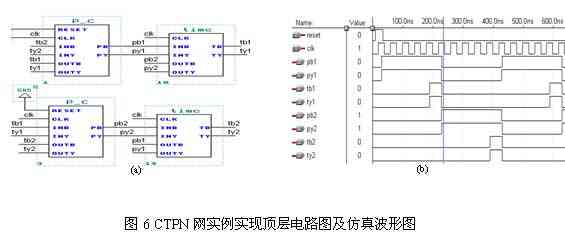

本文分別用VHDL語(yǔ)言研究了幾種Petri網(wǎng)系統(tǒng)的硬件實(shí)現(xiàn),包括同步PN、時(shí)延PN,尤其是高級(jí)網(wǎng)系統(tǒng)有色PN。在當(dāng)前的研究中有色Petri網(wǎng)的硬件實(shí)現(xiàn)是一個(gè)難點(diǎn)。

2021-04-30 06:13:21

千兆以太網(wǎng)技術(shù)是什么基于Altera FPGA的千兆以太網(wǎng)實(shí)現(xiàn)方案

2021-05-08 07:32:49

的數(shù)據(jù)發(fā)送和接收功能的實(shí)現(xiàn)。圖 9 W5500功能實(shí)測(cè)結(jié)果圖3 結(jié)語(yǔ)本系統(tǒng)實(shí)現(xiàn)了基于FPGA的,采用嵌入式以太網(wǎng)W5500芯片以硬件形式實(shí)現(xiàn)的TCP/IP協(xié)議棧,提高了CPU的處理效率,并且使得通信速率在很大程度上得到了提高,為以太網(wǎng)數(shù)據(jù)傳輸系統(tǒng)的設(shè)計(jì)提供了一種有效的方式。

2018-08-07 10:10:25

本帖最后由 gk320830 于 2015-3-8 21:23 編輯

開(kāi)始科創(chuàng),老師給了我們一個(gè)題基于FPGA的FFT算法硬件實(shí)現(xiàn)。但是什么都不會(huì),想找些論文看看,求相關(guān)的論文

2012-05-24 22:14:40

基于FPGA的萬(wàn)兆以太網(wǎng)接口的設(shè)計(jì)與實(shí)現(xiàn)標(biāo)準(zhǔn)中萬(wàn)兆以太網(wǎng)物理層及媒質(zhì)接入控制子層的相關(guān)協(xié)議以 應(yīng)用物理環(huán)境為例,闡述了萬(wàn)兆以太網(wǎng)接口各個(gè)單元模塊的功能和設(shè)計(jì)實(shí)現(xiàn)方法 仿真結(jié)果表明,該萬(wàn)兆以太網(wǎng)接口

2012-08-11 15:48:12

,希望有興趣的同志和我聯(lián)系!FPGA以太網(wǎng)傳輸系統(tǒng)介紹:1)平臺(tái):ALTERA FPGA,cyclone系列器件即可支持;2)系統(tǒng)架構(gòu):硬件:FPGA + PHY,其中MAC在FPGA中以IP方式實(shí)現(xiàn)

2014-06-19 12:04:25

,希望有興趣的同志和我聯(lián)系!FPGA以太網(wǎng)傳輸系統(tǒng)介紹:1)平臺(tái):ALTERA FPGA,cyclone系列器件即可支持;2)系統(tǒng)架構(gòu):硬件:FPGA + PHY,其中MAC在FPGA中以IP方式實(shí)現(xiàn)

2014-06-19 12:06:43

嵌入式網(wǎng)絡(luò)設(shè)備中引入FPGA技術(shù),可以使嵌入式以太網(wǎng)的速度更快。為此,本文介紹基于FPGA的嵌入式系統(tǒng)與LAN91C111型自適應(yīng)10Mb/100Mb嵌入式以太網(wǎng)的接口電路與實(shí)現(xiàn)方法。1 硬件設(shè)計(jì)1.1

2019-06-04 05:00:14

基于FPGA的超高速FFT硬件實(shí)現(xiàn)介紹了頻域抽取基二快速傅里葉運(yùn)算的基本原理;討論了基于FPGA達(dá)4 096點(diǎn)的大點(diǎn)數(shù)超高速FFT硬件系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)方法,當(dāng)多組大點(diǎn)數(shù)進(jìn)行FFT運(yùn)算時(shí),利用FPGA

2009-06-14 00:19:55

【關(guān)鍵詞】:半導(dǎo)體生產(chǎn)線(xiàn);;層次有色賦時(shí)Petri網(wǎng);;遺傳算法;;建模;;優(yōu)化【DOI】:CNKI:SUN:DZXU.0.2010-02-014【正文快照】:1引言半導(dǎo)體生產(chǎn)線(xiàn)作為第三類(lèi)生產(chǎn)系統(tǒng)—可重入

2010-05-04 08:08:48

`基于AlteraFPGA的千兆以太網(wǎng)實(shí)現(xiàn)方案`

2013-06-10 11:59:22

大家好,我想知道如何實(shí)現(xiàn)硬件(FPGA)中的時(shí)序報(bào)告給出的時(shí)序。我的意思是,如何測(cè)量FPGA和FPGA中輸入信號(hào)的建立或保持時(shí)間與靜態(tài)時(shí)間報(bào)告給出的值進(jìn)行比較。FPGA怪胎以上來(lái)自于谷歌翻譯以下

2019-01-15 11:07:15

嗨,我正在嘗試使用spartan 3E FPGA(成本因素)實(shí)現(xiàn)千兆以太網(wǎng)接口。由于斯巴達(dá)系列中沒(méi)有RocketIO收發(fā)器,因此我們必須使用LVDS TBI接口。有沒(méi)有人有實(shí)施這個(gè)經(jīng)驗(yàn)?你能給我一些

2019-08-07 09:38:25

如何在沒(méi)有AXI接口的kintex 7 FPGA中實(shí)現(xiàn)以太網(wǎng)?請(qǐng)幫幫我

2020-08-18 09:59:04

本文通過(guò)對(duì)長(zhǎng)BCH碼優(yōu)化方法的研究與討論,針對(duì)標(biāo)準(zhǔn)中二進(jìn)制BCH碼的特性,設(shè)計(jì)了實(shí)現(xiàn)該譯碼器的FPGA硬件結(jié)構(gòu)。

2021-06-15 09:23:27

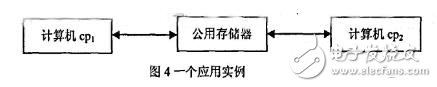

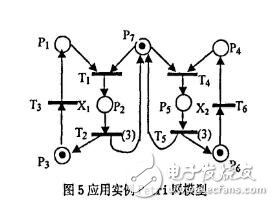

本文介紹一種使用硬件描述語(yǔ)言VHDL來(lái)實(shí)現(xiàn)基于Petri網(wǎng)的并行控制器的方法。首先使用Petri網(wǎng)對(duì)問(wèn)題進(jìn)行建模,并對(duì)模型進(jìn)行分析和控制,獲得控制器的Petri網(wǎng)模型;然后用VHDL對(duì)Petri網(wǎng)

2019-08-16 07:52:03

System Generator for DSP的特點(diǎn)是什么?如何使用System Generator for DSP實(shí)現(xiàn)系統(tǒng)級(jí)建模?怎么在Matlab中實(shí)現(xiàn)數(shù)字通信FPGA硬件設(shè)計(jì)?

2021-04-29 06:20:46

本帖最后由 eehome 于 2013-1-5 10:04 編輯

指紋識(shí)別算法的研究及基于FPGA的硬件實(shí)現(xiàn)

2012-05-23 20:14:46

在做一個(gè)數(shù)字機(jī)頂盒以太網(wǎng)接口的硬件設(shè)計(jì)與實(shí)現(xiàn)。。要求以太網(wǎng)硬件模塊系統(tǒng)框圖(phy+mac),還有ESD保護(hù)設(shè)計(jì)與實(shí)現(xiàn)、原理圖設(shè)計(jì)與Layout。以及各參數(shù)的測(cè)量。。。。由于自己知識(shí)有限,不知有哪位大俠接觸過(guò)這個(gè),給點(diǎn)意見(jiàn)。。再此謝謝大家了。

2014-02-18 13:57:26

本帖最后由 upup11 于 2012-11-21 20:45 編輯

我想請(qǐng)教一個(gè)問(wèn)題:如何用FPGA硬件實(shí)現(xiàn)小波變換。 問(wèn)題的由來(lái):我在做一個(gè)不影響語(yǔ)音通信的前提下,電話(huà)線(xiàn)感應(yīng)信號(hào)特征提取

2012-11-20 21:35:16

請(qǐng)問(wèn)有對(duì)petri網(wǎng)熟悉的朋友嗎,有一個(gè)項(xiàng)目想找人合作,待遇優(yōu)厚,有興趣的朋友請(qǐng)聯(lián)系我

2011-11-17 10:30:04

)映射到這一公共骨干網(wǎng)中。光設(shè)備生產(chǎn)商不斷降低成本,采用跨平臺(tái)元器件,因此,靈活映射各種客戶(hù)側(cè)端口的解決方案得到了應(yīng)用。FPGA是實(shí)現(xiàn)“通用客戶(hù)側(cè)端口”的主要元件,可以配置支持各種客戶(hù)側(cè)接口。這樣,單片

2011-07-13 14:36:03

,即第1層上實(shí)現(xiàn)基于相同的IEEE 802.3標(biāo)準(zhǔn),因此可以使用一個(gè)基于FPGA的平臺(tái)來(lái)支持不同的工業(yè)以太網(wǎng)協(xié)議,不論這些協(xié)議有怎樣的實(shí)時(shí)屬性和實(shí)現(xiàn)方法。對(duì)于速度和實(shí)時(shí)性能要求非常高的協(xié)議,在硬件中以

2019-07-29 07:40:50

概述EasyGo FPGA Solver是EasyGo開(kāi)發(fā)的專(zhuān)門(mén)部署在FPGA 硬件上的解算器軟件。根據(jù)不同的應(yīng)用需求,會(huì)有不同的FPGA Solver 選擇

2022-05-19 09:21:43

證明活的標(biāo)識(shí)S-圖、活的標(biāo)識(shí)T-圖、有界的沖突無(wú)關(guān)的Petri 網(wǎng)、有界的標(biāo)識(shí)T-圖具有匯合性質(zhì),討論共享合成與同步合成操作對(duì)Petri 網(wǎng)匯合性質(zhì)的保持性,得出由上述簡(jiǎn)單的Petri 網(wǎng)子

2009-03-21 15:42:37 12

12 為了增強(qiáng)傳統(tǒng)對(duì)象Petri網(wǎng)的定量分析能力,提出隨機(jī)對(duì)象Petri網(wǎng)模型。該模型具備隨機(jī)性和層次特性,獲得與隨機(jī)Petri網(wǎng)的等價(jià)關(guān)系,從宏觀和微觀2個(gè)層面對(duì)系統(tǒng)進(jìn)行性能分析,并將

2009-04-13 08:48:34 27

27 介紹了頻域抽取基二快速傅里葉運(yùn)算的基本原理;討論了基于FPGA達(dá)4 096點(diǎn)的大點(diǎn)數(shù)超高速FFT硬件系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)方法,當(dāng)多組大點(diǎn)數(shù)進(jìn)行FFT運(yùn)算時(shí),利用FPGA內(nèi)部大容量存儲(chǔ)資源,采

2009-04-26 18:33:08 26

26 Petri 網(wǎng)是一種很有效的模型描述語(yǔ)言,尤其適合描述工作流。[1]給出了基于Petri 網(wǎng)的工作流邏輯(WF_logic)化簡(jiǎn)規(guī)則,這里則借助矩陣及矩陣運(yùn)算或矩陣上的初等變換來(lái)實(shí)現(xiàn)這些

2009-06-10 15:05:07 15

15 本文介紹了神經(jīng)網(wǎng)絡(luò)VLSI硬件實(shí)現(xiàn)的基本情況和VerilgHDL硬件設(shè)計(jì)方法的概念,在此基礎(chǔ)上利用FPGA設(shè)計(jì)出了Kohonen競(jìng)爭(zhēng)網(wǎng)絡(luò)硬件電路,其工作頻率為33Mhz,并對(duì)其工作過(guò)程進(jìn)行了較詳細(xì)的

2009-06-18 08:49:21 11

11 本文針對(duì)工業(yè)中廣泛存在的混雜系統(tǒng),結(jié)合進(jìn)化算法,研究了應(yīng)用Petri 網(wǎng)的分層遞階建模方法,實(shí)現(xiàn)一類(lèi)混雜系統(tǒng)的建模與優(yōu)化。關(guān)鍵詞:混雜系統(tǒng) Petri 網(wǎng) 建模 進(jìn)化算法 優(yōu)化

2009-06-22 09:13:07 17

17 提出用FPGA 來(lái)實(shí)現(xiàn)指紋識(shí)別算法, 代替了PC 機(jī)、通用MCU 或者DSP。算法由硬件來(lái)實(shí)現(xiàn), 提高了運(yùn)算速度。同時(shí)具體說(shuō)明了指紋識(shí)別系統(tǒng)的基本原理、系統(tǒng)總體結(jié)構(gòu)、FPGA 模塊劃分, 以及指

2009-07-22 15:17:27 0

0 為增強(qiáng)工作流管理系統(tǒng)的安全性,本文使用高級(jí) Petri 網(wǎng)對(duì)工作流過(guò)程進(jìn)行建模。針對(duì)不同的安全問(wèn)題,分別引入時(shí)間Petri 網(wǎng)、有色Petri 網(wǎng)和有色時(shí)間Petri 網(wǎng)進(jìn)行建模。保證了

2009-08-05 16:37:46 20

20 軟硬件劃分技術(shù)是軟硬件協(xié)同設(shè)計(jì)中的一個(gè)關(guān)鍵技術(shù)。提出將時(shí)間Petri 網(wǎng)應(yīng)用到軟硬件劃分當(dāng)中,為系統(tǒng)的性能評(píng)估提供了形式化的方法和工具。另一方面,將系統(tǒng)功能集中到Petri

2009-08-15 14:34:35 11

11 對(duì)象Petri網(wǎng)(OPN)Petri網(wǎng)相結(jié)合的面向?qū)ο蟮睦碚撎峁┝艘环N有效的方法使用在并購(gòu)離散事件動(dòng)態(tài)系統(tǒng)S領(lǐng)域的Petri網(wǎng)。的概念和對(duì)象的機(jī)制帶來(lái)的,而Petri網(wǎng)的基

2009-08-31 09:09:44 0

0 線(xiàn)性時(shí)態(tài)邏輯Petri 網(wǎng)結(jié)合了Petri 網(wǎng)和時(shí)序邏輯的優(yōu)點(diǎn),清晰簡(jiǎn)潔的描述并發(fā)系統(tǒng)事件間的時(shí)序和因果關(guān)系,包括系統(tǒng)的活性和安全性。其中自動(dòng)機(jī)的體積是模型檢驗(yàn)的一個(gè)關(guān)鍵性

2009-08-31 16:14:50 22

22 對(duì)象Petri 網(wǎng)將面向?qū)ο蟮乃枷牒?b class="flag-6" style="color: red">Petri 網(wǎng)相結(jié)合,引入了對(duì)象的概念和機(jī)制,擴(kuò)展了基本Petri 網(wǎng)的功能,為Petri 網(wǎng)在離散事件動(dòng)態(tài)系統(tǒng)的建模和仿真領(lǐng)域的應(yīng)用提供了一條有效的途徑

2009-09-01 11:02:15 7

7 該文介紹了佩特利網(wǎng)(Petri網(wǎng))和Stateflow的基本概念,給出Petri網(wǎng)在Matlab環(huán)境下的仿真方法,并以單水箱系統(tǒng)的混合Petri網(wǎng)模型為例進(jìn)行說(shuō)明,結(jié)

2009-09-03 12:00:44 50

50 提出了一種建立在petri 網(wǎng)的基本結(jié)構(gòu)上的形式化正向推理算法,通過(guò)建立petri網(wǎng)的關(guān)聯(lián)矩陣、標(biāo)識(shí)向量和激發(fā)向量,將petri 網(wǎng)與矩陣運(yùn)算結(jié)合

2009-09-14 08:09:19 11

11 無(wú)線(xiàn)通信系統(tǒng)是一個(gè)分布式實(shí)時(shí)多任務(wù)數(shù)據(jù)處理系統(tǒng),具有實(shí)時(shí)性、并發(fā)、異步和多任務(wù)等特點(diǎn)。Petri網(wǎng)是描述和分析異步并發(fā)現(xiàn)象的一種有效的模型工具。以Petri網(wǎng)為工具,建立

2010-01-22 14:46:39 16

16 PWM整流電路是交-直-交變流器的重要電路,是包括連續(xù)和離散事件的混雜系統(tǒng),具有并發(fā)、異步等特點(diǎn)。Petri網(wǎng)是描述和分析異步并發(fā)現(xiàn)象的一種有效的混雜系統(tǒng)建模工具。本文以Petri網(wǎng)

2010-02-21 11:20:08 19

19 本文介紹了基于FPGA和MPC860架構(gòu)的網(wǎng)絡(luò)應(yīng)用硬件開(kāi)發(fā)平臺(tái)的設(shè)計(jì)原理及具體實(shí)現(xiàn),討論了其優(yōu)于網(wǎng)絡(luò)處理器的性能特點(diǎn),給出了利用該平臺(tái)進(jìn)行網(wǎng)絡(luò)應(yīng)用開(kāi)發(fā)的實(shí)例,并介紹了其在網(wǎng)

2010-03-02 16:28:24 13

13 乘累加器在DSP算法中有著舉足輕重的地位。現(xiàn)在,很多前端DSP算法都通過(guò)FPGA實(shí)現(xiàn)。結(jié)合FPGA具體的硬件結(jié)構(gòu),提出了乘累加器在FPGA中實(shí)現(xiàn)的改進(jìn)方法:流水線(xiàn)技術(shù)、CSD編碼、DA算法,

2010-08-06 14:41:38 29

29 提出了模糊CMAC網(wǎng)絡(luò)的一種基于FPGA的硬件實(shí)現(xiàn)方法。首先,分析了模糊CMAC網(wǎng)絡(luò)的結(jié)構(gòu)與算法,并以MATLAB仿真為依據(jù),得到模糊CMAC網(wǎng)絡(luò)的FPGA實(shí)現(xiàn)所需的參數(shù);在此基礎(chǔ)上,對(duì)模糊CMAC

2010-08-09 14:55:03 19

19 Petri網(wǎng)模型對(duì)復(fù)合時(shí)序事件具有較好的描述和檢測(cè)能力,提出基于Petri網(wǎng)描述和推理的監(jiān)控視頻事件信息的自動(dòng)識(shí)別方法.將運(yùn)動(dòng)目標(biāo)及其特征間的空間關(guān)系用Petri網(wǎng)的庫(kù)表示,時(shí)間關(guān)系

2010-09-23 11:51:53 19

19 1 引言Petri網(wǎng)是一種系統(tǒng)的、數(shù)學(xué)的和圖形的描述和分析工具[1],隨著超大規(guī)模集成電路FPGA和CPLD的發(fā)展,Petri網(wǎng)的硬件實(shí)現(xiàn)成為可能,而基于Petri網(wǎng)的邏輯控制器的邏輯電路

2009-01-09 16:03:45 757

757

基于FPGA的嵌入式Linux軟硬件設(shè)計(jì)

引言

FPGA是通過(guò)邏輯組合電路來(lái)實(shí)現(xiàn)各種功能的器件。由于FPGA內(nèi)部集成了大量的邏輯資源和可配置的I/O引腳,加上獨(dú)特的

2010-03-10 10:20:04 793

793

提出了二維模糊CMAC網(wǎng)絡(luò)的一種基于FPGA的硬件實(shí)現(xiàn)方法。首先,分析了模糊CMAC網(wǎng)絡(luò)的結(jié)構(gòu)與算法,并以Matlab仿真為依據(jù),得到模糊CMAC網(wǎng)絡(luò)的FPGA實(shí)現(xiàn)所需的參數(shù);在此基礎(chǔ)上,對(duì)模糊CMAC網(wǎng)絡(luò)進(jìn)行硬件模塊劃分,基于VHDL實(shí)現(xiàn)了各硬件模塊的功能描述,并對(duì)模塊

2011-03-15 17:19:56 29

29 System Generator 工具由 MathWorks 與 Xilinx 合作開(kāi)發(fā)而成,DSP 設(shè)計(jì)人員可使用 MATLAB 和Simulink 工具在 FPGA 內(nèi)進(jìn)行開(kāi)發(fā)和仿真來(lái)完善 DSP 設(shè)計(jì)。 該工具為系統(tǒng)級(jí) DSP 設(shè)計(jì)與 FPGA 硬件實(shí)現(xiàn)的融合起

2011-05-11 18:36:23 224

224 本文闡述了主同步搜索的改進(jìn)型算法,并且針對(duì)這種算法提出了基于片上RAM 的實(shí)現(xiàn)方式,最大程度地節(jié)省了FPGA 的硬件資源,為WCDMA 同步的FPGA 實(shí)現(xiàn)提供了很好的解決方案。這種技術(shù)可

2011-05-14 16:45:53 30

30 經(jīng)過(guò)硬件平臺(tái)的驗(yàn)證,基于FPGA 的VGA 圖形顯示器已達(dá)到設(shè)計(jì)要求,可實(shí)現(xiàn)彩條、漢字、小圖像和大圖像的顯示,并可實(shí)現(xiàn)FPGA 器件對(duì)顯示器的單片控制

2011-06-08 09:55:43 1992

1992

眾所周知. Petri網(wǎng) [ZHS1是一種數(shù)學(xué)模型.便于描述和模擬異步并發(fā)系統(tǒng),具有友好的圖形表示。Petri網(wǎng)最早是在C.A.Petri的博士論文Kommunikafion mit Automaten中被提出的.而后.Petri網(wǎng)如雨

2011-06-16 17:42:57 18

18 在對(duì)模塊化制造系統(tǒng)( MPS )進(jìn)行設(shè)計(jì)時(shí),運(yùn)用 Petri網(wǎng) 建立其狀態(tài)轉(zhuǎn)換模型,從邏輯控制的角度出發(fā),給出了用Petri網(wǎng)控制器工具設(shè)計(jì)PLC程序的一般方法。并從實(shí)例出發(fā)介紹了基于Petri網(wǎng)控

2011-08-09 14:51:54 23

23 本書(shū)共分8章,主要內(nèi)容包括典型fpga器件的介紹、vhdl硬件描述語(yǔ)言、fpga設(shè)計(jì)中常用軟件簡(jiǎn)介、用fpga實(shí)現(xiàn)數(shù)字信號(hào)處理的數(shù)據(jù)規(guī)劃、多種結(jié)構(gòu)類(lèi)型的fir數(shù)字濾波器的fpga實(shí)現(xiàn)、不同結(jié)構(gòu)

2011-11-04 15:50:12 0

0 采用雙運(yùn)算核在FPGA硬件平臺(tái)上實(shí)現(xiàn)小波變換模塊。采用單一時(shí)鐘,在不增加系統(tǒng)設(shè)計(jì)復(fù)雜性和功耗的情況下,使得系統(tǒng)達(dá)到實(shí)時(shí)處理的要求。系統(tǒng)通過(guò)仿真驗(yàn)證,工作穩(wěn)定可靠。

2011-12-07 13:59:56 22

22 本書(shū)比較全面地闡述了fpga在數(shù)字信號(hào)處理中的應(yīng)用問(wèn)題。本書(shū)共分8章,主要內(nèi)容包括典型fpga器件的介紹、vhdl硬件描述語(yǔ)言、fpga設(shè)計(jì)中常用軟件簡(jiǎn)介、用fpga實(shí)現(xiàn)數(shù)字信號(hào)處理的數(shù)據(jù)規(guī)劃、多種

2015-12-23 11:07:46 44

44 基于有色Petri網(wǎng)的網(wǎng)絡(luò)化傳感系統(tǒng)研究_程學(xué)珍

2017-01-31 15:22:44 0

0 Petri網(wǎng)在計(jì)費(fèi)系統(tǒng)中的應(yīng)用研究_侯煜

2017-03-19 11:27:34 0

0 基于擴(kuò)展染色Petri網(wǎng)的工作流過(guò)程模型_周小聰

2017-03-16 09:59:00 0

0 Petri網(wǎng)的水產(chǎn)品溯源系統(tǒng)模型_袁紅春

2017-03-19 18:58:18 3

3 混成時(shí)空Petri網(wǎng)的CPS實(shí)時(shí)事件模型_譚朋柳

2017-03-19 19:07:04 0

0 基于對(duì)稱(chēng)三層架構(gòu)的Petri網(wǎng)仿真工具開(kāi)發(fā)_王雷

2017-03-19 19:19:35 0

0 算法進(jìn)行深入研究,面向Xilinx K7 410T FPGA 芯片設(shè)計(jì)SHA-1算法實(shí)現(xiàn)結(jié)構(gòu),完成SHA-1算法編程,進(jìn)行測(cè)試和后續(xù)應(yīng)用。該算法在FPGA 上實(shí)現(xiàn),可以實(shí)現(xiàn)3.2G bit/s的吞吐

2017-10-30 16:25:54 4

4 ,不利于硬件的開(kāi)發(fā)進(jìn)度。面對(duì)這一難題,文章從FPGA 的軟硬件協(xié)同測(cè)試角度出發(fā),利用PC 機(jī)和測(cè)試硬件設(shè)備的特點(diǎn),進(jìn)行FPGA 的軟硬件協(xié)同測(cè)試的設(shè)計(jì),努力實(shí)現(xiàn)FPGA 的軟硬件協(xié)調(diào)測(cè)試系統(tǒng)在軟硬件的測(cè)試和分析中的應(yīng)用。

2017-11-18 05:46:28 1616

1616 針對(duì)即時(shí)檢驗(yàn)系統(tǒng)的設(shè)計(jì)與開(kāi)發(fā)建模問(wèn)題,提出一種基于時(shí)間Petri網(wǎng)的并發(fā)系統(tǒng)建模分析方法,為即時(shí)檢驗(yàn)流程設(shè)計(jì)建立較為準(zhǔn)確的信息化模型。通過(guò)將活動(dòng)持續(xù)時(shí)間概念引入Petri網(wǎng)模型中,提出了適用于即時(shí)

2017-12-28 15:02:08 0

0 由于多棧的模型圖靈等價(jià),因此,通用的異步通信程序模型的驗(yàn)證問(wèn)題不可判定.為此,基于Petri網(wǎng)。提出了一個(gè)新的模型通信一一通信Petri網(wǎng),對(duì)異步通信程序進(jìn)行刻畫(huà).通過(guò)對(duì)輸入通信進(jìn)行缸型限制以及對(duì)

2017-12-29 15:53:03 0

0 近年來(lái),FPGA技術(shù)發(fā)展迅速,片內(nèi)集成了PLL、硬件乘法器、存儲(chǔ)器,具有了實(shí)現(xiàn)優(yōu)秀算法的充足資源。許多航空電子嵌入式圖像處理系統(tǒng)是由固定的視頻源和顯示設(shè)備組成,系統(tǒng)中圖像縮放的倍率是固定的。文中針對(duì)此展開(kāi)重點(diǎn)研究,基于FPGA硬件,實(shí)現(xiàn)固定倍率的圖像縮放。

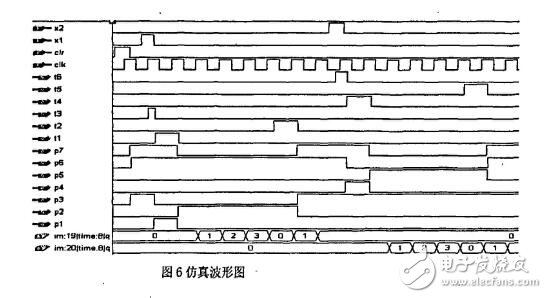

2018-08-18 09:36:50 4184

4184 Petri網(wǎng)是離散事件系統(tǒng)建模的重要工具,本文使用硬件描述語(yǔ)言VHDL實(shí)現(xiàn)了基于Petri網(wǎng)的并行控制器。文中通過(guò)一個(gè)液位控制系統(tǒng)實(shí)例具體介紹了這一方法,并通過(guò)仿真波形證明了該方法的正確性。這對(duì)于離散事件系統(tǒng)并行控制器的設(shè)計(jì)具有十分重要的意義。

2019-04-22 08:10:00 1680

1680

建立了一個(gè)基于FPGA的可實(shí)現(xiàn)流水化運(yùn)行的OFDM系統(tǒng)的硬件平臺(tái),包括模擬前端、基于FPGA的OFDM調(diào)制器和OFDM 解調(diào)器。重點(diǎn)給出了OFDM調(diào)制解調(diào)器的實(shí)現(xiàn)構(gòu)架,對(duì)FPGA實(shí)現(xiàn)方法進(jìn)行了詳細(xì)的描述,介紹了系統(tǒng)調(diào)試方法,并對(duì)系統(tǒng)進(jìn)行了性能評(píng)價(jià)。

2018-12-13 16:45:51 22

22 應(yīng)用能夠有更高的性能,您需要熟悉如下介紹的硬件。另外,將會(huì)介紹編譯優(yōu)化選項(xiàng),有助于將您的 OpenCL 應(yīng)用更好的實(shí)現(xiàn) RTL 的轉(zhuǎn)換和映射,并部署到 FPGA 上執(zhí)行。

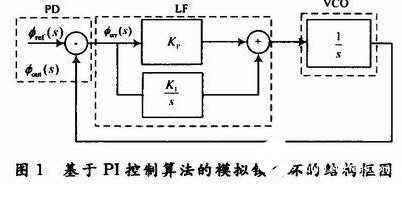

2020-07-16 17:58:28 6015

6015

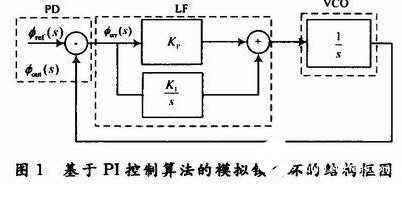

的鎖定、編譯適配下載到FPGA芯片,實(shí)現(xiàn)所設(shè)計(jì)的帶寬自適應(yīng)全數(shù)字鎖相環(huán),并完成硬件測(cè)試。在硬件測(cè)試中需要用到信號(hào)發(fā)生器和示波器,信號(hào)發(fā)生器用來(lái)產(chǎn)生鎖相環(huán)的輸入測(cè)試信號(hào),示波器用來(lái)觀測(cè)鎖相環(huán)的輸入/輸出波形。圖7為輸入信號(hào)Phi_ref取不同頻率時(shí)的實(shí)測(cè)波形。

2020-08-21 10:55:00 2158

2158

VHDL語(yǔ)言由于其其強(qiáng)大的行為描述能力及與硬件行為無(wú)關(guān)的特性,被廣泛的用于數(shù)字系統(tǒng)設(shè)計(jì),實(shí)現(xiàn)了硬件電路設(shè)計(jì)的軟件化,成為實(shí)現(xiàn)Petri網(wǎng)邏輯控制器的有力的工具。用VHDL語(yǔ)言進(jìn)行數(shù)字電路設(shè)計(jì)的很大

2020-09-22 20:46:51 691

691

在電子設(shè)計(jì)中,由于現(xiàn)場(chǎng)可編程門(mén)陣y~J(FPGA)的高邏輯密度和高可靠性以及用戶(hù)可編程性,受到了廣大硬件工程師的青睞。用FPGA來(lái)實(shí)現(xiàn)某些專(zhuān)用電路,可使整個(gè)設(shè)計(jì)更加緊湊、更小巧、靈活、穩(wěn)定、可靠

2021-01-15 15:27:00 9

9 該文在闡述了灰度圖像順序形態(tài)變換的基礎(chǔ)上,介紹了順序形態(tài)變換硬件實(shí)現(xiàn)的圖像處理系統(tǒng).該系統(tǒng)采用DSP+FPGA的框架結(jié)構(gòu),利用FPGA的可重構(gòu)特性將其中一片FPGA作為協(xié)處理器可以實(shí)現(xiàn)不同的圖像處理

2021-04-01 11:21:46 8

8 基于FPGA的RBF神經(jīng)網(wǎng)絡(luò)硬件實(shí)現(xiàn)說(shuō)明。

2021-04-28 11:24:23 25

25 基于FPGA的神經(jīng)網(wǎng)絡(luò)硬件實(shí)現(xiàn)方法說(shuō)明。

2021-06-01 09:35:16 37

37 電子發(fā)燒友網(wǎng)站提供《在FPGA上構(gòu)建EVM硬件的實(shí)現(xiàn).zip》資料免費(fèi)下載

2023-06-26 11:50:49 0

0 Petri網(wǎng)是離散事件系統(tǒng)建模的重要工具,本文使用硬件描述語(yǔ)言VHDL實(shí)現(xiàn)了基于Petri網(wǎng)的并行控制器。文中通過(guò)一個(gè)液位控制系統(tǒng)實(shí)例具體介紹了這一方法,并通過(guò)仿真波形證明了該方法的正確性。這對(duì)于離散事件系統(tǒng)并行控制器的設(shè)計(jì)具有十分重要的意義。

2023-08-03 15:33:38 299

299

電子發(fā)燒友網(wǎng)站提供《基于FPGA的RBF神經(jīng)網(wǎng)絡(luò)的硬件實(shí)現(xiàn).pdf》資料免費(fèi)下載

2023-10-23 10:21:25 0

0 FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列)屬于硬件設(shè)備,而不是軟件。它是一種可編程的硬件設(shè)備,由大量的邏輯單元、存儲(chǔ)單元和互連資源組成,能夠實(shí)現(xiàn)復(fù)雜的數(shù)字電路和系統(tǒng)設(shè)計(jì)。

2024-03-14 17:08:59 124

124

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論