完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

電子發燒友網技術文庫為您提供最新技術文章,最實用的電子技術文章,是您了解電子技術動態的最佳平臺。

所有二進制數均被表示為一個多項式,x僅是碼元位置的標記,因此我們并不關心x的取值,稱之為碼多項式。(我沒研究過CRC代數推理過程,沒體會到用多項式計算的方便之處,這里要學會的就是給出生成多項式g(x),能寫出對應的二進制即可)...

FPGA端將CSI_PCLK設置為65MHz,測試數據寫入FIFO的時鐘FIFO_WR_CLK設置為59MHz。...

賽靈思FPGA為機器學習應用提供的DSP切片的數量已從最大的Virtex 6 FPGA的約2,000個切片增加到現代Virtex UltraScale +器件的約12,000個切片。...

而且現在的LUT都是4輸入或者6輸入,可以做成邏輯門的組合,跟普通的邏輯門個數肯定不會是一對一關系。今天我們來看下這個關系如果對應。...

FPGA端實現SDIO Slave功能 a.FPGA將SDIO Master發送的2KByte數據保存至BRAM。 b.SDIO Master發起讀數據時,FPGA從BRAM讀取2KByte通過SDIO總線傳輸給SDIO Master。...

位寬變換:對于不同寬度的數據接口也可以用FIFO,例如單片機位8位數據輸出,而DSP可能是16位數據輸入,在單片機與DSP連接時就可以使用FIFO來達到數據匹配的目的。...

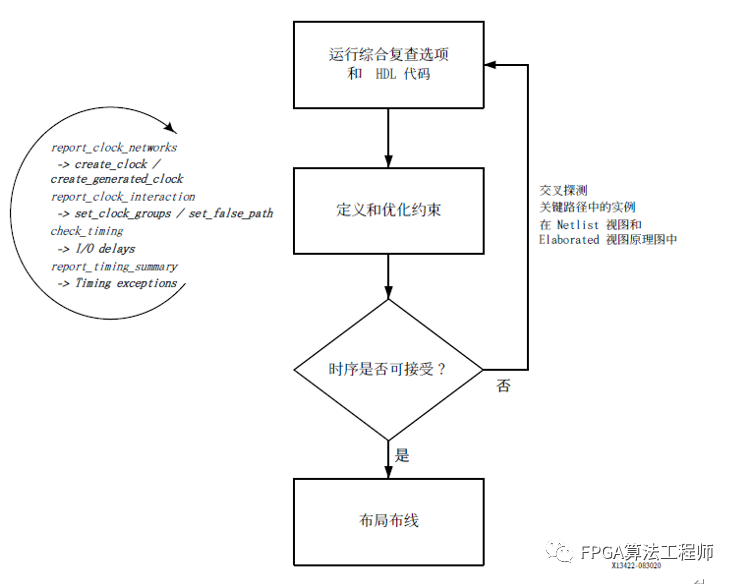

時序收斂是指設計滿足所有的時序要求。針對綜合采用正確的 HDL 和約束條件就能更易于實現時序收斂。通過選擇更合適的 HDL、約束和綜合選項,經過多個綜合階段進行迭代同樣至關重要,...

基于現場可編程門陣列 (FPGA) 的原型驗證系統已經出現多年。有些公司依賴商用原型驗證系統。然而,這些系統常常需要完全獨立地進行開發,以便在FPGA 中實現硬件設計,并提供足夠的性能來運行應用代碼。...

同步設計:。 上游數據到下游邏輯單元的傳遞是通過時鐘來同步的 -只要能滿足時延要求,就可以確保下游邏輯單元能正確采樣到_上游數據。...

計算性能相對GPU:FPGA進行整數乘法、浮點乘法運算,性能相對GPU存在數量級差距,可通過配置乘法器、浮點運算部件接近GPU計算性能。...

FIFO 是我們設計中常用的工具,因為它們使我們能夠在進行信號和圖像處理時緩沖數據。我們還使用異步FIFO來處理數據總線的時鐘域交叉問題。...

DPU目前分為SoC(Arm與ASIC協同架構)、FPGA、ASIC三種主要技術形態。基于FPGA的DPU擁有最佳的靈活性,但吞吐量、功耗在一定程度上受到限制。...

PCIE 3.0總線: 支持PCIE 3.0 X8 X4 X1模式,兼容PCIE 2.0, 最高理論帶寬8GB/s 3.SDI連接器: 使用HDBNC連接器...

基于 Xilinx 公司ZYNQ Ultrascale+ MPSoC系列 FPGA 芯片設計,應用于工廠自動化、機器視覺、工業質檢等工業領域...