完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

電子發燒友網技術文庫為您提供最新技術文章,最實用的電子技術文章,是您了解電子技術動態的最佳平臺。

在PCB設計中為了減少線間串擾,應保證線間距足夠大,當線中心間距不少于3倍線寬時,則可保持大部分電場不互相干擾,這就是3W原則。...

直角走線的對信號的影響就是主要體現在三個方面:一是拐角可以等效為傳輸線上的容性負載,減緩上升時間;二是阻抗不連續會造成信號的反射;三是直角尖端產生的EMI,到10GHz以上的RF設計領域,這些小小的直角都可能成為高速問題的重點對象。...

在對一塊完好的PCB電路板進行原理圖的逆向設計時,合理劃分功能區域能夠幫工程師減少一些不必要的麻煩,提高繪制的效率。一般而言,一塊PCB板上功能相同的元器件會集中布置,以功能劃分區域可以在反推原理圖時有方便準確的依據。...

電流流過阻抗最小路徑的概念是不正確的。電流在全部不同阻抗路徑的多少與其電導率成比例。在一個地平面,常常有不止一個大比例地電流流經的低阻抗路徑:一個路徑直接連至旁路電容;另一個在達到旁路電容前,對輸入電阻形成激勵。圖1示意了這兩個路徑。地回流電流才是真正引發問題的原因。...

在PCB板設計時,可以通過分層、恰當的布局布線和安裝實現PCB的抗ESD設計。在設計過程中,通過預測可以將絕大多數設計修改僅限于增減元器件。通過調整PCB布局布線,能夠很好地防范ESD。以下是一些常見的防范措施。...

高頻電路往往集成度較高,布線密度大,采用多層板既是布線所必須,也是降低干擾的有效手段。在PCB Layout階段,合理的選擇一定層數的印制板尺寸,能充分利用中間層來設置屏蔽,更好地實現就近接地,并有效地降低寄生電感和縮短信號的傳輸長度,同時還能大幅度地降低信號的交叉干擾等,所有這些方法都對高頻電路的...

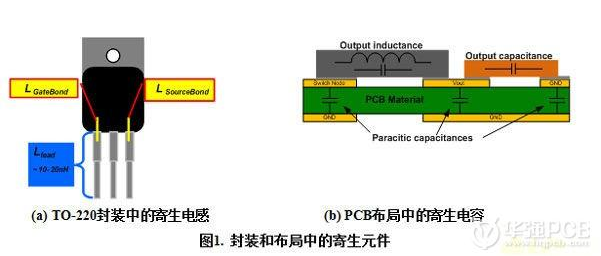

為驅動快速開關超級結MOSFET,必須了解封裝和PCB布局寄生效應對開關性能的影響,以及為使用超級結所做的PCB布局調整。主要使用擊穿電壓為500-600V的超級結MOSFET。在這些電壓額定值中,工業標準TO-220、TO-247、TO-3P和TO-263是應用最廣泛的封裝。封裝對性能的影響有限,...

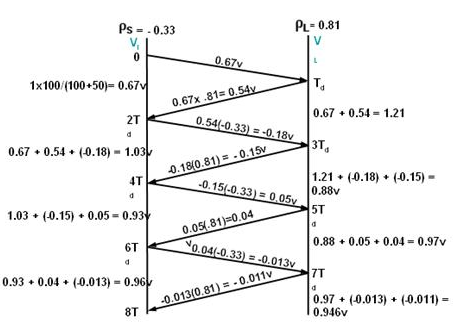

在高速電路中,信號的傳輸如上圖所示,如果一根走線沒有被正確終結(終端匹配),那么來自于驅動端的信號脈沖在接收端被反射,從而引發不可預期效應,使信號輪廓失真。當失真變形非常顯著時可導致多種錯誤,引起設計失敗。同時,失真變形的信號對噪聲的敏感性增加了,也會引起設計失敗。如果上述情況沒有被足夠考慮,EMI...

在核芯結構中,PCB板中的所有導電層敷在核芯材料上;而在敷箔結構中,只有PCB板內部導電層才敷在核芯材料上,外導電層用敷箔介質板。所有的導電層通過介質利用多層層壓工藝粘合在一起。...

智能時代的到來,不僅給普通人的生活帶來了便利,也對各行業產生了深刻的影響。為了使得PCB有高可靠性,必然要對PCB抄板、設計提出更高的要求。例如智能化產品對器件品質的要求、對密度散熱的要求、對無處不在的物聯網通信的要求,而智能化生產對柔性設備的要求、對智能機械的要求、對復雜環境的要求等等。...

最有效的電路板堆疊方法是將主接地面(主地)安排在表層下的第二層,并盡可能將RF線走在表層上。將RF路徑上的過孔尺寸減到最小不僅可以減少路徑電感,而且還可以減少主地上的虛焊點,并可減少RF能量泄漏到層疊板內其他區域的機會。在物理空間上,像多級放大器這樣的線性電路通常足以將多個RF區之間相互隔離開來,但...

在PCB板的設計當中,可以通過分層、恰當的布局布線和安裝實現PCB的抗ESD設計。在設計過程中,通過預測可以將絕大多數設計修改僅限于增減元器件。通過調整PCB布局布線,能夠很好地防范ESD。以下是一些常見的防范措施。...

在元器件的布局方面,應該把相互有關的元件盡量放得靠近一些,例如,時鐘發生器、晶振、CPU的時鐘輸入端都易產生噪聲,在放置的時候應把它們靠近些。對于那些易產生噪聲的器件、小電流電路、大電流電路開關電路等,應盡量使其遠離單片機的邏輯控制電路和存儲電路(ROM、RAM),如果可能的話,可以將這些電路另外制...

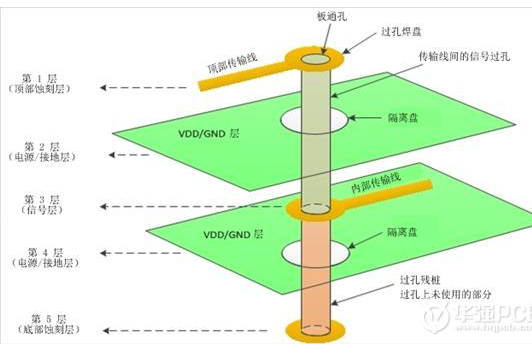

過孔是鍍在電路板頂層與底層之間的通孔外的金屬圓柱體。信號過孔連接不同層上的傳輸線。過孔殘樁是過孔上未使用的部分。過孔焊盤是圓環狀墊片,它們將過孔連接至頂部或內部傳輸線。隔離盤是每個電源或接地層內的環形空隙,以防止到電源和接地層的短路。...

無論是在制造組裝流程還是在實際使用中,PCB都要具有可靠的性能,這一點至關重要。除相關成本外,組裝過程中的缺陷可能會由PCB帶進最終產品,在實際使用過程中可能會發生故障,導致索賠。因此,從這一點來看,可以毫不為過地說,一塊優質PCB的成本是可以忽略不計的。在所有細分市場,特別是生產關鍵應用領域的產品...

1、如果設計的電路系統中包含FPGA器件,則在繪制原理圖前必需使用Quartus II軟件對管腳分配進行驗證。(FPGA中某些特殊的管腳是不能用作普通IO的)。 2、4層板從上到下依次為:信號平面層、地、電源、信號平面層;6層板從上到下依次為:信號平面層、地、信號內電層、信號內電層、電源、信號...

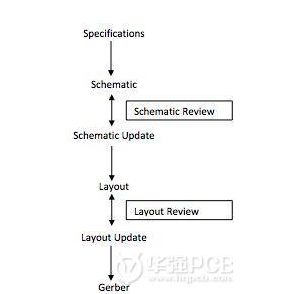

前面三個步驟花的時間最多,因為原理圖檢查是一個手工過程。想像一個具有1000條甚至更多連線的SoC電路板。人工檢查每一根連線是冗長乏味的一項任務。事實上,檢查每根連線幾乎是不可能的,因而會導致最終電路板出問題,比如錯誤的連線、懸浮節點等。...

一、資料輸入階段 1.在流程上接收到的資料是否齊全 2.確認PCB模板是最新的 3. 確認模板的定位器件位置無誤 4.PCB設計說明以及PCB設計或更改要求、標準化要求說明是否明確 5.確認外形圖上的禁止布放器件和布線區已在PCB模板上體現 6.比較外形圖,確認P...

PCB布局規則: 1、在通常情況下,所有的元件均應布置在電路板的同一面上,只有頂層元件過密時,才能將一些高度有限并且發熱量小的器件,如貼片電阻、貼片電容、貼片IC等放在低層。 2、在保證電氣性能的前提下,元件應放置在柵格上且相互平行或垂直排列,以求整齊、美觀,在一般情況下不允許元件重疊;...

PageUp:以鼠標為中心放大 PageDown:以鼠標為中心縮小。 Home:將鼠標所指的位置居中 End:刷新(重畫) *:頂層與底層之間層的切換 +(-)逐層切換:“+”與“-”的方向相反 Qmm(毫米)與mil(密爾)的單位切換 IM:測量兩點間的距...