完善資料讓更多小伙伴認識你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > fpga

FPGA(Field-Programmable Gate Array),即現(xiàn)場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進一步發(fā)展的產(chǎn)物。它是作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點。

文章:12576個 瀏覽:617558次 帖子:7893個

JESD204B協(xié)議相關(guān)介紹與具體應(yīng)用實例

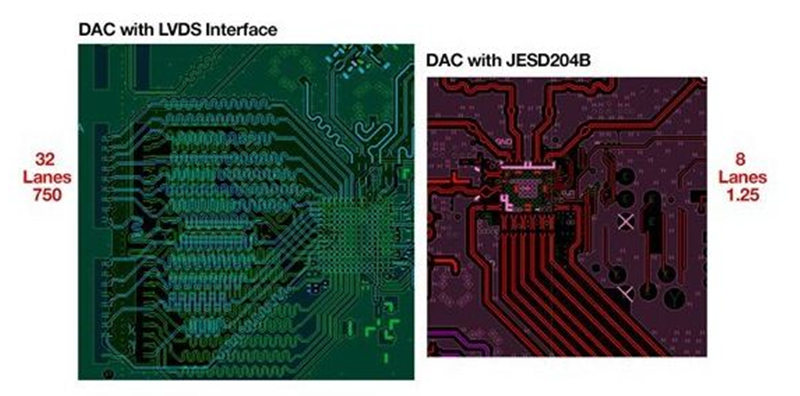

接觸過FPGA高速數(shù)據(jù)采集設(shè)計的朋友,應(yīng)該會聽過新術(shù)語“JESD204B”。這是一種新型的基于高速SERDES的ADC/DAC數(shù)據(jù)傳輸接口。隨著ADC/...

隨著電子技術(shù)的不斷發(fā)展,傳統(tǒng)的頻率合成技術(shù)逐漸不能滿足人們對于頻率轉(zhuǎn)換速度、頻率分辨率等方面的追求,直接數(shù)字頻率合成技術(shù)應(yīng)運而生。

2022-07-03 標(biāo)簽:fpga轉(zhuǎn)換器頻率 2172 0

之前很多人問我有沒有好的代碼可以參考,我之前一直推薦的是官方的IP參考例程/IP源碼,但是不知道大家有沒有看過官方的項目例程,看下下圖:

鎖存器是電平觸發(fā)的存儲單元,數(shù)據(jù)存儲的動作取決于輸入時鐘(或者使能)信號的電平值,僅當(dāng)鎖存器處于使能狀態(tài)時,輸出才會隨著數(shù)據(jù)輸入發(fā)生變化。

CN0549 CbM 平臺在開發(fā)應(yīng)用程序時為設(shè)計人員提供系統(tǒng)靈活性和大量軟件資源。圍繞如何利用不同的組件進行 CbM 和預(yù)測性維護 (PdM) 開發(fā)...

2022-07-01 標(biāo)簽:fpga調(diào)制解調(diào)器微處理器 1356 0

FPGA芯片設(shè)計企業(yè)安路科技發(fā)布2022第一季度報告

FPGA芯片設(shè)計企業(yè)上海安路信息科技股份有限公司發(fā)布2022第一季度報告,具體內(nèi)容如下。 一、 主要財務(wù)數(shù)據(jù) (一)主要會計數(shù)據(jù)和財務(wù)指標(biāo) 單位:元 幣...

不論是CNN還是RNN,一個共同特點是整個網(wǎng)絡(luò)是由幾個相同的單元聯(lián)結(jié)形成的。CNN中基本的單元是神經(jīng)元,一個神經(jīng)元包含一個權(quán)重和激活函數(shù),其中權(quán)重是對輸...

隨著工業(yè)自動化水平的迅速提高以及計算機技術(shù)在工業(yè)領(lǐng)域的不斷應(yīng)用,人們對工業(yè)自動化技術(shù)的要求越來越高,工業(yè)控制器在設(shè)計上正朝著嵌入式系統(tǒng)方向發(fā)展。

下一個級別,TrustFLEXv,提供了使用客戶選擇的證書頒發(fā)機構(gòu)的靈活性,同時仍然受益于預(yù)配置的用例。對于那些想要完全定制他們的產(chǎn)品的人,Trus...

2022-06-30 標(biāo)簽:fpga物聯(lián)網(wǎng) 1272 0

Arria 10 SoC確保系統(tǒng)設(shè)計滿足現(xiàn)在和未來性能要求

借助 Arria 10 SoC,您可以通過將 GHz 級處理器、FPGA 邏輯和數(shù)字信號處理 (DSP) 集成到單個可定制的片上系統(tǒng)中來減小電路板尺...

整個過程是一系列連續(xù)的改進,從快速 TLM 模型開始,在可用時添加更多硬件細節(jié),同時保持足夠快的運行時以進行軟件開發(fā)。

不僅如此,32 位 ARM 生態(tài)系統(tǒng)提供了統(tǒng)一的結(jié)構(gòu),使代碼搜索變得更加容易,并使嵌入式軟件商店成為主要目的地。許多產(chǎn)品都提供評估版本,具有預(yù)打包配...

中科億海微:芯有靈犀 智創(chuàng)未來,世界FPGA珠峰攀登者

中科院團隊:托舉行業(yè)新星 中科億海微電子科技(蘇州)有限公司(企業(yè)官網(wǎng):http://www.ehiway.cn/)是中科院空天信息創(chuàng)新研究院“可編程芯...

parameter關(guān)鍵字定義模塊特定的參數(shù),該參數(shù)在特定模塊實例的范圍生效。參數(shù)用于為模塊實例提供不同的自定義,例如,輸入或輸出端口的寬度。以下是使用p...

LVDS電平以及LVDS25電平能否約束到這個BANK上呢?

當(dāng)兩個banks的I/O口作為LVDS電平時,HR banks的I/O電壓VCCO只能為2.5V,HP banks的I/O口電壓為1.8V。兩個bank...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |