說(shuō)說(shuō)latch與verilog的聯(lián)系。

還是照慣例,首先必須放上關(guān)于latch的定義和解釋。ALTERA 的recommended HDL coding中提到:

A latch is a small combinational loop that holds the value of a signal until a new value is assigned.

從上可以看出,latch是一個(gè)記憶元件或者說(shuō)是存儲(chǔ)單元,他能保持信號(hào)的值

同時(shí)在網(wǎng)上找了找關(guān)于latch的中文定義。

鎖存器是電平觸發(fā)的存儲(chǔ)單元,數(shù)據(jù)存儲(chǔ)的動(dòng)作取決于輸入時(shí)鐘(或者使能)信號(hào)的電平值,僅當(dāng)鎖存器處于使能狀態(tài)時(shí),輸出才會(huì)隨著數(shù)據(jù)輸入發(fā)生變化。

從一般情況來(lái)看,鎖存器多數(shù)是有電平鎖存的。當(dāng)電平無(wú)效時(shí),輸出信號(hào)隨輸入信號(hào)變化,就像通過(guò)了緩沖器;當(dāng)電平有效時(shí),輸出信號(hào)被鎖存。

看了很多關(guān)于verilog的語(yǔ)法資料,大多其中并沒(méi)有談到latch,latch和verilog發(fā)生聯(lián)系是在用verilog進(jìn)行FPGA或者ASIC設(shè)計(jì)時(shí)。而在此由于本人正式學(xué)習(xí)用verilog進(jìn)行FPGA設(shè)計(jì),

而涉及到的書(shū)中均提到要采用同步設(shè)計(jì),避免采用latch。從網(wǎng)上找了找為什么不使用latch的原因:

不要鎖存器的原因有二:1、鎖存器容易產(chǎn)生毛刺,2、鎖存器在A(yíng)SIC設(shè)計(jì)中應(yīng)該說(shuō)比f(wàn)f要簡(jiǎn)單,但是在FPGA的資源中,大部分器件沒(méi)有鎖存器這個(gè)東西,所以需要用一個(gè)邏輯門(mén)和ff來(lái)組成鎖存器,這樣就浪費(fèi)了資源。3、鎖存器的出現(xiàn)使得靜態(tài)時(shí)序分析變得更加復(fù)雜

所以又可以得出一條指導(dǎo)性的原則:

在能使用DFF或者寄存器的時(shí)候,堅(jiān)決不使用latch

說(shuō)了latch的定義和latch的危害,現(xiàn)在要來(lái)說(shuō)說(shuō)latch的產(chǎn)生和避免

查閱資料,結(jié)合自己的理解,總結(jié)出無(wú)意生成latch的三大原因:

1、不完整的if或者case結(jié)構(gòu)

2、不完整的敏感信號(hào)列表

latch的出現(xiàn)總是與不完整有關(guān),組合電路本應(yīng)該是完整的,最理想的寫(xiě)法可能是一個(gè)輸入對(duì)應(yīng)一個(gè)輸出,當(dāng)一個(gè)輸入沒(méi)有相應(yīng)的輸出或者引起輸出的信號(hào)沒(méi)有作為輸入的時(shí)候,Latch產(chǎn)生了!

先解釋第一點(diǎn)不完整的if結(jié)構(gòu),例如:

if(a)

begin

out = 1'b1;

end

當(dāng)a為1時(shí)輸出為1,當(dāng)a為0時(shí)由于沒(méi)有相應(yīng)的譯碼語(yǔ)句,所以輸出將保持,此時(shí)將生成latch而不是原來(lái)想要的組合電路。

而對(duì)于不完整的case語(yǔ)句,例如:

always@( * )

case(a)

3'b000: b = 8'd1;

3'b001: b = 8'd5;

3'b010: b = 8'd8;

3'b011: b = 8'd17;

endcase

此時(shí)語(yǔ)句中沒(méi)有default,當(dāng)a為4、5、6、7時(shí)沒(méi)有響應(yīng)的譯碼語(yǔ)句,輸出將保持,此時(shí)將生成latch。

對(duì)于第二點(diǎn)不完整的敏感信號(hào)表,夏雨聞老師的書(shū)中有提到:

如是說(shuō)道:在賦值表達(dá)式右邊參與賦值的信號(hào)都必須在always@(敏感電平列表)中列出。

如果在賦值表達(dá)式右端引用了敏感電平列表中沒(méi)有列出的信號(hào),那么在綜合時(shí),將會(huì)為該沒(méi)有列出的信號(hào)隱含地產(chǎn)生一個(gè)透明鎖存器。

所以得出指導(dǎo)性的原則:

務(wù)必寫(xiě)好if和case所有的分支,務(wù)必寫(xiě)全敏感信號(hào)列表!

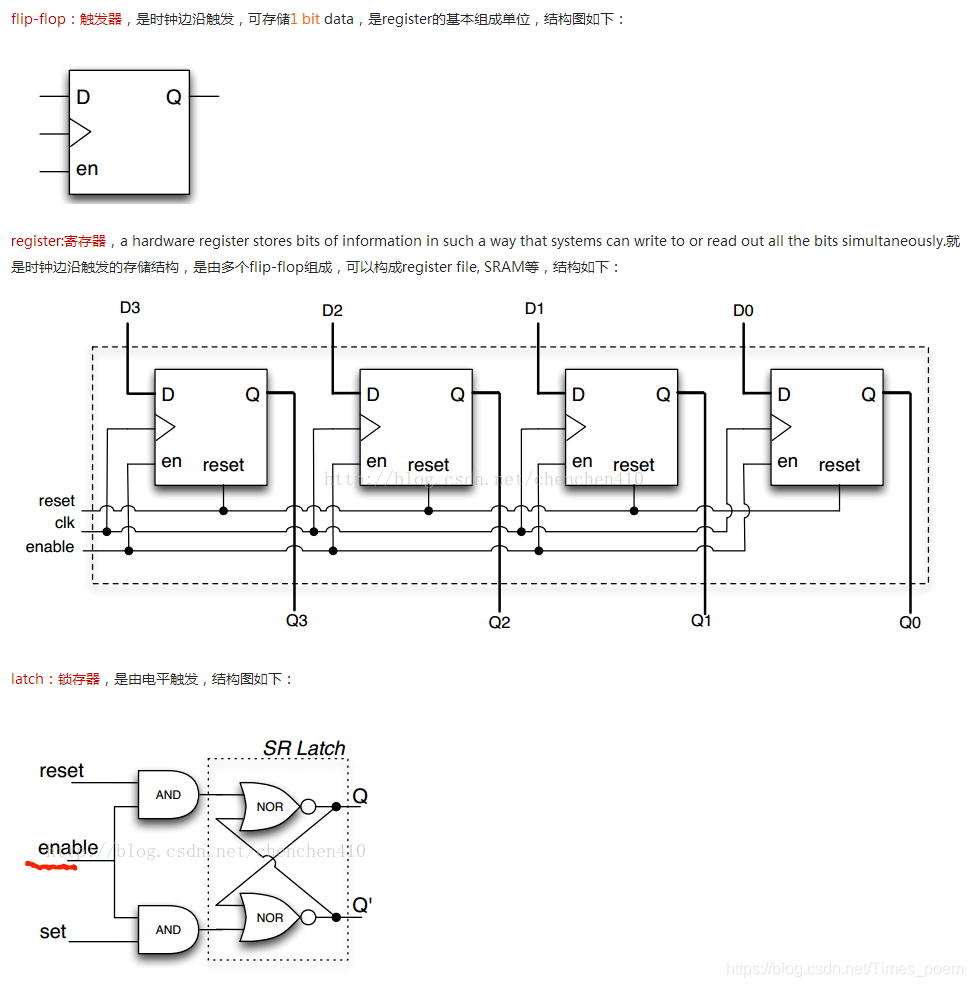

關(guān)于硬件中常見(jiàn)的基本存儲(chǔ)元件的定義、中英文對(duì)應(yīng)的名字會(huì)模糊,今天特地查明具體定義。

觸發(fā)器:flipflop

鎖存器:latch

寄存器:register

鎖存器是電平觸發(fā)的存儲(chǔ)單元,數(shù)據(jù)存儲(chǔ)的動(dòng)作取決于輸入時(shí)鐘(或者使能)信號(hào)的電平值,僅當(dāng)鎖存器處于使能狀態(tài)時(shí)輸出才會(huì)隨著數(shù)據(jù)輸入發(fā)生變化。

觸發(fā)器是邊沿敏感的存儲(chǔ)單元,數(shù)據(jù)存儲(chǔ)的動(dòng)作由某一信號(hào)的上升或者下降沿進(jìn)行同步的。

寄存器用來(lái)存放數(shù)據(jù)的一些小型存儲(chǔ)區(qū)域,用來(lái)暫時(shí)存放參與運(yùn)算的數(shù)據(jù)和運(yùn)算結(jié)果。其實(shí)寄存器就是一種常用的時(shí)序邏輯電路,但這種時(shí)序邏輯電路只包含存儲(chǔ)電路。寄存器的存儲(chǔ)電路是由鎖存器或觸發(fā)器構(gòu)成的,因?yàn)橐粋€(gè)鎖存器或觸發(fā)器能存儲(chǔ)1位二進(jìn)制數(shù),所以由N個(gè)鎖存器或觸發(fā)器可以構(gòu)成N位寄存器。觸發(fā)器是在時(shí)鐘的沿進(jìn)行數(shù)據(jù)的鎖存的,而鎖存器是用電平使能來(lái)鎖存數(shù)據(jù)的。所以觸發(fā)器的Q輸出端在每一個(gè)時(shí)鐘沿都會(huì)被更新,而鎖存器只能在使能電平有效器件才會(huì)被更新。有一些教科書(shū)里的觸發(fā)器實(shí)際是鎖存器。在FPGA設(shè)計(jì)中建議如果不是必須那么應(yīng)該盡量使用觸發(fā)器而不是鎖存器。

鐘控D觸發(fā)器其實(shí)就是D鎖存器,邊沿D觸發(fā)器才是真正的D觸發(fā)器,鐘控D觸發(fā)器在使能情況下輸出隨輸入變化,邊沿觸發(fā)器只有在邊沿跳變的情況下輸出才變化。

20、D 觸發(fā)器和D 鎖存器的區(qū)別。

兩個(gè)鎖存器可以構(gòu)成一個(gè)觸發(fā)器,歸根到底還是dff是邊沿觸發(fā)的,而latch是電平觸發(fā)的。鎖存器的輸出對(duì)輸入透明的,輸入是什么,輸出就是什么,這就是鎖存器不穩(wěn)定的原因,而觸發(fā)器是由兩個(gè)鎖存器構(gòu)成的一個(gè)主從觸發(fā)器,輸出對(duì)輸入是不透明的,必須在時(shí)鐘的上升/下降沿才會(huì)將輸入體現(xiàn)到輸出,所以能夠消除輸入的毛刺信號(hào)。

21、latch和filp-flop的異同

都是時(shí)序邏輯,但latch受所有的輸入信號(hào)控制,只要輸入信號(hào)變化,latch就變化。也正因?yàn)槿绱耍琹atch很容易出毛刺。

flip-flop是觸發(fā)器,只有在被時(shí)鐘觸發(fā)時(shí)才采樣當(dāng)前的輸入,產(chǎn)生輸出。如果使用門(mén)電路來(lái)搭建latch和ff,則latch消耗的門(mén)資源比f(wàn)f要少。但是你用的如果是 fpga,那么內(nèi)部一般帶DFF單元,反而用觸發(fā)器更好。

22、latch與register的區(qū)別,

為什么現(xiàn)在多用register.行為級(jí)描述中l(wèi)atch如何產(chǎn)生的行為級(jí)描述中l(wèi)atch一般是由于if或case邏輯表述不完全產(chǎn)生的。

異同:

1、 latch由電平觸發(fā),非同步控制。在使能信號(hào)有效時(shí)latch相當(dāng)于通路,在使能信號(hào)無(wú)效時(shí)latch保持輸出狀態(tài)。

DFF由時(shí)鐘沿觸發(fā),同步控制。

2、 latch容易產(chǎn)生毛刺(glitch),DFF則不易產(chǎn)生毛刺。

3、如果使用門(mén)電路來(lái)搭建latch和DFF,則latch消耗的門(mén)資源比DFF要少,這是latch比DFF優(yōu)越的地方。所以,在A(yíng)SIC中使用 latch的集成度比DFF高。

但在FPGA中正好相反,因?yàn)镕PGA中沒(méi)有標(biāo)準(zhǔn)的latch單元,但有DFF單元,一個(gè)LATCH需要多個(gè)LE才能實(shí)現(xiàn)。

4、 latch將靜態(tài)時(shí)序分析變得極為復(fù)雜。

一般的設(shè)計(jì)規(guī)則是:在絕大多數(shù)設(shè)計(jì)中避免產(chǎn)生latch。它會(huì)讓您設(shè)計(jì)的時(shí)序完蛋,并且它的隱蔽性很強(qiáng),非老手不能查出。latch最大的危害在于不能過(guò)濾毛刺。這對(duì)于下一級(jí)電路是極其危險(xiǎn)的。所以,只要能用D觸發(fā)器的地方,就不用latch。有些地方?jīng)]有時(shí)鐘,也只能用latch了。比如現(xiàn)在用一個(gè)clk接到latch的使能端(假設(shè)是高電平使能),這樣需要的setup時(shí)間,就是數(shù)據(jù)在時(shí)鐘的下降沿之前需要的時(shí)間,但是如果是一個(gè)DFF,那么setup時(shí)間就是在時(shí)鐘的上升沿需要的時(shí)間。這就說(shuō)明如果數(shù)據(jù)晚于控制信號(hào)的情況下,只能用 latch,這種情況就是,前面所提到的latch timing borrow。基本上相當(dāng)于借了一個(gè)高電平時(shí)間。也就是說(shuō),latch借的時(shí)間也是有限的。

關(guān)于latch的討論 latch和flip-flop都是時(shí)序邏輯,區(qū)別為:

latch同其所有的輸入信號(hào)相關(guān),當(dāng)輸入信號(hào)變化時(shí)latch就變化,沒(méi)有時(shí)鐘端;

flip- flop受時(shí)鐘控制,只有在時(shí)鐘觸發(fā)時(shí)才采樣當(dāng)前的輸入,產(chǎn)生輸出。當(dāng)然因?yàn)槎叨际菚r(shí)序邏輯,所以輸出不但同當(dāng)前的輸入相關(guān)還同上一時(shí)間的輸出相關(guān)。

1、沒(méi)有時(shí)鐘端,不受系統(tǒng)同步時(shí)鐘的控制,無(wú)法實(shí)現(xiàn)同步操作;

2、對(duì)輸入電平敏感,受布線(xiàn)延遲影響較大,很難保證輸出沒(méi)有毛刺產(chǎn)生;

在 xilinx和altera器件的slice和LE中都能夠同時(shí)支持生產(chǎn)d-latch和d-ff,在這一層面上二者有什么區(qū)別暫時(shí)沒(méi)有想到。如果使用門(mén)電路來(lái)搭建latch和ff,則latch消耗的門(mén)資源比f(wàn)f要少,這是latch比f(wàn)f優(yōu)越的地方。latch的最大缺點(diǎn)就是沒(méi)有時(shí)鐘端,和當(dāng)前我們盡可能采用時(shí)序電路的設(shè)計(jì)思路不符。latch是電平觸發(fā),相當(dāng)于有一個(gè)使能端,且在激活之后(在使能電平的時(shí)候)相當(dāng)于導(dǎo)線(xiàn)了,隨輸出而變化,在非使能狀態(tài)下是保持原來(lái)的信號(hào),這就可以看出和flip-flop的差別,其實(shí)很多時(shí)候latch是不能代替ff的

1.latch對(duì)毛刺敏感

2.在A(yíng)SIC中使用latch的集成度比DFF高,但在FPGA中正好相反,因?yàn)镕PGA中沒(méi)有標(biāo)準(zhǔn)的latch單元,但有DFF單元,一個(gè)LATCH需要多個(gè)LE才能實(shí)現(xiàn)

3.latch將靜態(tài)時(shí)序分析變得極為復(fù)雜

4. 目前l(fā)atch只在極高端電的路中使用,如intel 的P4等CPU。FPGA中有l(wèi)atch單元,寄存器單元就可以配置成latch單元,在xilinx v2p的手冊(cè)將該單元成為register/latch單元,附件是xilinx半個(gè)slice的結(jié)構(gòu)圖。其它型號(hào)和廠(chǎng)家的FPGA沒(méi)有去查證。——個(gè)人認(rèn)為xilinx是能直接配的而altera或許比較麻煩,要幾個(gè)LE才行,然而也非xilinx的器件每個(gè)slice都可以這樣配置altera的只有DDR接口中有專(zhuān)門(mén)的latch單元,一般也只有高速電路中會(huì)采用latch的設(shè)計(jì)。altera的LE是沒(méi)有l(wèi)atch的結(jié)構(gòu)的又查了sp3和sp2e,別的不查了,手冊(cè)上說(shuō)支持這種配置。有關(guān)altera的表述wangdian說(shuō)的對(duì),altera的ff不能配置成latch,它使用查找表來(lái)實(shí)現(xiàn)latch,

一般的設(shè)計(jì)規(guī)則是:在絕大多數(shù)設(shè)計(jì)中避免產(chǎn)生LATCH.它會(huì)讓您設(shè)計(jì)的時(shí)序完蛋,并且它的隱蔽性很強(qiáng),非老手不能查出.latch最大的危害在于不能過(guò)濾毛刺。這對(duì)于下一級(jí)電路是極其危險(xiǎn)的。所以,只要能用D觸發(fā)器的地方,就不用latch。有些地方?jīng)]有時(shí)鐘,也只能用latch了。

對(duì)latch進(jìn)行STA的分析其實(shí)也是可以,但是要對(duì)工具相當(dāng)熟悉才行.不過(guò)很容易出錯(cuò).當(dāng)前PrimeTime,是支持進(jìn)行l(wèi)atch分析的.現(xiàn)在一些綜合工具內(nèi)置的STA分析功能也支持比如RTL compiler, Design Compiler. 除了ASIC里可以節(jié)省資源以外。我感覺(jué)latch這個(gè)東西在同步設(shè)計(jì)里出現(xiàn)的可能還是挺小的吧,現(xiàn)在處理過(guò)程中大都放在ff里打一下,影響不太大吧

標(biāo)簽:無(wú)標(biāo)簽latch與DFF的區(qū)別收集了一下網(wǎng)上資源,總結(jié)如下:

1、latch由電平觸發(fā),非同步控制。在使能信號(hào)有效時(shí)latch相當(dāng)于通路,在使能信號(hào)無(wú)效時(shí)latch保持輸出狀態(tài)。DFF由時(shí)鐘沿觸發(fā),同步控制。

2、latch容易產(chǎn)生毛刺(glitch),DFF則不易產(chǎn)生毛刺。

3、如果使用門(mén)電路來(lái)搭建latch和DFF,則latch消耗的門(mén)資源比DFF要少,這是latch比DFF優(yōu)越的地方。所以,在A(yíng)SIC中使用latch的集成度比DFF高,但在FPGA中正好相反,因?yàn)镕PGA中沒(méi)有標(biāo)準(zhǔn)的latch單元,但有DFF單元,一個(gè)LATCH需要多個(gè)LE才能實(shí)現(xiàn)。

4、latch將靜態(tài)時(shí)序分析變得極為復(fù)雜。一般的設(shè)計(jì)規(guī)則是:在絕大多數(shù)設(shè)計(jì)中避免產(chǎn)生latch。它會(huì)讓您設(shè)計(jì)的時(shí)序完蛋,并且它的隱蔽性很強(qiáng),非老手不能查出。latch最大的危害在于不能過(guò)濾毛刺。這對(duì)于下一級(jí)電路是極其危險(xiǎn)的。所以,只要能用D觸發(fā)器的地方,就不用latch。有些地方?jīng)]有時(shí)鐘,也只能用latch了。比如現(xiàn)在用一個(gè)clk接到latch的使能端(假設(shè)是高電平使能),這樣需要的setup時(shí)間,就是數(shù)據(jù)在時(shí)鐘的下降沿之前需要的時(shí)間,但是如果是一個(gè)DFF,那么setup時(shí)間就是在時(shí)鐘的上升沿需要的時(shí)間。這就說(shuō)明如果數(shù)據(jù)晚于控制信號(hào)的情況下,只能用 latch,這種情況就是,前面所提到的latch timing borrow。基本上相當(dāng)于借了一個(gè)高電平時(shí)間。也就是說(shuō),latch借的時(shí)間也是有限的。在if語(yǔ)句和case不全很容易產(chǎn)生latch,需要注意。VIA題目這兩個(gè)代碼哪個(gè)綜合更容易產(chǎn)生latch:

代碼1

always@(enableorinaorinb)

begin

if(enable)begin

data_out=ina;

end

elsebegin

data_out=inb;

end

end

代碼2

input[3:0]data_in;

always@(data_in)

begin

case(data_in)

0:out1=1'b1;

1,3:out2=1'b1;

2,4,5,6,7:out3=1'b1;

default:out4=1'b1;

endcase

end

答案是代碼2在綜合時(shí)更容易產(chǎn)生latch。

使用條件語(yǔ)句不當(dāng)在設(shè)計(jì)中生成了原本沒(méi)有想到的鎖存器:、

例1:在一個(gè)always語(yǔ)句中不正確使用if語(yǔ)句

Always@(alord)always@(alord)

begin begin

if(al)q<=?d;??????????????????????????????????? if(al)?q?<=?d;

end elseq<=?0;

end

在這個(gè)always塊中,if語(yǔ)句只保證了當(dāng)al=1時(shí)q才取d的值。這段程序并沒(méi)有給出當(dāng)al=0時(shí)q的取值,那么當(dāng)al=0時(shí)q取何值?在always塊中在給定的條件下變量沒(méi)有被賦值,那么變量將保持原值,也就是說(shuō)將會(huì)生成一個(gè)鎖存器。

如果當(dāng)設(shè)計(jì)人員希望當(dāng)al=0時(shí),q的值為0,則else項(xiàng)就必不可少了。請(qǐng)注意看右邊的always塊,整個(gè)verilog程序模塊綜合出來(lái)后,always塊對(duì)應(yīng)的部分不會(huì)生成鎖存器。

Verilog HDL程序的另一種偶然生成鎖存器是在使用case語(yǔ)句時(shí)缺少default項(xiàng)的情況下發(fā)生的。

Case語(yǔ)句的功能是:在某個(gè)信號(hào)取不同的值時(shí),給另一個(gè)信號(hào)賦不同的值。如下,如果sel=00,q取a值,而sel=11,q取b值。這個(gè)例子不清楚的是:如果sel取00和11以外的值時(shí)q將賦予什么值?在這個(gè)例子中,默認(rèn)q保持原值,這就會(huì)自動(dòng)生成鎖存器。

always@(sel[1:0]oraorb)always@(sel[1:0]oraorb)

case(sel[1:0])case(sel[1:0])

2’b00:q<=?a;????????????????????????????2’b00:??q?<=?a;

2’b11:q<=?b;????????????????????????????2’b11:??q?<=?b;

endcase default:q<=?‘b0;???????

endcase

有鎖存器無(wú)鎖存器

避免生成鎖存器的方法:如果用到if語(yǔ)句,最好寫(xiě)上sles項(xiàng);如果用case語(yǔ)句,最好寫(xiě)上default項(xiàng)。遵循上面兩條原則,就可以避免發(fā)生這種錯(cuò)誤,使設(shè)計(jì)者更加明確設(shè)計(jì)目標(biāo),同時(shí)也增強(qiáng)了verilog程序的可讀性。

原文標(biāo)題:FPGA學(xué)習(xí)-verilog(flipflop和latch以及register的區(qū)別)

文章出處:【微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

FPGA

+關(guān)注

關(guān)注

1645文章

22034瀏覽量

617892 -

寄存器

+關(guān)注

關(guān)注

31文章

5433瀏覽量

124318 -

硬件

+關(guān)注

關(guān)注

11文章

3481瀏覽量

67454 -

鎖存器

+關(guān)注

關(guān)注

8文章

925瀏覽量

42333

原文標(biāo)題:FPGA學(xué)習(xí)-verilog(flipflop和latch以及register的區(qū)別)

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

【HarmonyOS 5】鴻蒙中常見(jiàn)的標(biāo)題欄布局方案

連接器元件的定義和結(jié)構(gòu)特點(diǎn)

數(shù)字電路中常見(jiàn)組件

Altium Designer 15.0自定義元件設(shè)計(jì)

電網(wǎng)中常見(jiàn)的影響電能質(zhì)量

常見(jiàn)的PCB元件封裝類(lèi)型

常見(jiàn)手插元件識(shí)別

什么是ROM存儲(chǔ)器的定義

emc軟件定義存儲(chǔ)的未來(lái)發(fā)展

放大電路中常見(jiàn)的噪聲有哪些

電感元件的伏安關(guān)系是什么

電感元件和電容元件有什么異同

伺服閉環(huán)系統(tǒng)中常見(jiàn)的檢測(cè)元件包括什么

硬件中常見(jiàn)的基本存儲(chǔ)元件的定義

硬件中常見(jiàn)的基本存儲(chǔ)元件的定義

評(píng)論