完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

標簽 > fpga

FPGA(Field-Programmable Gate Array),即現場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。

文章:12615個 瀏覽:619471次 帖子:7913個

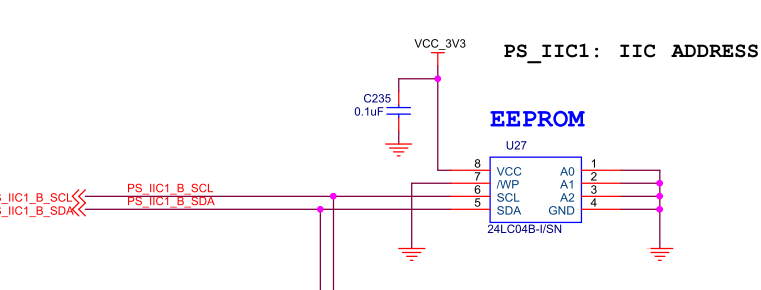

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十二章PS端I2C的使用

ReadBuffer清0,WriteBuffer賦FF寫16個字節到EEPROM讀EEPROM的16個字節到ReadBuffer檢驗是否正確Readbu...

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十一章PS端UART讀寫控制

除了打印信息之外,如果我們想用UART進行數據傳輸呢?本章便來介紹PS端UART的讀寫控制,實驗中,每隔1S向外發送一串字符,如果收到數據,產生中斷,并...

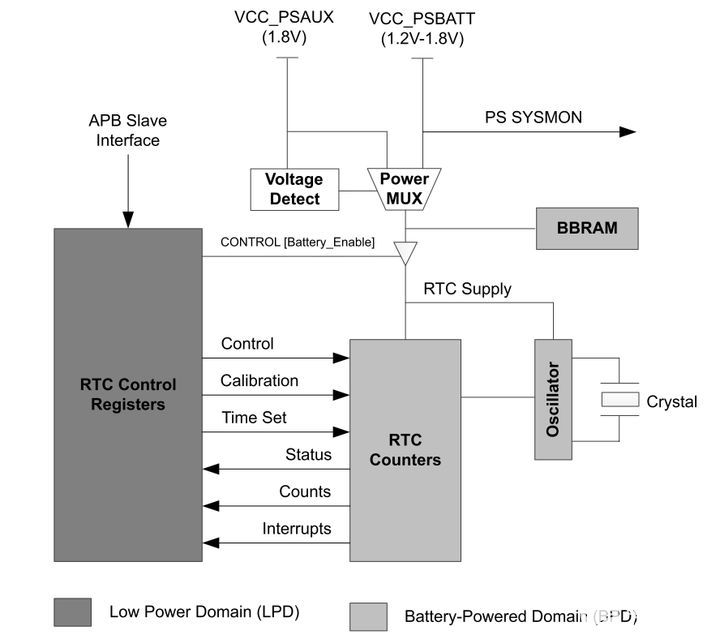

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十章PS端RTC中斷實驗

實驗中通過簡單的修改Vitis的例程,就完成了RTC,中斷的應用,看似簡單的操作,但蘊含了豐富的知識,我們需要非常了解RTC的原理、中斷的原理,這些基本...

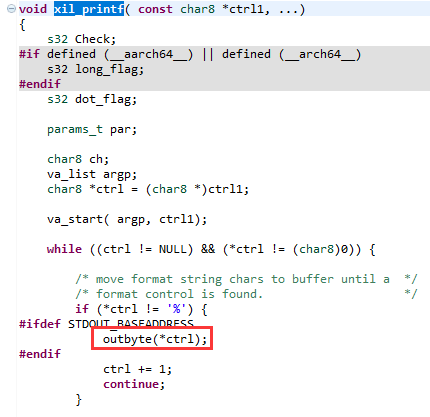

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十九章 Hello World(下)

本章從FPGA工程師和軟件工程師兩者角度出發,介紹了ZYNQ開發的經典流程,FPGA工程師的主要工作是搭建好硬件平臺,提供硬件描述文件hdf給軟件工程師...

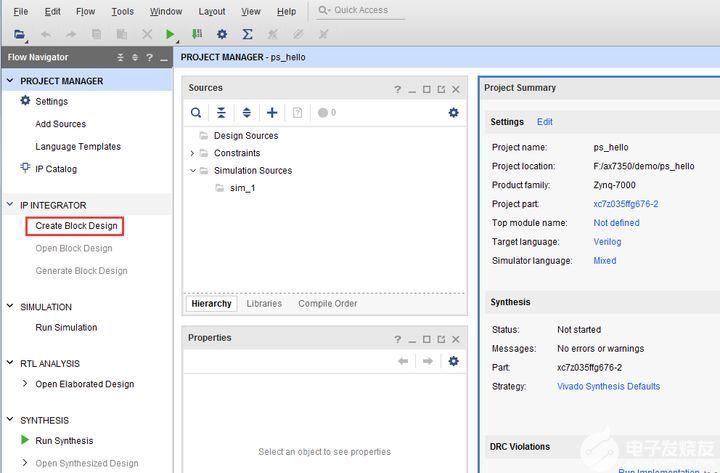

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十八章 Hello World(上)

我們從原理圖中可以看到ZYNQ芯片分為PL和PS,PS端的IO分配相對是固定的,不能任意分配,而且不需要在Vivado軟件里分配管腳,雖然本實驗僅僅使用...

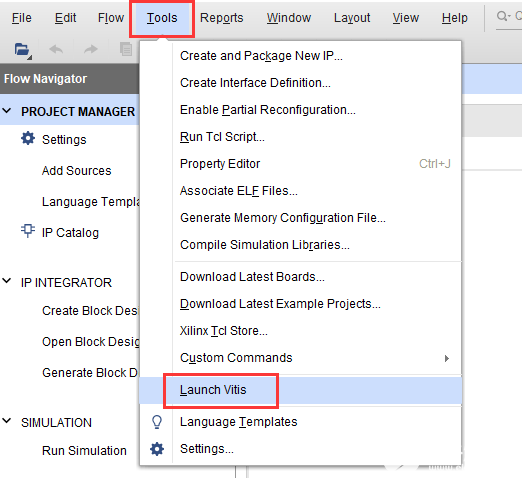

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十七章Vitis準備工程及注意事項

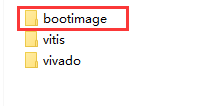

所有的工程目錄下都有個bootimage文件夾,存放了對應的BOOT.bin文件,可將此文件拷貝到Vitis_image_download文件夾,覆蓋原...

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十六章7寸液晶屏顯示實驗

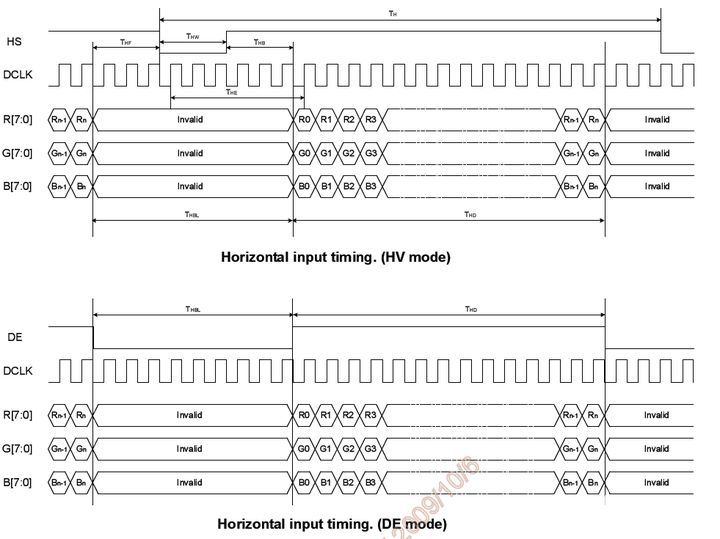

LCD屏顯示方式從屏幕左上角一點開始,從左向右逐點顯示,每顯示完一行,再回到屏幕的左邊下一行的起始位置,在這期間,需要對行進行消隱,每行結束時,用行同步...

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十五章HDMI字符顯示實驗

在HDMI輸出實驗中講解了HDMI顯示原理和顯示方式,本實驗介紹如何使用FPGA實現字符顯示,通過這個實驗更加深入的了解HDMI的顯示方式。

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十四章HDMI輸出實驗

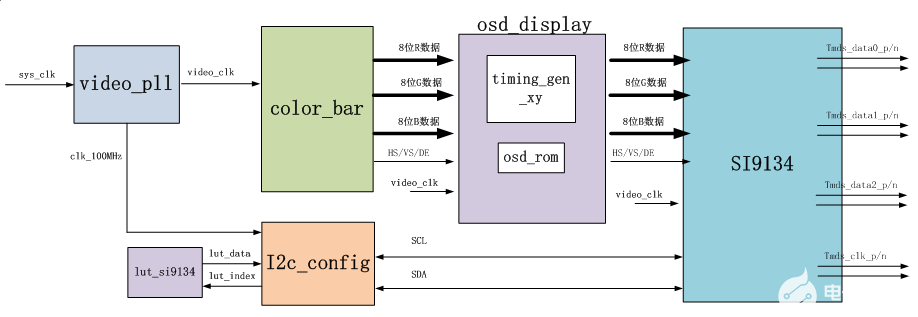

由于開發板上只有DP可以顯示,但卻是PS端的,PL端沒有HDMI的接口,因此我們采用AN9134的HDMI擴展模塊實現HDMI顯示。將24位RGB編碼輸...

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十三章RS485實驗

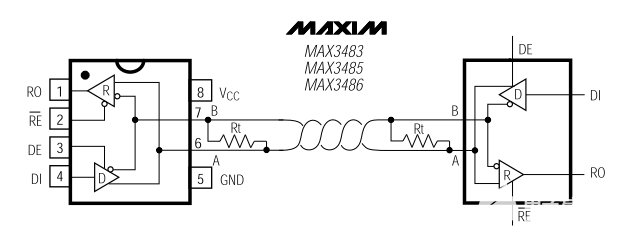

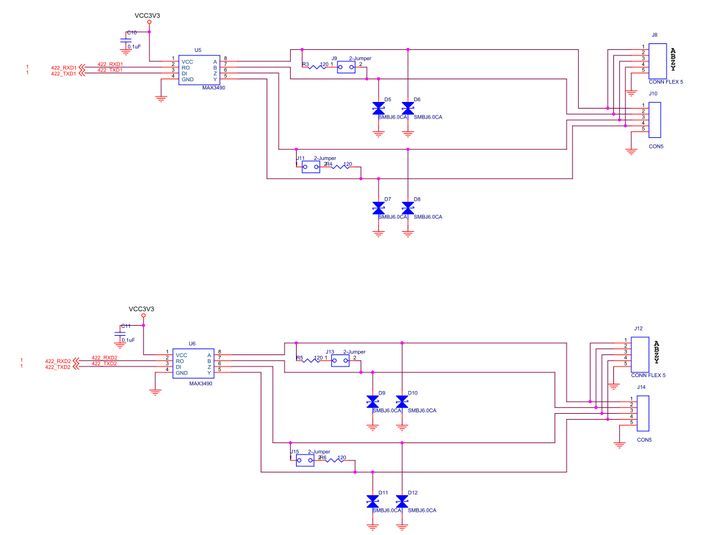

RS485與RS422類似,也是采用差分信號傳輸,但RS485是半雙工傳輸,也就是說,同一時刻只能有一個方向的數據傳輸。而且接口也比RS422少,只有差...

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十二章RS422實驗

本章利用AN3485模塊實現RS422接口數據傳輸。關于模塊,在前面的RS232實驗中已經介紹過,本實驗不再贅述。RS422與RS232在與FPGA的連...

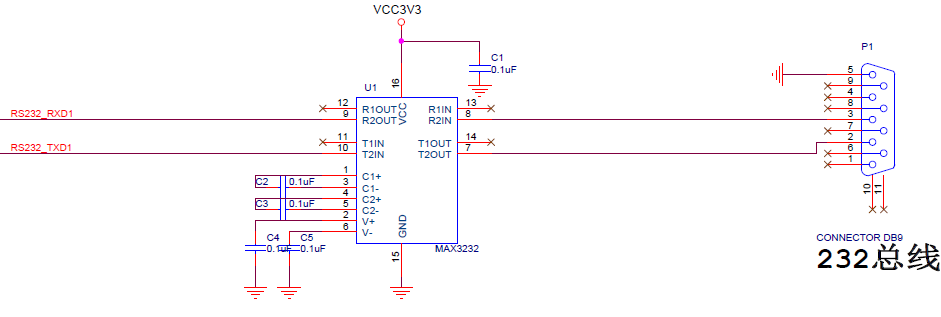

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十一章RS232實驗

AN3485模塊的RS232接口采用MAX3232芯片實現RS232和+3.3V TTL電平的轉換。TTL電平的串口接收和發送信號(RXD, TXD)連...

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十章PWM呼吸燈實驗

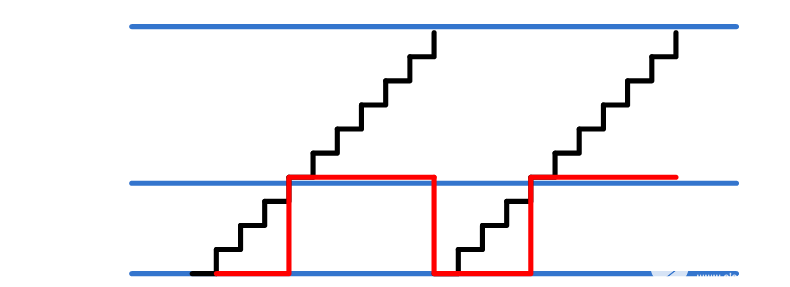

用一個N比特的計數器,最大值可以表示為2的N次方,最小值0,計數器以“period”為步進值累加,加到最大值后會溢出,進入下一個累加周期。當計數器值大于...

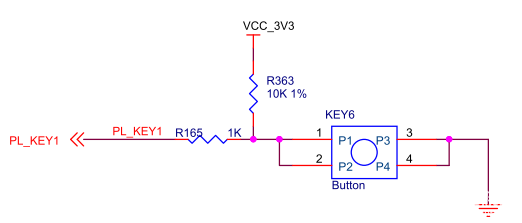

【ZYNQ Ultrascale+ MPSOC FPGA教程】第九章Vivado下按鍵實驗

按鍵是FPGA設計當中最常用也是最簡單的外設,本章通過按鍵檢測實驗,檢測開發板的按鍵功能是否正常,并了解硬件描述語言和FPGA的具體關系,學習Vivad...

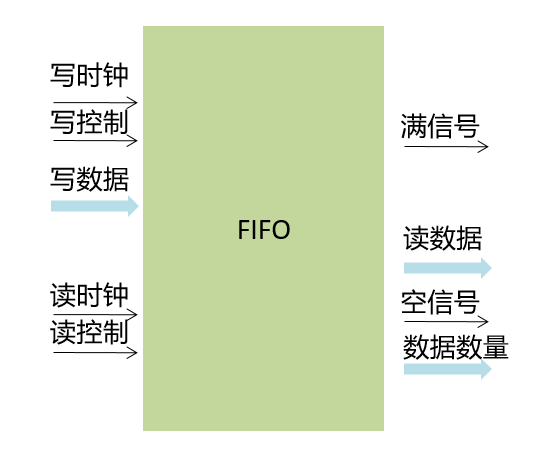

【ZYNQ Ultrascale+ MPSOC FPGA教程】第八章FPGA片內FIFO讀寫測試實驗

FIFO: First in, First out代表先進的數據先出,后進的數據后出。Xilinx在VIVADO里為我們已經提供了FIFO的IP核, 我...

【ZYNQ Ultrascale+ MPSOC FPGA教程】第七章FPGA片內ROM測試實驗

既然是ROM,那么我們就必須提前給它準備好數據,然后在FPGA實際運行時,我們直接讀取這些ROM中預存儲好的數據就行。Xilinx FPGA的片內ROM...

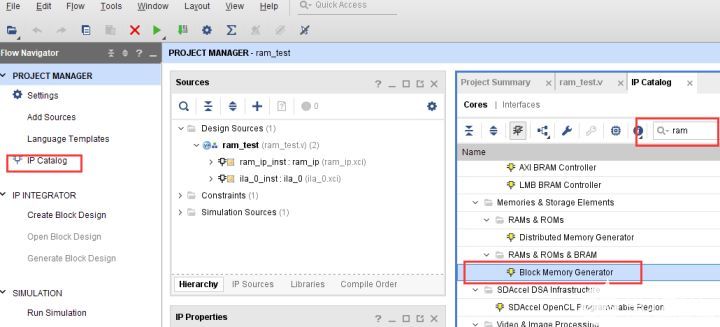

【ZYNQ Ultrascale+ MPSOC FPGA教程】第六章FPGA片內RAM讀寫測試實驗

RAM是FPGA中常用的基礎模塊,可廣泛用于緩存數據的情況,同樣它也是ROM,FIFO的基礎。本實驗將為大家介紹如何使用FPGA內部的RAM以及程序對該...

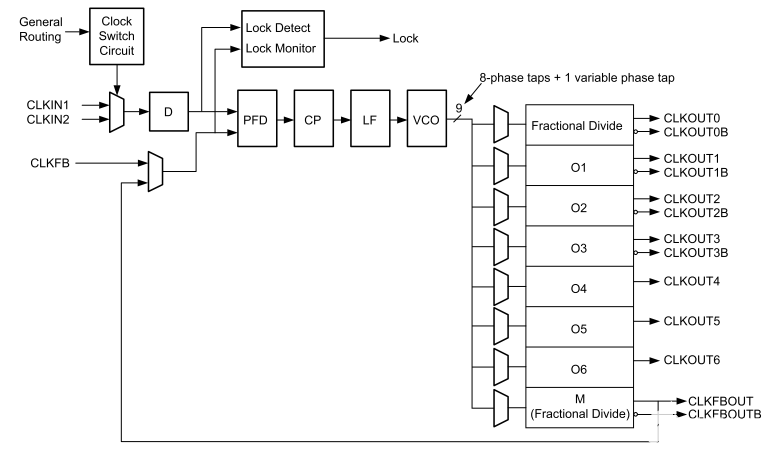

【ZYNQ Ultrascale+ MPSOC FPGA教程】第五章Vivado下PLL實驗

PLL(phase-locked loop),即鎖相環。是FPGA中的重要資源。由于一個復雜的FPGA系統往往需要多個不同頻率,相位的時鐘信號。所以,一...

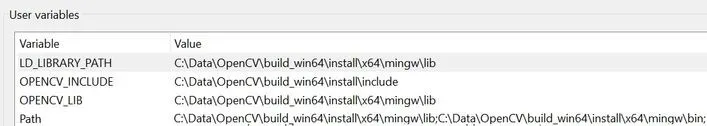

Vitis HLS工具在Standalone模式下調用Xilinx Vision Library L1 API例程

在論壇上遇到在高層次綜合工具中調用視覺庫遇到的大多數問題都和 opencv 庫以及Xilinx Vision 庫的安裝路徑有關,如今 Vitis HLS...

換一批

換一批

編輯推薦廠商產品技術軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯網 | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發電 | UPS | AR | 智能電網 | 國民技術 | Microchip |

| 開關電源 | 步進電機 | 無線充電 | LabVIEW | EMC | PLC | OLED | 單片機 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 藍牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太網 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 語音識別 | 萬用表 | CPLD | 耦合 | 電路仿真 | 電容濾波 | 保護電路 | 看門狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 閾值電壓 | UART | 機器學習 | TensorFlow |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |